一种用于PWM 控制Buck 型DC-DC 变换器的带隙基准源

2013-12-21王宇星

王宇星 ,朱 波

在DC-DC 转换器芯片设计中,误差放大器的参考电压和其他模块需要的参考电流由带隙基准产生,可见基准的精度会直接影响到芯片的控制精度[1]。在众多的基准实现电路中,带隙基准(BGR)电路的研究最为广泛[2-5]。就进行补偿和具有正负温度系数的电学量而言,可以分为电流模式带隙电压基准源和电压模式带隙电压基准源。为提高电压基准综合性能水平,需将电流模与电压模结构的优点充分结合。因此,具有负载驱动能力的电压模Widlar 带隙基准结构[6],成为实现精度基准的理想结构选择。

电路基于经典的Wildar 电压基准环路控制系统分析的基础上,通过高阶补偿完成系统分析和研究,进行仿真验证和版图设计,最后给出流片测试结果。

1 Widler 带隙基准基本原理

Widlar 基准源[6]基本原理与电压模基准相同,不同之处表现为系统反馈环路控制不仅实现的支路电流匹配的条件,同时通过负反馈控制稳定系统工作点,提高输出负载的电流驱动能力和系统的PSRR 特性。图1 所示的基于BJT 结构的Widlar 基准电路。Q3反向放大器构成系统闭环负反馈控制环路,利用其VBE 电压的箝位作用实现R1与R2支路电流相等,并在R3电阻上形成PTAT 电压定义的电流并传递到R1中,在R1和Q1串联支路中最终形成电压模基准输出。反馈控制调节管Q4基极电位提供基准及负载支路所需电流,维持输出不变,并且输出电压由电压模基准支路定义。

图1 基于BJT 的Widler 型电压基准

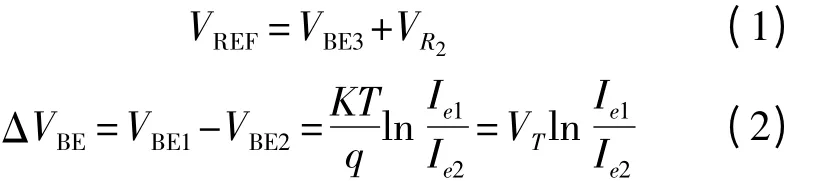

Widler 型电压基准的基准电压从Q3的集电极引出,其表达式为:

从电路上看,ΔVBE是电阻R3上的压降,ΔVBE=R3·Ie2。如果晶体管的β 值很高,可以忽略Iβ 的影响,则Ie2=Ic2,VR3=R2·Ic2=R2/R3·ΔVBE。

将VR2代入表达式(1)得:

在电路上,电路中R1和R2近似相等,都等于VREF减去一个VBE,所以Ie1/Ie2=Ic1/Ic2=R2/R1代入式(3)得

得到Widler 带隙基准电压表达式。式中第一项具有负的温度系数,第二项具有正的温度系数,适当地选择电阻比值,可以使正、负温度系数互相抵消,从而实现零温度漂移。

这种结构的缺点就是电源电压比较高,提高PSRR 性能的关键,可通过增益调节的反馈环路控制实现环路稳定,提高源跟随缓冲器基极或栅极电位的动态调节能力,同时实现支路电流匹配。

2 电路实现

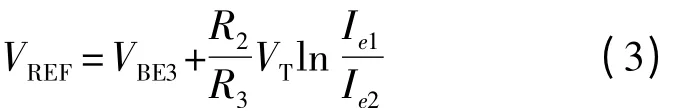

图2 所示为基于Widler 型电压基准基本原理设计的应用于BUCK 型DC-DC 转换器的带隙基准电路。

其中Q1、Q2、R1、R2、R3是带隙基准电路的核心部分。Q1、Q2是采用1 ∶8的NPN 管,R1、R2和R3采用相同类型电阻;Q3、R4构成高温段二阶温度补偿电路。基准输出电压表达式为:

由于R1、R2和R3采用相同类型电阻,式(5)第二项是PTAT 电压,由三极管理论知,VBE1具有负的温度系数,是温度的复杂高阶函数,对于简单一阶补偿的带隙基准,Vref与T 的关系曲线向上凸,极值点出现在300 K 附近,在高温阶段Vref随温度升高逐渐降低。由于三极管的VBE的值随温度升高而减小,当温度较低时,Q3的VBE值较高,大于电阻R2两端电压VR2,Q3截止,不消耗电流;当温度升高到一定值时,VBE,Q3小于VR2,Q3导通,向电阻R3注入一路电流,使得R3的等效阻值增大,Vref值增加,Vref-T 曲线趋近平坦,起到高温段补偿作用。调节电阻R4的值,当R4增大,IQ3减小,补偿作用减弱,Vref高温段曲线降低;当R4减小,IQ3增大,补偿作用增强,Vref高温段曲线升高,但是R4阻值的大小并不影响Q3导通的温度点。考虑补偿VBE(T)二阶项后,输出基准电压为:

图2 高阶补偿带隙基准电路

三极管Q3和带隙核心主电路构成负反馈环路,以保证系统工作稳定性。

偏置电流由基准电压经过一个VBE的压降后除以电阻得到,表达式如下:

由此式可看到分子呈现正温度系数,而R4、R5是为后面的OTP 电路产生偏置电流,R4、R5是高阻的PLOY 电阻,其为负温度系数的电阻,则整个电流呈现了正温效应。实际电路中QS2会提供另外一路电流,但因为此电流值与上式相比,可以忽略。另外经过此偏置电流镜像为后续模块提供的一般均为OP、比较器的偏置电流,其绝对值要求并不高,因此采用此种设计。

3 仿真结果与分析

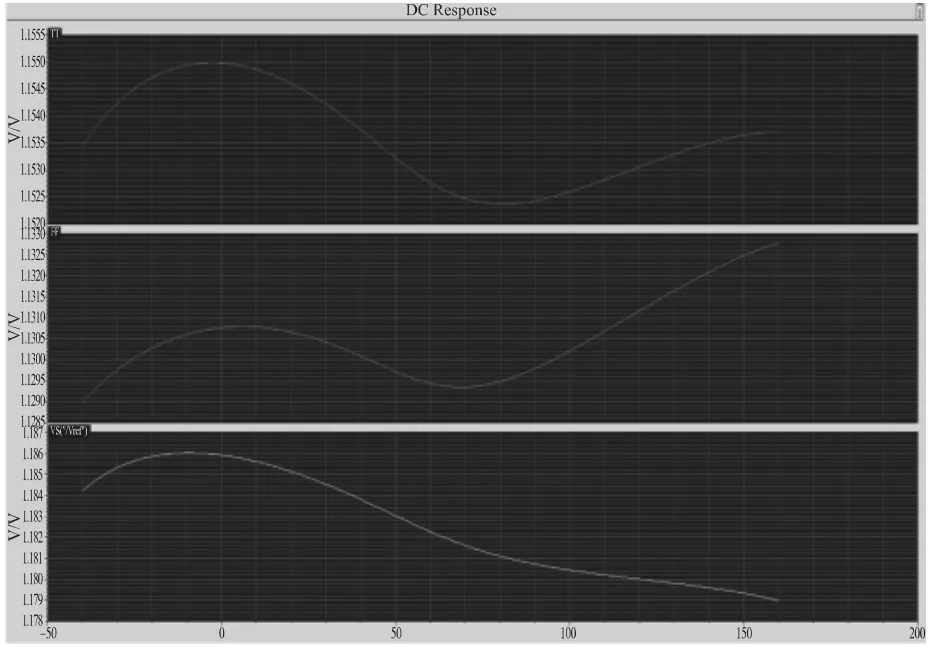

本电路运用Cadence Spectre 工具和BD 0. 35 μm BCD 工艺,在-40 ℃~160 ℃温度范围条件下进行仿真。

电源电压上电后,电路完成启动,输出基准电压稳定在1.25 V。图3 给出了高阶补偿后bandgap 在TT/SS/FF Corner 下温度从-40 ℃~160 ℃的扫描结果。由图可知,在tt 模型下,最小值和最大值之间差为12.5 mV 左右,主要是低温时效果欠佳,从-25 ℃到160 ℃的温度系数是22×10-6/℃左右,从-40 ℃到160 ℃温度系数是65×10-6/℃左右。

图3 基准在TT/SS/FF Corner 下温度曲线

从图3 可以看出,输出的参考电压具有二阶温度补偿效果,而且单个Corner 下电压随温度的漂移尚可。但是3 个Corner 比较可以发现SS 和FF 下的温度变化在54 mV。这时,参考电压0.923 V 的变化范围大约在40 mV 左右。

图4 所示,电源电压从7.5V ~18V 的变化范围内,基准输出变化了0.03 mV/V,可以看出基准源有良好的电源电压稳定性。

图5 所示是高阶补偿后电源电压为4.75 V 的Vref在TT/SS/FF Corner 的电源抑制比仿真结果,扫描范围从100 Hz ~10 MHz,TT 模型下,低频的时候电源抑制比在-57.37 dB,高频的时候电源抑制比在-30 dB,3 个Corner 比较差异不大。基准在整个工作过程中有很高的电源抑制比。

图4 输出电压随电源电压的变化曲线

图5 基准电源在TT/SS/FF Corner 下抑制比仿真曲线

4 版图与测试

4.1 版图设计

带隙基准在整个电路中是非常关键的模块,它是否能正常工作,直接影响到整个芯片能否正常工作,而且输出电压的精度等指标是由带隙基准决定的,因此带隙基准设计时不仅要考虑电路原理图,版图的设计也非常重要。此模块对匹配程度要求比较高,寄生的PNP 管要求高度匹配以保证低失调。该基准电路版图见图6 所示。

图6 带隙基准的版图

4.2 测试与分析

测试工具:稳压源、示波器、电感电流测试仪、万用表。如图7 所示,当VIN=12 V,EN=3 V,COMP与FB 短接,即可测量FB 点基准电压,即电阻分压V0.9 处电压。

图7 基准测试原理图

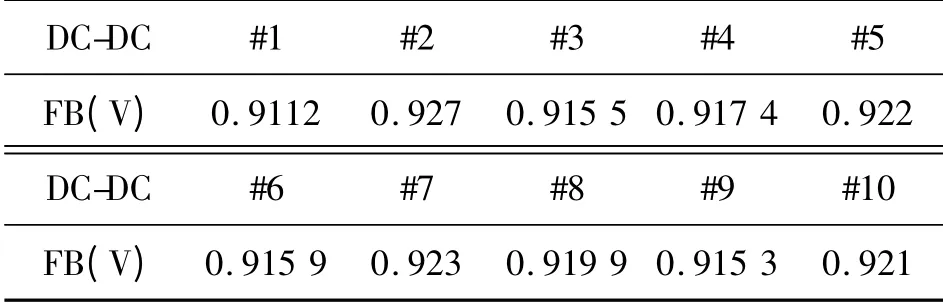

表1 基准常温实测结果

从图8 可知,基准随温度呈负温状态,随温度的上升,基准会变小,常温下,基准输出电压的值约为0.917 左右,与设计值相仿。

图8 基准随温度测试曲线

5 结束语

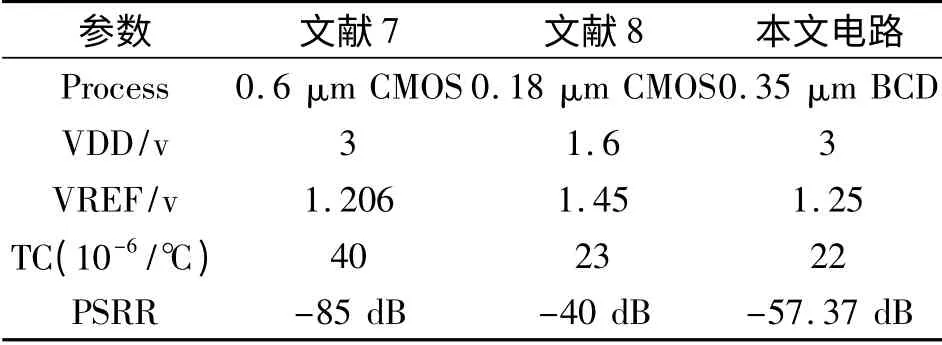

本文电路利用运用Cadence 工具和BD 0. 35 μm BCD 工艺设计了一种应用于DC-DC 转换器专用芯片的带隙基准电路。从表2 本文电路与文献[7]和文献[8]电路模拟仿真性能比较,本电路精度高、结构简单占用芯片面积小。如进一步优化高价补偿,可进一步提高TC 性能。芯片流片后的测试结果满足设计要求,已大量应用于实际产品中。

表2 基准源性能比较

[1] 谢芳,戴庆元. 一种新型CMOS 集成降压源IP 模块的设计[J].电子器件,2009,6(9):1027-1030.

[2] Piero Malcovati,Franco Maloberti,Carlo Fiocchi,et al. Curvature-Compensate BiCMOS Bandgap with 1 V Supply Voltage[J].IEEE Journal of Solid-State Circuit,2001,36:1076-1081.

[3] Paul R Gray,Paul J Hurst,Stephen H Lewis,et al.模拟集成电路的分析与设计[M].北京:高等教育出版社,2005:284-310.

[4] Kem iMoniwa A,Suneo Terasawa T,Kyoji Nakio,et al. Heuristic Method for Phase“Conflict Minimization in Automatic Phase”Shift Mask Design[J].JPN J Appl Phys,1995,34:6584-6589.

[5] Tham K M,Nagaraj K.A Low Supply Voltage High PSRR Voltage Reference in CMOS Process[J]. IEEE J Solid-State Circuits,1995,30(5):586-590.

[6] Widlar R J. New Developments in IC Voltage Regulators[J].ISSCC,1971,6(1):2-7.

[7] 应建华,陈嘉,王洁.低功耗、高电源抑制比基准电压源的设计[J].半导体学报,2007,28(6):975-978.

[8] Xing Xinpen,Li Dongmei,Wang Zhihual. A Novel CMOS Current Mode Bandgap Reference[J].半导体学报,2008,7(29):1249-1253.