一种通用雷达信号处理系统的硬件设计

2013-12-17李小娟全英汇

周 杰,李小娟,张 伟,全英汇

(1.中国电子科技集团第20研究所雷达事业部,陕西西安 710068;2.西安电子科技大学雷达信号处理国家重点实验室,陕西西安 710071)

随着雷达技术的发展,信号处理的复杂度和运算量大幅增加,对雷达信号处理系统的要求也越来越高。一个完备、复杂的雷达信号处理系统通常包括[1]:信号采集、数据存储、控制、运算、通信、电源和电磁兼容与屏蔽系统。本文介绍了一种以高速AD+高性能FPGA+DSP为核心,兼顾大容量数据存储的通用化雷达信号处理硬件平台,系统集成度高,结构灵活,对算法的适应性强,具有较好的通用性和可扩展性。

1 通用雷达信号处理系统组成

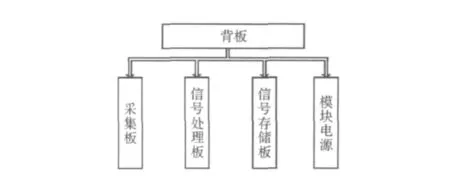

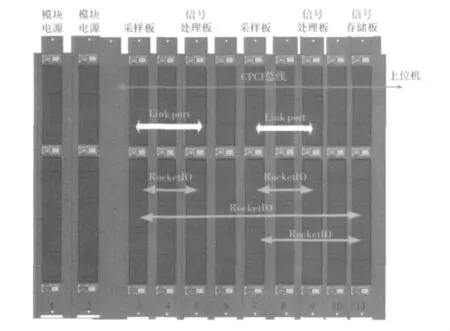

系统由采样板、信号处理板、存储板、背板、电源及机箱组成,其基本结构如图1所示。在本系统中,采样板完成数据采集、数字下变频及脉冲压缩处理。信号处理板完成搜索、跟踪和抗干扰等实时运算。信号存储板依靠板载Flash阵列完成数据存储,方便以后仿真分析及非实时处理。各板上均放置FPGA负责实时控制。背板自定义,采用CPCI总线进行状态控制和处理结果反馈,板间通讯通过Rocket IO接口以及Link Port接口两种形式[1]。

图1 雷达信号处理系统基本框图

2 通用雷达信号处理系统硬件设计

2.1 采样板的硬件设计

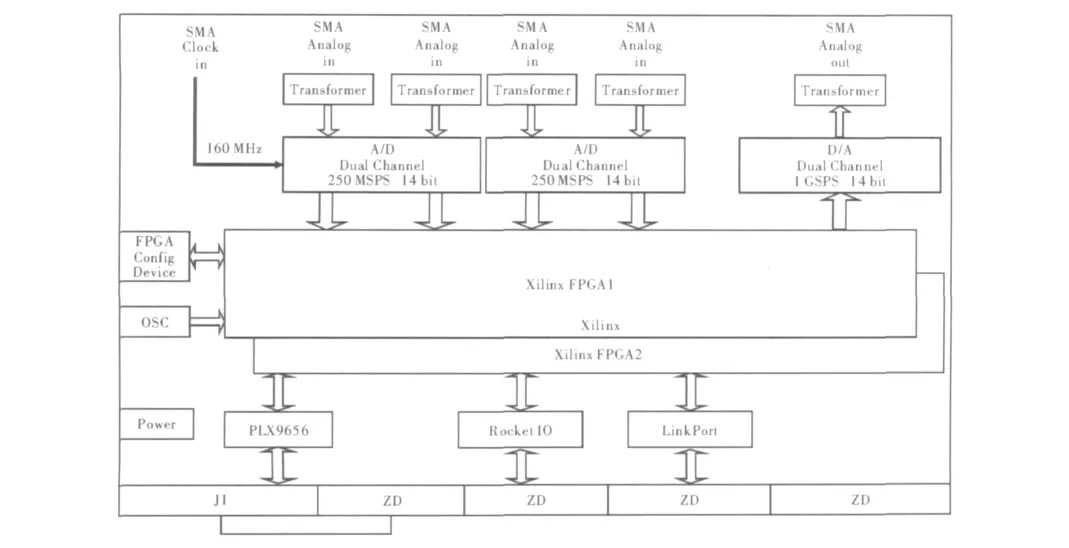

采样板共有4路模拟信号输入通道和一路模拟信号输出通道,两片双通道ADC,FPGA1作为主处理芯片,FPGA2作为从处理芯片[2]。两片 FPGA之间用LVDS通信,板卡框图如图2所示。

ADC采用ADI公司的AD9643,该芯片是双通道ADC,最大采样率250 Msample·s-1,采样精度14 位,模拟信号输入最大2Vpp,可以通过SPI接口对芯片进行控制。采用两片65 nm工艺的Xilinx Virtex-5作为核心处理器,其中一片作为备用,FPGA同时兼容LX110T和SX95T[3]。前者逻辑资源多,后者则更适于信号处理,于是采用后者作为核心控制芯片。

图2 采集板基本电路框图

采样板接收前端送来的4路中频模拟信号,将信号经过4路A/D进行模数转换,A/D的时钟由外部供给。A/D输出的14位数字信号经过LVDS传输给FPGA1,FPGA1对该数字信号进行数字下变频以及脉冲压缩处理。如果运算量大,FPGA1处理后的数据可通过两片FPGA之间的 LVDS传输线传输到FPGA2中。FPGA1同时可以将处理后的数据传给D/A,经过数模转换后将输出信号传输给显控器进行状态监测。两片FPGA中的数据均可通过高速串口或链路口传输给信号处理板。板上FPGA1通过CPCI接口接收上位机的指令控制采样板的工作状态。CPCI总线的工作频率为33 MHz或66 MHz,数据宽度为32或64位,总线带宽最高为66×64/8=528 MB/s。

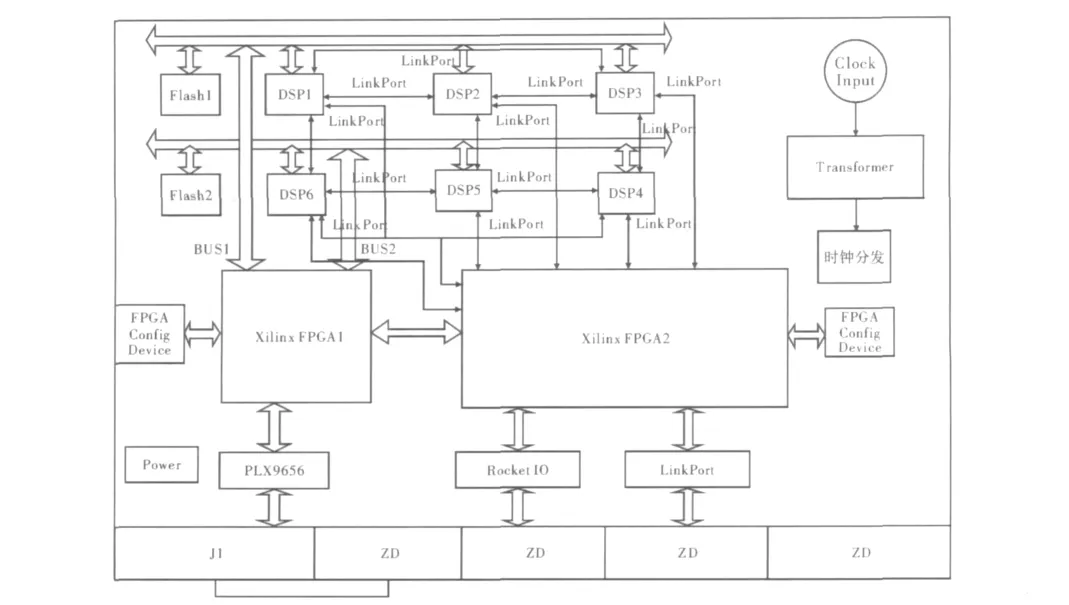

2.2 信号处理板的硬件设计

信号处理板的主要硬件包括2片FPGA和6片DSP。6片DSP分成两组,3片一组,共享数据总线,接入FPGA1以获取数据;6片DSP,两两互联,用链路口串成环形,均连接到 FPGA2,用于交换数据[4]。图3给出了信号处理板基本电路框图。

图3 信号处理板基本电路框图

与采样板相同,板上FPGA1通过CPCI接口接收上位机的指令控制信号处理板的工作状态,通过数据总线分发给6片DSP。板上FPGA2可通过Rockit IO接口以及Link Port接口接收采样板送来的数据,通过链路口分发给6片DSP。6片DSP是信号处理板实时运算的核心,考虑到成像、跟踪、搜索、抗干扰等多种应用需求,设计时以大容量处理、快速数据交换、可灵活选择为原则,每片DSP外挂大容量SDRAM,64位并行数据总线,链路口连接完备,从而满足不同需求。例如,某跟踪雷达在用此信号处理板时,仅选择一组3片DSP,某成像雷达在用此信号处理板时,板上资源全部保留。

信号处理板与采样板之间可通过Rocket IO进行高速串行数据传输,设计有4个lane。每个lane的速率为3.125 Gbit·s-1,若采用 4lane 进行传输,最高数据率达 DRocketIO=3.125 Gbit·s-1×4 lane≈1.5 GB·s-1。也可通过Link Port接口进行数据传输,每个链路口的可靠传输率约为100 MB·s-1,设计有2个链路口,共200 MB·s-1。

2.3 存储板的硬件设计

存储板是数据存储的载体,以大容量NAND Flash芯片存储阵列为存储介质,设计每块存储板容量为1 TB,持续写入速度 >1 GB·s-1。为通用化考虑,存储板设计多种总线接口,包括CPCI 66 bit/66 MHz、背板Rocket IO接口10路、千兆以太网接口等。其中CPCI接口和背板Rocket IO接口在背板上走线;千兆以太网接口在存储板的前面板[5]。存储板电路原理框图如图4所示。

图4 信号处理板基本电路框图

存储板与采样板之间采用Rocket IO进行高速串行数据传输,设计有8lane。每个lane速率为3.125 Gbit·s-1,若采用8lane进行传输,最高数据率可达3 GB·s-1。

2.4 背板及模块电源的设计

系统为一个自定义的高速互连系统,根据需求,某跟踪雷达使用了1块信号处理板,1块采样板,1块数据存储板和1块电源模块。某成像雷达使用了2块信号处理板,2块采样板,1块数据存储板和2块电源模块。某成像雷达信号处理系统背板定义如图5所示。

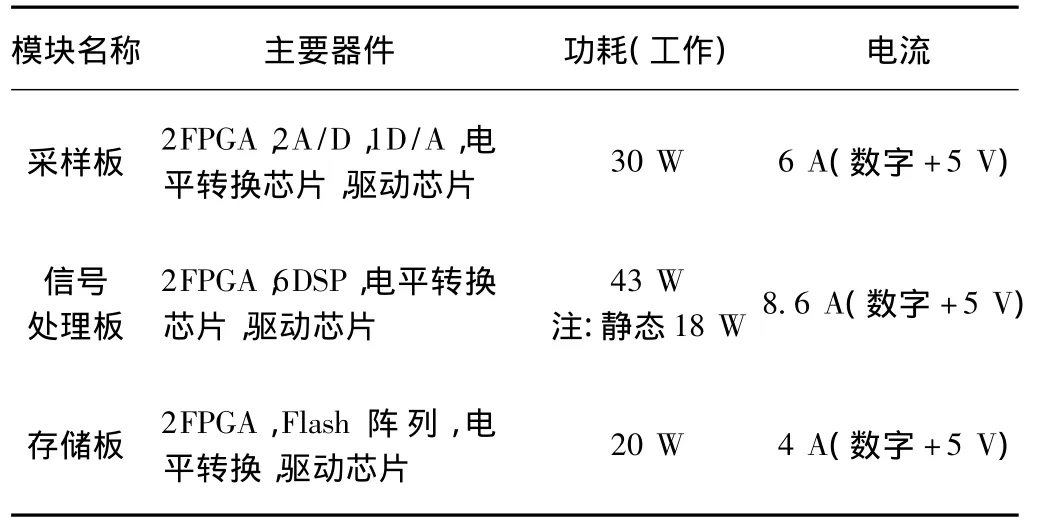

表1 信号处理系统各模块功耗估算

图5 某成像雷达信号处理系统背板定义

模块设计时,尽量统一电源种类,可提高系统的适用性。根据不同应用需求,确定板卡种类及数目,计算出信号处理系统的总功耗,留出一定的裕度,确定模块电源总功耗,或为采样板提供一路独立的线性电源,更好地保证ADC的性能。

3 结束语

以雷达信号处理设计为背景,将信号处理划分为若干个模块,结合通用化应用需求,对每个模块的硬件设计进行了研究。利用CPCI接口保证了系统间通讯的可靠性和易用性,利用高速串口克服了板件通讯数据率低的问题,利用Flash阵列解决了实时大容量数据存储问题,实现了通用雷达信号处理平台。由于模块化设计研制周期短、可重构性好、对处理算法适应性强,目前该通用雷达信号处理系统已在成像、跟踪、探测雷达上获得应用。

[1]苏涛,何学辉,吕林夏.实时信号处理系统设计[M].西安:西安电子科技大学出版社,2006.

[2]杨剑,张月,陈曾平.数字化雷达通用信号处理机设计[J].电路与系统学报,2009(4):55 -59.

[3]刘书明,苏涛,罗军辉.TigerSHARC DSP应用系统设计[M].北京:电子工业出版社,2004.

[4]刘伟,李海,曾涛.面向对象通用雷达信号处理程序框架的设计与实现[J].北京理工大学学报,2004(8):731-734.

[5]王倩,李燕,王虹现,等.基于高速数模转换器的通用雷达信号模拟器的设计[J].电子科技,2008(1):25-28.