IEEE 802.11p物理层 OFDM 调制器的设计

2013-12-14张家波刘兴迪

张家波,刘兴迪,杨 庆

(重庆邮电大学移动通信技术重点实验室,重庆400065)

0 引言

近年来,汽车产业得到了快速发展,在它给人们的交通带来方便的同时也显现出了一些问题,例如交通安全和交通堵塞等。基于无线通信技术的车联网技术为解决这些问题提供了有效途径。车联网系统主要是指车与车(vehicle-to-vehicle,V2V)以及车与路面基础设施(vehicle-to-infrastructure,V2I)之间的无线通信,它可以大大提高交通的安全性。以后车联网会有更多的应用,例如,对实时数据的交通管理以及使车辆对交通拥塞快速地做出反应等。

车联网是基于IEEE 802.11p无线局域网标准的。802.11p 标准是由 802.11a 扩充而来[1-2],针对其高速移动的使用环境对802.11a的物理层和MAC(media access control)层做了很多修改。802.11p物理层的核心技术仍然是使用OFDM(orthogonal frequency division multiplexing)调制技术。

本文在研究802.11p的物理层参数的基础上,提出了其OFDM发送端基带设计的总体框架和详细流程。使用Verilog HDL硬件描述语言,在Quar-tusⅡ开发环境中设计综合和验证,结果证明该设计符合802.11p的要求。

1 802.11p 物理层参数

802.11p在物理层上对802.11a上的修改主要是将工作频带变为5.850~5.925 GHz,75 MHz被划分为7个10 MHz的信道,频率最低的5 MHz作安全空白。其中,一个信道作为控制信道,而其他6个作为服务信道。这样,信号的带宽由802.11a的20 MHz变为10 MHz,物理层的参数在时域上变为802.11a的2倍[3]。信号带宽的减小可以降低多普勒扩展的影响,保护间隔的增大可以减小多径效应引起的码间干扰。802.11p物理层的主要参数如表1所示[4]。

表1 802.11p物理层的主要参数Tab.1 Main characteristic values of IEEE 802.11P

从表1可以看出,802.11p的调制方式,编码方式以及帧的结构与802.11a都非常相似,只是与时间有关的参数变为802.11a的2倍,相应数据速率变为802.11a的一半。数据速率由调制方式和编码效率决定,三者对应关系可以参考文献[3]。

2 802.11p基带调制器设计

2.1 系统总体设计

802.11p的物理层协议数据单元(physical protocol data unit,PPDU)帧结构主要包括3部分,即训练序列;SIGNAL域和DATA域。其中,训练序列包括10个重复的短训练序列和2个重复的长训练序列;SIGNAL域主要包含数据长度和数据速率的信息;而DATA域中的PSDU是MAC层所要传输的数据,这部分数据才是有效载荷数据[3]。

根据802.11p的物理层参数和帧结构,我们设计802.11p的发送端基带设计如图1所示。

基带数据处理流程可以分成3个部分并行处理,即训练符号生成模块;SIGNAL域符号和DATA域符号的形成过程。其中,训练符号是确定的数据,将其存储在ROM中,当SIGNAL域和DATA域符号形成后将其按照帧格式进行读出,与SIGNAL域和DATA域符号合并成完整的发送端数据帧。

2.2 关键模块设计

2.2.1 时钟生成模块

由于802.11p的信号带宽为10 MHz,因此,使用10 MHz时钟作为整个基带处理器的系统时钟(SYS_CLK)。对于DATA域而言,由于该设计采用的是16QAM调制,因此,星座映射模块输入端的时钟为40 MHz(CB_CLK);编码效率为3/4,因此,在编码前数据输入时钟为30 MHz(DIN_CLK);MAC层送往物理层的数据为字节格式,因此,MAC层时钟大小为30 MHz/8=3.75 MHz(MAC_CLK)。对于SIGNAL域而言:由于调制使用的是BPSK调制,因此,映射模块输入端时钟为系统时钟,编码效率为1/2,因此,编码输入时钟为 5 MHz(SIG_CLK)[5]。

图1 802.11p发送端OFDM基带设计框图Fig.1 802.11p transmitter block diagram for the OFDM baseband

2.2.2 主控模块

主控模块MCU用来控制与协调子模块的工作,以保证整个处理器时序的精确同步,另外,还承担着与 MAC 层的握手[6]。

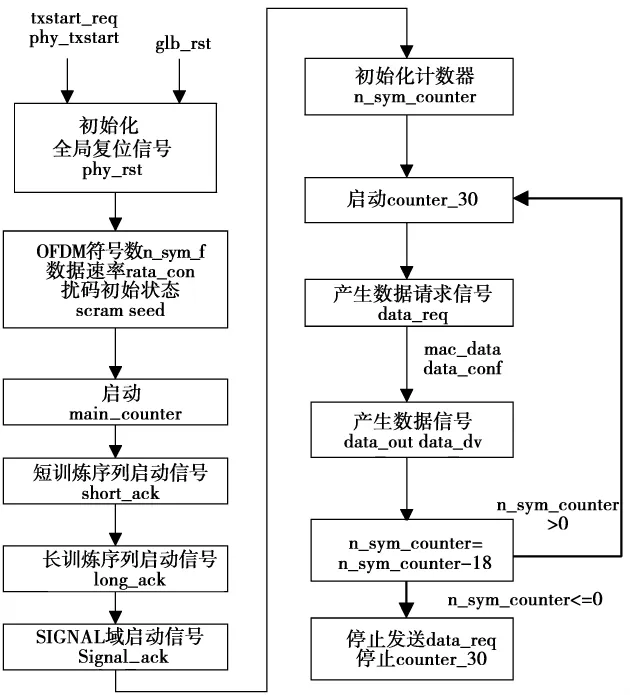

MCU的工作过程可以用状态机来描述,如图2所示。

图2 主控模块MCU状态机Fig.2 State machine of MCU block

系统启动时glb_rst为低电平,完成系统时钟模块和MCU中控制信号的复位。当MCU收到请求信号txstart_req后,发送复位信号phy_rst进行各个模块(除系统工作时钟和MCU模块外)的初始化。同时输入21 bits的phy_txstart信号,包含PSDU帧长,用length(12 bits)表示;数据速率 rate_con(6 bits)和发射功率(3 bits)。当MCU接收完phy-txstart信号后,将 length,rate_con及加扰模块初始化信号scram_seed送入相应模块输入端口。接下来启动主计数器 main_counter,按照要求的时序依次输出短训练序列启动信号short_ack,长训练序列启动信号long_ack和SIGNAL域启动信号signal_ack。

接下来MCU用一个模30的计数器来产生date_req信号,请求MAC层返回一个OFDM符号所需的18 Bytes数据,同时用计数器n_sym_counter(PSDU包含的字节数length)减去18。由于MAC层时钟为3.75 MHz,因此,OFDM 符号间隔正好为 8 μs。当计数器小于或等于0时,发送结束,请求信号data_req复位。

2.2.3 SIGNAL信号生成模块

当主控模块发出SIGNAL域启动信号signal_ack时,SIGNAL域首先经过SIG_BUFFER模块,生成24 bits的 SIGNAL域信号,包括 rate(4 bits)、length(12 bits)、保留位(1 bit)、奇偶校验位(1 bit)和尾比特(6 bits)。其中,rate和length分别表示主控模块发出的数据速率和数据长度。另外,此模块还实现了并串变换,形成24 bits数据以5 MHz时钟进行串行输出。

2.2.4 DATA域信号生成模块

本设计采用的是16QAM调制,编码效率为3/4[7],得到数据速率为18 Mbit/s,每个OFDM符号的数据为144 bits,即18 Bytes。在设计中,假设从MAC层传来100 Bytes的数据,这些数据存放在ROM里,在收到主控模块MCU发出的数据请求信号date_req之后,将数据输入确认信号(DATA_CONF)拉高18时钟,读取一个OFDM符号数据。

从ROM里读出的数据要按照帧结构,添加service字段、尾比特和填充比特以形成完整的DATA域数据。这一过程利用一个8位宽的双口RAM配合计数器来完成,将地址0和1里的8位数据填充0,作为16 bits的service字段[8]。然后,从地址2开始写入从ROM里读出的数据,一直到地址length+1(这里length为100),尾部填上6 bits的“0”当作尾比特位,后面添加42 bits的填充比特(PAD)位(全部为“0”)[9]。填充比特的计算公式为

NPAD=NDPS×(ceil(16+8×length+6)/NDPS)-(16+8×length+6)

上式中,ceil为取不小于该值的最小整数;NDPS为一个OFDM符号的数据比特数目,本设计为144。因此,经过组装后的DATA域数据为864 bits数据,共6个OFDM符号。

2.2.5 IFFT模块

在该设计中,IFFT是通过 Altera公司的 FFT V11.0 IP核来实现的,它与个人编写的IFFT模块相比,占用的资源更少,还可根据需求配置参数,提高了系统开发的灵活性。

在用IFFT核实现时,为了减小变换后的数据误差,要对IFFT输入数据进行适当放大。通过多次对IFFT IP核计算结果和MATLAB计算结果进行比较,最后,确定将IFFT模块输入数据放大比例确定为64倍。这可以在IFFT模块前通过乘法器左移6位实现。由于16QAM变换后的复数数据是8位,我们将IFFT核的输入和输出位数设为16位。

2.2.6 添加循环前缀模块

为了最大程度的消除符号干扰(inter symbol interference,ISI)和信道间干扰(inter channel interference,ICI),802.11p 规定符号间间隔为 1.6 μs,并在保护间隔内添加循环前缀。硬件实现时,将一个OFDM符号的前48个数据被存入RAM中,后16个数据一边存入RAM中,一边直接输出,然后,再将RAM 中的 64 个数据依次读出[10-12]。在实际实现时,使用2块宽度为16 bits,深度为64的RAM进行乒乓帧操作,当前一帧数据从第1个RAM输出时,后一帧数据存入第2个RAM,两者轮流进行读写操作,使数据实时连续处理,大大减少延时。

3 系统仿真与验证

在验证了设计中要用到的各个模块功能正确后,在QuartusⅡ11.0sp1软件开发环境中采用自顶向下的设计思想,依据图1来完成整个基于802.11p的OFDM基带系统设计。在设计中使用Verilog HDL硬件描述语言来完成各个模块的设计输入。硬件开发环境是 DE2-115开发板,FAGA芯片为ALTERA公司的CycloneⅣEP4CE115F29C7。

在设计时采用系统内部时钟50 MHz作为输入时钟,利用锁相环产生设计中所需要的各个时钟。并充分利用IP核里的现有模块,例如PLL,RAM,FIFO、计数器和IFFT等,以提高系统设计的简便可靠性,并缩短开发时间,节省硬件资源。

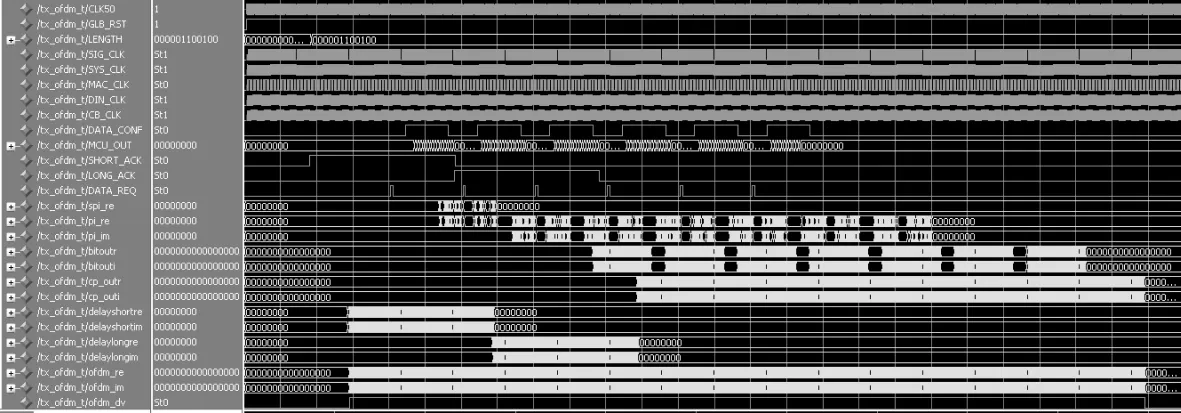

在对整个系统编译无误后,调用Mentor公司的Modelsim仿真软件进行功能仿真,仿真结果如图3所示。从图3中可以看出,帧的形成过程与我们设计的完全相符,SIGNAL域符号在插入导频后与DATA域的6个符号组装在一起,然后,进行IFFT变换及添加循环前缀操作。然后与延迟后的长短训练序列组装成帧。其中,ofdm_re为输出的OFDM符号的实部;ofdm_im为输出的OFDM符号的虚部;ofdm_dv为输出有效信号。

图3 基于802.11p的OFDM基带调制仿真图Fig.3 Simulation of IEEE 802.11P OFDM baseband

4 结束语

本文在研究802.11p标准的物理层参数以及帧结构的基础上,利用FPGA来设计整个OFDM基带调制系统。在设计中采用了自顶向下设计思想,并把系统划分为很多子模块,以提高系统的可靠性和可维护性。在设计中尽量使用现有的IP核来简化设计,提高设计进度,减少资源开销。通过仿真验证,该设计完全达到了802.11p标准所要求的功能。

[1]IEEE Computer Society.IEEE Std 802.11pTM-2010.IEEE Standard for Information technology—Telecommunications and information exchange between systems—Local and metropolitan area networks—Specific requirements—Part 11:Wireless LAN Medium Access Control(MAC)and Physical Layer(PHY)specifications—Amendment 6:Wireless Access in Vehicular Environments[S].New York,USA:IEEE,2010.

[2]IEEE Computer Society.IEEE Std 802.11a-1999.Sup-plement to IEEE Standard for Information technology—Telecommunications and information exchange between systems—Local and metropolitan area networks—Specific requirements—Part 11:Wireless LAN Medium Access Control(MAC)and Physical Layer(PHY)Specifications:High-speed Physical Layer in the 5 GHz Band[S].New York,USA:IEEE,1999.

[3]罗志锋,徐洪刚,何山.车路互联网的底层协议-802.11p标准[J]. 电子质量,2011(11):45-50.LUO Zhifeng,XU Honggang,HE Shan.802.11p Standard Specification for Telecommunications and Information Exchange Between Roadside and Vehicle Systems[J].Electronics Quality,2011(11):45-50.

[4]KIOKES G,ECONOMAKOS G,AMDITIS A,et al.Design and Implementation of an OFDM System for Vehicular Communications with FPGA Technologies[C]//2011 6th International Conference on Design&Technology of Integrated Systems in Nanoscale Era(DTIS).Athens:DTIS,2011:1-6.

[5]MIZANI M,RAKHMATOV D.Multi-Clock Pipeline Structure for 802.11a WLAN Transceiver[C]//IEEE International Symposium on Circuitsand Systems.Seattle WA:IEEE Press,2008:1580-1583.

[6]史治国,洪少华,陈抗生.基于XILINX FPGA的OFDM通信系统基带设计[M].杭州:浙江大学出版社,2009:1-99.SHI Zhiguo,HONG Shaohua,CHEN Kangsheng.Design of OFDM communication system Baseband Based on XILINX FPGA[M].Hangzhou:Zhe jiang University Press,2009:1-99.

[7]唐建明,孙小霞,徐位凯.基于编码的OFDM系统性能仿真[J].重庆邮电大学学报:自然科学版,2009,21(3):348-352.TANG Jianming,SUN Xiaoxia,XU Weikai.Performances simulation of coded OFDM systems[J].Journal of Chongqing University of Posts and Telecommunications:Natural Science Edition,2009,21(3):348-352.

[8]高仁璟,谭显松,王兢,等.高速802.16d OFDM基带系统研究与FPGA设计[J].重庆邮电大学学报:自然科学版,2010,22(4):411-415.GAO Renjing,TAN Xiansong,WANG Jing,et al.High speed OFDM baseband systems in 802.16d and its FPGA design[J].Journal of Chongqing University of Posts and Telecommunications:Natural Science Edition,2010,22(4):411-415.

[9]郭继经,李晓飞,张国栋.IEEE802.11a的OFDM基带调制的FPGA 实现[J].电视技术,2010,34(S1):90-93.GUO Jijing,LI Xiaofei,ZHANG Guodong.Implementation of OFDM Baseband of IEEE802.1la Based on FPGA[J].Video Engineering,2010,34(S1):90-93.

[10]崔丽珍,樊晓冬,刘乃君,等.基于FPGA的OFDM基带发送系统设计与实现[J].电视技术,2012,36(21):120-123.CUI Lizhen,FAN Xiaodong,LIU Naijun,et al.Design and Implementation of OFDM Baseband Sending System Based on FPGA[J].Video Engineering,2012,36(21):120-123.

[11]HECHRI A,ABDELLATIF M.FPGA Implementation of an OFDM Baseband Transmitter[C]//2011 International Conference on Communications,Computing and Control Applications(CCCA).Hammamet:CCCA,2011:1-4.

[12]刘松林,严家明,李超.基于 FPGA的 MIMO-OFDM基带系统发射机的设计[J].电子设计工程,2012,20(15):110-112.LIU Songlin,YAN Jiaming,LI Chao.Design of MIMOOFDM baseband system transmitter based on FPGA[J].Electronic Design Engineering,2012,20(15):110-112.