基于SOPC技术的脉冲多普勒引信信号处理器设计*

2013-12-10周军伟

周军伟,刘 斌

(中国空空导弹研究院,河南洛阳 471009)

0 引言

未来空战中电磁环境十分复杂且典型作战目标都具有高速、高机动的能力,从而导致最高弹目交会速度的提高和对应的弹目交会持续时间的缩短。为了完成对目标的精确探测识别和高效毁伤,引信信号处理就需要能够充分利用弹目交会信息提高引信的抗干扰能力并具有高速、灵活的信号处理能力[1]。

脉冲多普勒引信是一种在国内外多种型号空空导弹中广泛应用的无线电近炸引信体制。引信信号处理系统是引信的信息中枢,其具有收发系统时序控制、弹目交会信息处理、目标回波信号检测以及引信起爆控制等功能,它的结构和性能对于引信整体性能的优劣有着至关重要的影响。

目前MCU、DSP、FPGA是现代嵌入式系统中广泛应用的3种主要处理器,并且其各具特点,而SOPC技术可以将MCU、DSP、FPGA的优点完美结合,是嵌入式系统信号处理的一个重要发展方向。文中基于SOPC技术完成了脉冲多普勒引信信号处理系统设计,其具有高速、灵活的特点,能够有效提高引信的自适应能力和抗干扰能力。

1 SOPC技术简述

随着微电子技术的快速发展,传统的以微处理器和DSP为核心的嵌入式电子系统设计不断转向片上系统SOC(system on a chip)设计。SOC设计从整个系统性能要求出发,将微处理器、芯片结构、外围器件等各层次电路设计紧密结合起来,通过建立在全新理念上的系统硬件和系统软件的协同设计,在单个芯片上实现整个系统的功能[2]。

片上可编程系统SOPC(system on a programmable chip)是最早由Altera公司提出的一种灵活、高效的片上系统设计方案。SOPC与其他SOC设计技术相比,它的特点在于可编程性,也即它利用FPGA或CPLD器件的可编程性来进行SOC设计。根据在FPGA中使用的处理器IP类型的不同,SOPC基于FPGA的实现一般有两种形式,一种是在FPGA中嵌入微处理器的IP硬核,如 Altera的 Excalibur系列的 FPGA中植入了ARM922T嵌入式处理器,Xilinx的Virtex-II PRO系列的FPGA中植入了PowerPC405;另一种是在FPGA中嵌入微处理器的IP软核,如Altera提供了Nios II软核,Xilinx提供了 MicroBlaze软核[3]。相对硬核的SOPC实现形式,基于软核的SOPC实现方式更加灵活,可以完全根据实际系统的应用需求进行处理器硬件资源的剪裁,并可以选择实现多个处理器核,可以充分体现SOPC技术的特点。

Nios II嵌入式处理器是Altera公司于2004年6月推出的第二代用于可编程逻辑器件的可配置的软核处理器。它基于哈佛结构的RISC通用嵌入式处理器软核,能与用户逻辑相结合编程至Altera的FPGA中,性能超过200 DMIPS。文中以Nios II为嵌入式处理器,开展基于SOPC技术的脉冲多普勒引信信号处理系统设计。

2 基于SOPC技术的脉冲多普勒引信信号处理器硬件系统设计

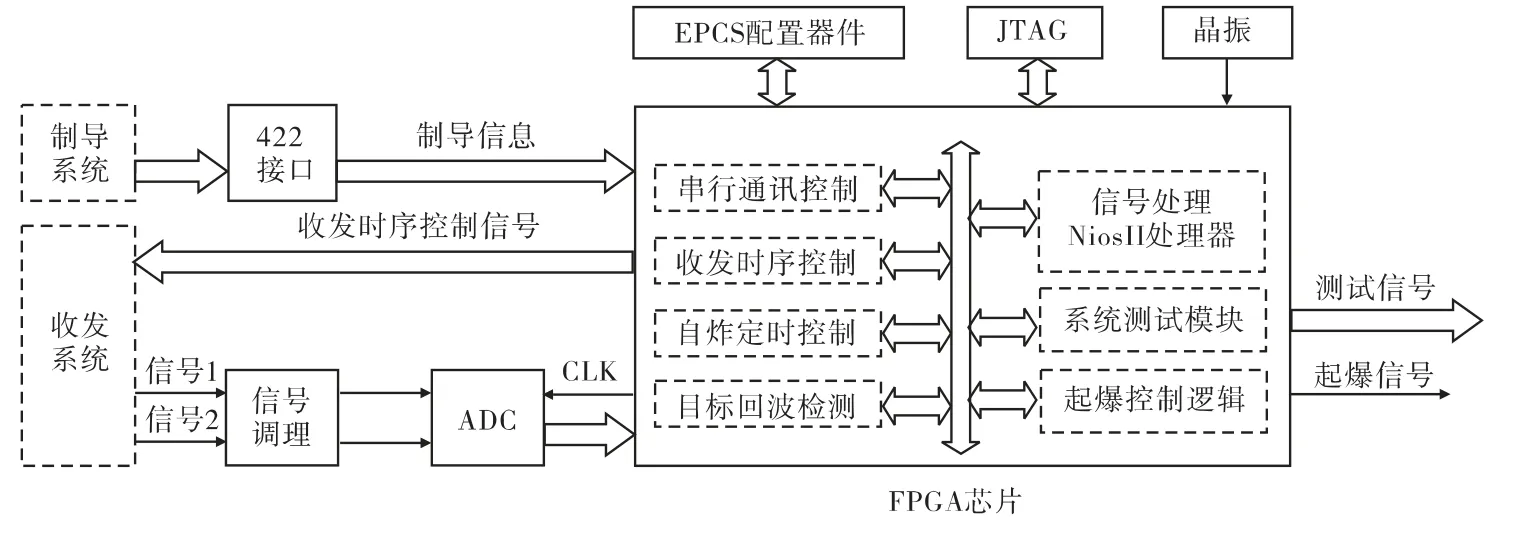

基于NiosII的脉冲多普勒引信信号处理系统的硬件电路设计如图1所示。由于采用SOPC技术能够充分利用系统资源提高了系统集成度,除了采样电路、422接口电路、配置电路、晶振以及电源等必需的外围器件以外,系统只需要一片大容量的 FPGA芯片。脉冲多普勒信号处理器的串行通讯、收发时序控制、自炸定时、目标回波检测、起爆控制等功能都在一片FPGA中利用SOPC技术编程实现。

图1 硬件系统组成原理简图

图2 基于SOPC技术的脉冲多普勒信息信号处理软件体系结构

从图1中可知,基于SOPC技术的脉冲多普勒引信信号处理器的硬件系统设计有如下特点:

●需要外部器件较少,硬件结构非常简洁,体积小可以满足弹上狭小空间的要求。

●处理能力具有可扩展性,通过选择大容量的FPGA芯片,可以方便的扩展系统处理能力。

●信号处理的主要功能通过软件设计实现,具有高速、灵活、易扩展的特性。

3 基于SOPC技术的脉冲多普勒引信信号处理器软件系统设计

3.1 脉冲多普勒引信信号处理器软件系统体系结构

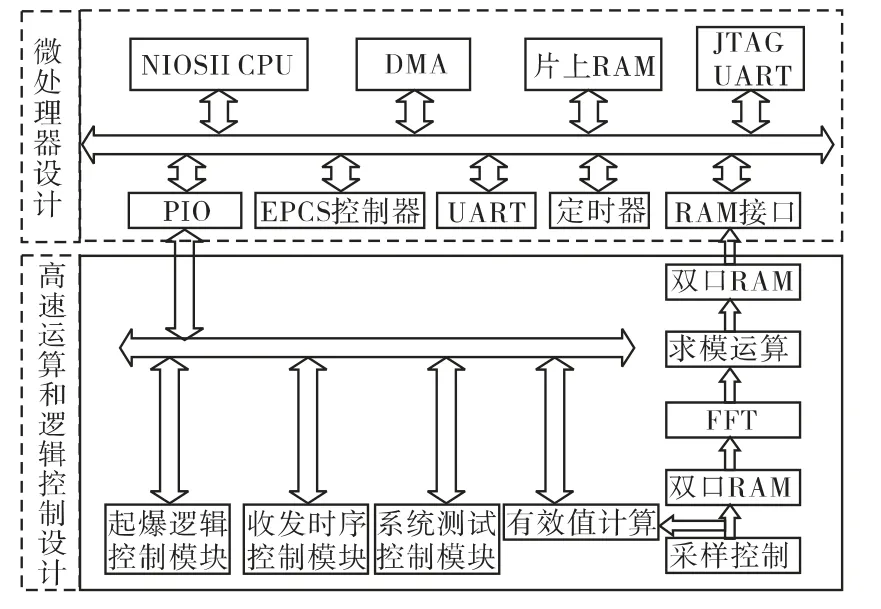

采用SOPC技术后,可以将脉冲多普勒引信信号处理功能进行分解、划分,并选择合理的软硬件实现方法。基于SOPC技术的脉冲多普勒引信信号处理器的软件设计体系结构如图2所示。

软件体系可以大致分为两个部分,一个部分是微处理器结构及运行软件设计,该部分主用于处理灵活的算法、实时性相对较弱的工作状态控制等内容,如自炸定时、目标恒虚警算法、串行通讯等,另一个部分为高速运算与逻辑控制设计,该部分主要用于实时性要求高、高速密集运算等部分内容,如起爆控制逻辑、收发时序、目标回波FFT变换等。

3.2 微处理器构建及运行软件设计

1)微处理器的构建

Altera公司提供的SOPC Builder为微控制器的开发设计提供了标准化的图形环境,允许用户选择和自定义NiosII处理器、存储器、标准外围设备、用户自定义外围设备等组件和接口,并自动生成必要的总线逻辑,将这些组件通过 Avalon总线连接到一起[4]。除了NiosII处理器,根据功能需求定制的外设主要有定时器、片上RAM、UART、输入输出IO等,此外为了能够实现软件调试定制了JTAG_UART组件,为了软件的配置启动定制了EPCS控制器,为了实现外部数据高速输入定制DMA组件。

图3 软件开发及启动过程示意图

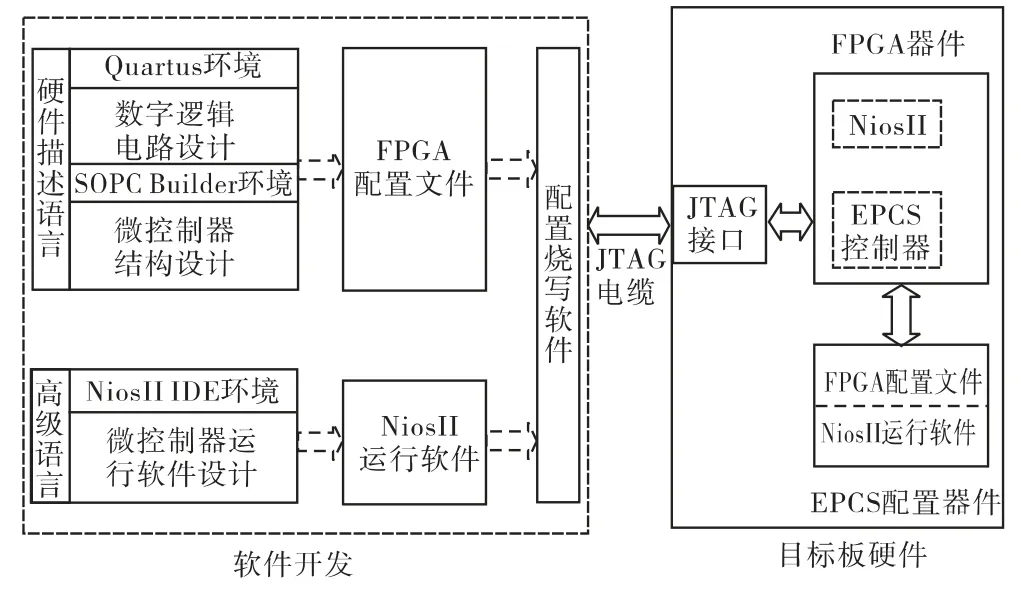

2)软件开发及系统启动过程

基于SOPC设计的软件开发主要包括基于硬件描述语言的数字逻辑电路设计NiosII微控制器构建和基于高级语言的微控制器运行软件设计两个部分。通过SOPC Builder定制的微控制器模块与Quartus软件中的其它设计模块,经过设计综合、布线最终可以获得FPGA的配置文件。通过Altera公司提供的NiosII软件开发集成环境NiosII IDE可以利用C或汇编语言完成微控制器的运行软件设计。软件开发完成后,可以通过JTAG接口电缆,烧写配置到信号处理板的EPCS控制器中[5]。当系统硬件电路加电后,首先从EPCS配置器件中读取FPGA的配置文件完成FPGA的配置工作,然后通过将NiosII中运行软件加载到片内RAM中,提升信号处理软件的运行速度。

3)软件的工作流程

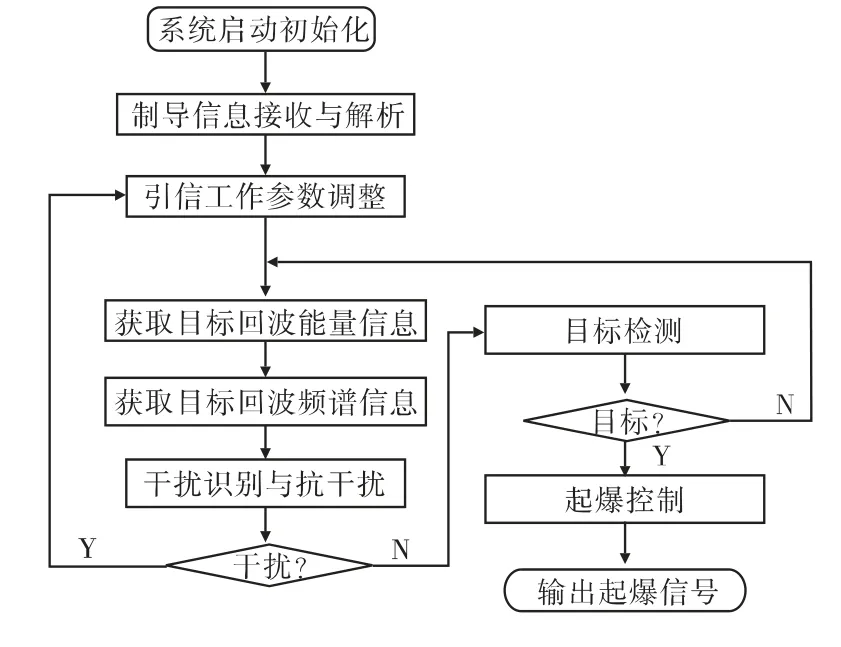

NIOSII中运行软件的功能是引信信号处理中最灵活、最核心的部分,它可以充分利用制导信息、目标回波信息等完成交会目标的识别、起爆功能,同时也具有完成干扰的识别并采用相应抗干扰措施的功能。软件工作示意流程如图4所示。

图4 软件工作示意流程图

3.3 高速运算和逻辑控制设计

在微控制器中利用软件实现大量高速密集的数字运算需要占用大量的处理器时间,因而为了获得更高的性能,可以充分利用FPGA中的硬件资源完成相关的运算和高速逻辑。在脉冲多普勒引信信号处理中主要的高速运算包括有效值计算和目标回波频谱计算等。

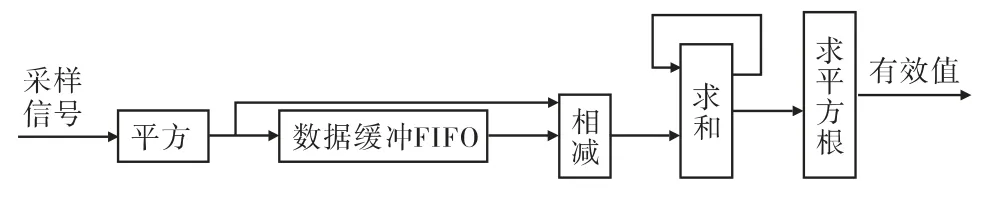

1)有效值的数字化计算

目标回波信号有效值可以用数字化的方法来近似计算,在FPGA中可以采用如图5所示的方法来完成。

图5 数字化有效值计算示意流程

当采样系统采样频率达到回波多普勒信号频率的6~8倍,即可以通过上述方法达到满意效果。通过调整数据缓冲FIFO的深度,可以灵活的改变有效值计算的累积时间。

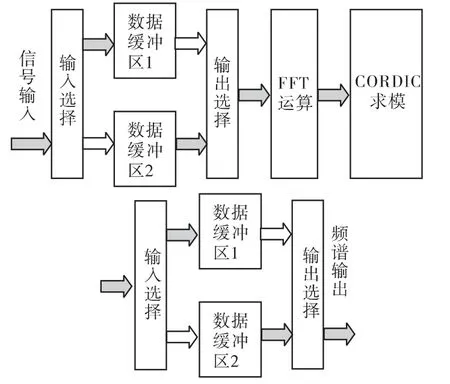

2)目标回波频谱计算

目标回波频谱获取主要依靠FFT运算和求模运算来实现。FFT(快速傅里叶变换)是数字信号处理中一个非常重要的基本变换,它能将一个时域信号转换成频域信号,其实现需要大量的密集的乘加运算。坐标旋转数字计算机CORDIC(coordinate rotations digital computer)算法的基本思想是通过一系列固定的、与运算基数相关的角度的不断偏摆以逼近所需的旋转角度,可以用于计算三角函数、双曲函数等[6]。

利用Altera公司提供的经过严格验证的FFT运算的IP核和CORDIC运算的IP核,通过设置相关参数可以实现FFT运算和求模运算,从而有效缩短开发时间。目标回波频谱计算流程示意如图6所示。

图6 目标回波频谱计算流程示意图

为了提高脉冲多普勒引信信号处理的实时性,采用乒乓操作来提高数据的处理速度。乒乓操作通过输入选择和输出选择单元按节拍、相互配合的切换,实现数据的无间断流水传输[7]。通过在FFT运算和CORDIC求模处理的输入之前和输出之后采用乒乓操作,实现数据的无缝输入缓冲、处理和输出缓冲。

4 结论

基于SOPC技术构建的脉冲多普勒引信信号处理器在硬件设计方面能够最大程度的简化系统硬件的设计,在软件设计方面能够完全依据引信功能需求来定制所需微控制器,实现了FPGA内部软硬件功能分配和协同设计,其主要功能都依靠软件编程来完成,从而提高引信信号处理的功能扩展能力和升级能力,能够满足引信不同研制阶段及后续性能升级的需求。

[1]袁正,李元级.现代空空导弹引信技术[J].航空兵器,2000(2):11-15.

[2]李兰英.NiosII嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[3]孙恺,王苗苗,魏洪兴,等.嵌入式 CPU软核综述[J].计算机工程,2006,32(7):6 -9.

[4]孟芳,于立佳,张文志.基于NIOSII的SOPC系统设计分析[J].无线电通讯技术,2012,38(1):73 -76.

[5]张学森,杜春鹏,孙实泽.NIOSII处理器在雷达信号处理中的应用[J].舰船电子工程,2007,27(4):126-128.

[6]张明友.数字阵列雷达和软件化雷达[M].北京:电子工业出版社,2008.

[7]吴继华,王诚.Altera FPGA/CPLD设计:高级篇[M].北京:人民邮电出版社,2006.