基于Avalon总线的LCD组件设计

2013-12-03郑恭明沈媛媛陈永军长江大学电子信息学院湖北荆州434023

郑恭明,沈媛媛,陈永军 (长江大学电子信息学院,湖北 荆州434023)

12864液晶模块的显示分辨率为128×64,其接口灵活、指令简单、操作方便,既可显示8×4行16×16点阵汉字又可完成图形显示,构成全中文的人机交互图形界面,因而被广泛应用。可编程片上系统SOPC (System on a Programmable Chip)[1]是以Altera推出的第二代软核 NiosⅡ处理器为核心的嵌入式系统,包括硬件的配置、设计、仿真与软件的设计、调试等。其开发流程包括2个方面,即基于QuartusⅡ、SOPC Builder的硬件设计与基于NiosⅡIDE的软件设计。在NiosⅡ系统的构建过程中,SOPC Builder开发环境集成了常用类型的设备模型,供开发者调用。下面,笔者基于Avalon总线进行LCD组件设计。

1 LCD IP核设计

片上可编程 (SOPC)技术可以根据具体的点阵LCD显示模块设计对应的驱动程序,对不同类型的点阵LCD显示模块完成对应的算法,提供相应的时序信号和数据信号。此外,可以根据不同的微处理器设计出对应的接口,适用于不同的操作,通过相关电路设计在一定程度上减轻微处理器的负担。

SOPC Builder开发工具允许用户依据相应规则扩展其所需设备组件IP(Intellectual Property)核,完成系统的设计和开发,开发者按照Avalon总线规范将设备驱动程序集成到SOPC Builder的硬件抽象层 (HAL)中,在SOPC Builder环境下加载使用,从而方便用户开发一个自定制的片上系统[2-3]。

1.1 硬件设计

设计时采用自顶向下的设计和自底向上的实现思想,将其分为3个功能模块:接口模块 (avalon interface)作为顶层模块,定义总线接口信号;寄存器文件模块 (register file)完成IP核与外部模块进行通信,提供访问与控制元件的逻辑界面;任务逻辑模块 (task logic)实现元件的硬件功能[4]。从最底层的模块开始编程实现,只要保证下层模块的正确性,上层模块的正确性也就容易得到保证。

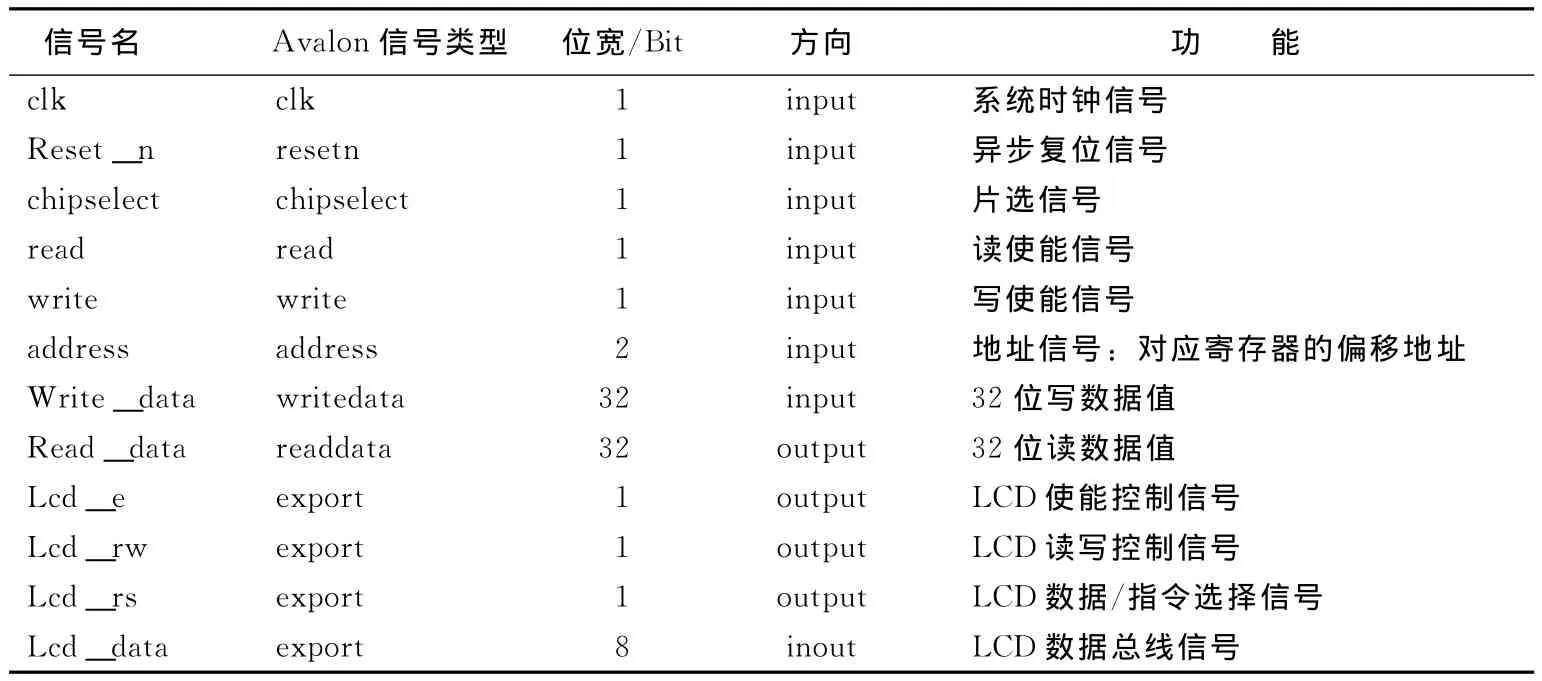

1)接口模块 接口模块作为顶层模块,为寄存器文件模块提供了一个标准的Avalon前端。它遵循Avalon总线的规范,实现对LCD IP核寄存器的访问,并支持任务逻辑的传输类型[3]。总线接口主要完成从NiosⅡ处理器接收指令和数据,实现对IP核的复位、片选、寻址及内部寄存器进行读写等操作。LCD接口信号如表1所示。

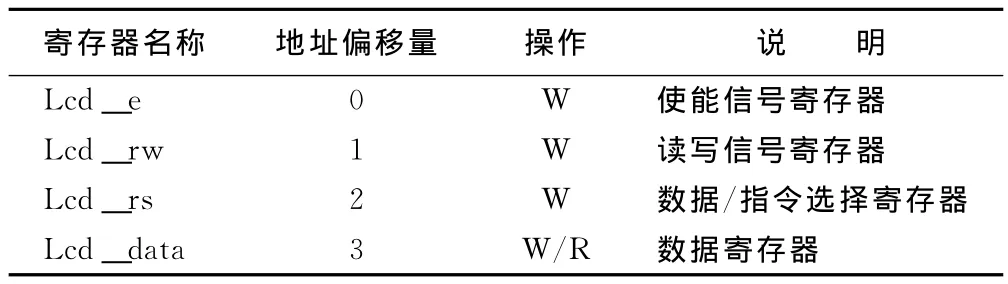

2)寄存器文件模块 寄存器文件模块提供了IP核与外界交换信息的途径,依据寄存器文件,可以通过Avalon接口采用“基地址+地址偏移量”的方式来访问IP核内部的各个寄存器。LCD IP核内部寄存器如表2所示。

表1 LCD接口信号

表2 LCD IP核内部寄存器

在HDL文件中,如果reset_n、chipselect、write均等于 ‘1’,且address信号为‘0’时,将write_data的数据写入Lcd_e控制寄存器;address信号为 ‘1’时,将write_data的数据写入Lcd_rw控制寄存器;address信号为 ‘2’时,将write_data的数据写入Lcd_rs控制寄存器;address信号为 ‘3’时,将write_data的数据写入Lcd_data数据寄存器。从而实现对LCD的显示控制。

3)VerilogHDL实现 利用Altera公司提供的Component Editor工具可以设计符合时序要求的外设接口,并且可以将用户开发驱动程序与NiosⅡHAL(硬件抽象层)系统库集成在一起,形成NiosⅡ 的接口组件,在系统生成的时候,对外设进行初始化设置。在建立新工程时,只需将接口组件添加到系统即可,这样对组件的访问变得轻松,并使得代码可重复利用。LCD组件的代码如下:

1.2 软件设计

NiosⅡHAL系统库是一个轻量级实时环境,提供一个组件驱动接口,使得程序与底层硬件通信。HAL API(应用程序接口)与ANSI C标准库集成在一起,允许用户通过库函数访问设备和文件,例如printf()、fopen()和fwrite()等,这样其他开发者无需知道底层硬件结构就可以对组件进行操作[4]。以下是对LCD寄存器的读写操作函数和功能函数的接口程序设计。

2 系统测试

构建SOPC系统是硬件开发的重点部分,需要添加7个模块,分别是NiosⅡ中央处理器、JTAG UART串行通信接口、SDRAM存储器、PIO口按键、设计的LCD2864组件、RAM片上存储器和PIO数据交换模块 (见 图1(a))。建好SOPC系统后再通过添加输入、输出管脚,选择对应的锁相环PLL模块并与SOPC系统连接,分配管脚等步骤 (见图1(b))。

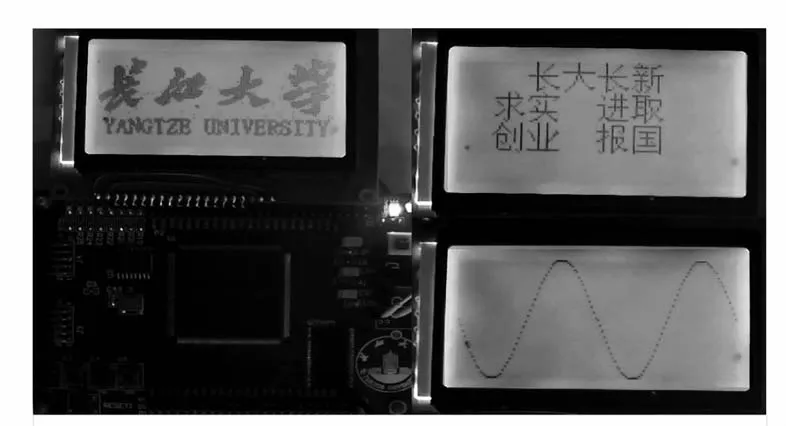

软件设计是在硬件系统搭建完毕的基础上在NiosⅡIDE软件中完成的,主要采用C语言进行编程设计,并在工程中加入驱动函数进行验证。在系统的硬件开发和软件开发完成后,将配置文件和编译好的程序下载到以EP3C16Q240FPGA芯片为核心的开发板进行测试,图片、字符和图形的显示效果图如图2所示。

3 结 语

在QuartusⅡ和NiosⅡ开发环境下,完成了基于SOPC技术的液晶显示屏的图形与字符显示的软硬件协同设计。该设计组件可移植性好,可以根据需要改变点阵LCD显示模块的显示内容。SOPC技术的灵活性使设计修改和产品升级变得简单,同时也提高了电子系统的灵活性和通用性。

图1 SOPC测试系统设计

图2 测试效果图

[1]杨军 .基于FPGA的SOPC实践教程 [M].北京:科学出版社,2011.

[2]刘敏,戴曙光,穆平安 .采用SOPC IP核技术实现液晶屏显示 [J].液晶与显示,2011,26(5):665-672.

[3]高枫,玉松 .基于Nios自定制Avalon设备的设计与实现 [J].中国测试技术,2007(7):105-108.

[4]蔡伟纲 .NiosⅡ软件架构解析 [M].西安:电子科技大学出版社,2007.