功能精确型多核处理器参考模型设计

2013-12-02纪丽婧汪国锋周晓慧

纪丽婧,汪国锋,周晓慧

(1.杭州电子科技大学自动化学院,浙江 杭州310018;2.浙江省福利彩票发行中心技术部,浙江 杭州310012)

0 引 言

嵌入式产品应用的日益复杂促使系统对处理器的性能需求越来越高,多核处理器已逐渐成为嵌入式系统应用的主要选择之一[1]。复杂的多核处理器及其高速缓存一致性使得其功能验证愈加庞大[2]。为在验证中尽早发现设计缺陷,如何构建和实现高效准确的多核处理器参考模型已成为关键问题和重大挑战[3-4]。现在主流的多核处理器参考模型分为时序精确型参考模型[5]、传输级精确型参考模型[6]和功能级精确型参考模型[7]。时序精确型参考模型的特点是:能精确模拟硬件细节,能够准确评估多核处理器的性能,有利于同时追踪功能和性能缺陷,但模型开发周期长,仿真时间长,不利于设计前期多核处理器的功能验证。传输级精准型参考模型是在传输级精确型参考模型的基础上进行了抽象,忽略处理单元的时序信息,其仿真效率高于时序精确型参考模型,同时能准确给出核心通信的性能。功能精确型参考模型在传输级精确型参考模型的基础上进一步抽象,只保证功能正确。其特点是:实现简单,仿真效率高。功能精确型参考模型虽然无法早期评估架构的性能,但能够为硬件设计提供功能结果的参考,在多核验证中被广泛采用。在同构多核处理器的验证中,高速缓存一致性一直是验证人员关注的重点和难点。能否提供高效的高速缓存一致性验证机制,直接影响到多核处理器的验证效率。当前大部分功能精准型多核参考模型只给出最终的执行结果,无法精确地模拟硬件高速缓存一致性操作过程,这给错误的追踪带来巨大的困难,显著降低验证的效率。本文提出了一种新的功能精确型多核参考模型架构和流程,本参考模型通过读写指令顺序作为输入,采用指令提前执行模块技术和高速缓存一致性模块技术来精确模拟多核处理器硬件并发操作和高速缓存一致性功能。

1 多核参考模型的架构与流程

多核处理器验证的典型流程如图1所示,首先将测试激励文件分别输入到多核处理器和参考模型中,得到执行结果后,再将两者的执行结果进行对比,判断设计是否正确。本文采取的就是这样的流程。

图1 多核处理器验证流程

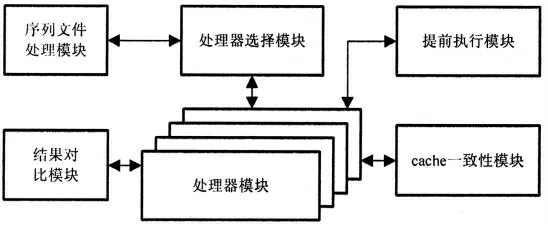

本文提出的多核参考模型架构如图2所示,由6部分组成:序列文件处理模块、处理器选择模块、处理器模块、结果对比模块、提前执行模块和高速缓存一致性模块。序列文件处理模块负责读取并处理序列文件。为了精确模拟硬件高速缓存一致性,参考模型中读写指令的执行顺序与硬件的执行顺序保持一致,为此,引入了序列文件。在序列文件中,所有读写指令按其访问存储器的先后顺序排列,参考模型将严格按照序列文件中的顺序执行读写指令。序列文件中的信息包括:读写指令编号、处理器标识(ID)、PC、指令访问的地址和数据等信息。处理器选择模块用于选择执行下一条指令的处理器。如果当前被选中的处理器要执行的下一条指令为读写指令,且处理器与序列文件处理模块提供的处理器ID不一致,处理器选择模块将切换处理器,序列文件中指示的处理器将被选中;否则,处理器选择模块不工作,被选中的处理器继续执行指令。

图2 参考模型架构

提前执行模块决定一条读写指令是否需要被提前执行。若被选中的处理器要执行的下一条指令为读写指令,其处理器ID与序列文件处理模块提供的处理器ID 匹配,但PC与序列文件处理模块提供的PC 不匹配,则序列文件处理模块指示的指令将被提前执行;否则,提前执行模块不工作。高速缓存一致性模块负责维护高速缓存一致性,其接收并响应处理器模块发送的高速缓存一致性请求。提前执行模块和高速缓存一致性模块是多核处理器参考模型的两个关键模块,确保准确模拟指令乱序执行、多核并发操作和高速缓存一致性功能。

处理器模块负责执行指令,包括取指、译码、执行等子模块。指令是多核参考模型的最小执行单元,即多核参考模型中没有流水线及周期。这种简单的调度方式能很好地满足单核处理器功能验证,但在多核处理器功能验证中,需要结合序列文件以确定各个处理器的读写指令执行顺序。结果对比模块用于对比参考模型的执行结果与硬件执行结果,从而发现设计缺陷。

1.1 多核参考模型工作流程

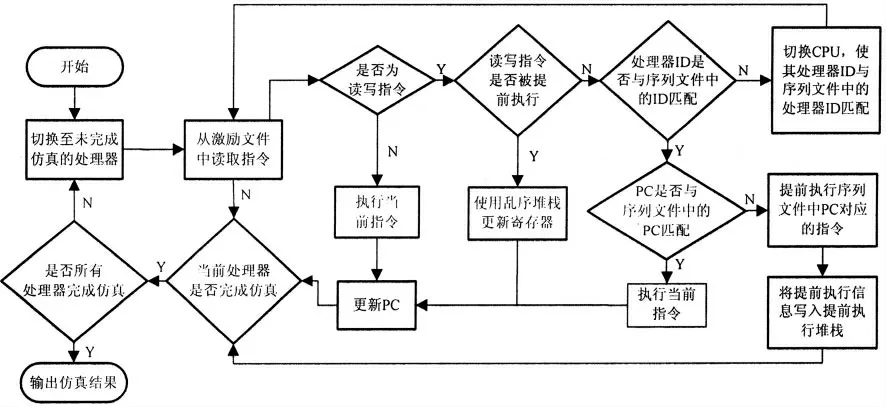

多核参考模型的工作流程如图3所示,参考模型首先选择未完成仿真的处理器,并读取指令。

若本指令为非读写指令,本处理器执行当前指令。若本指令为读写指令,判断本指令是否被提前执行,若本指令被提前执行,使用乱序堆栈中保存的值更新寄存器;若本指令未被提前执行,且当前处理器ID与序列文件中的处理器ID 不匹配,则切换处理器,使其处理器ID与序列文件中的处理器ID 匹配;若本指令未被提前执行,且当前处理器ID 及PC与序列文件中的处理器ID 及PC 匹配,则执行当前指令;若本指令未被提前执行,且当前处理器ID与序列文件中的ID 匹配,但PC与序列文件中的PC 不匹配,则提前执行序列文件中PC 对应的指令,并将提前执行信息写入提前执行堆栈中。每执行完一条指令(包括提前执行),需要判断处理器是否完成仿真,若当前处理器完成仿真且其它处理器未完成仿真,则切换至未完成仿真的处理器继续执行指令;若所有处理器完成仿真,则停止并输出仿真结果。

图3 多核参考模型工作流程

1.2 高速缓存一致性模块

参考模型采用高速缓存一致性协议[8]作为高速缓存一致性协议,各处理器严格按照高速缓存一致性协议执行指令。当发生读缺失、写缺失、写命中且高速缓存块状态为共享时,处理器模块将向高速缓存一致性模块发送高速缓存一致性请求。

1.3 提前执行模块

本文介绍的参考模型引入了提前执行堆栈。当一条读指令被提前执行,其数据不会被直接写回寄存器,而是暂存在提前执行堆栈中,直到参考模型PC与被提前执行指令的PC 匹配,将数据写回寄存器。提前执行堆栈包括处理器ID、指令PC、指令是否为读指令、指令读取的数据、指令使用的寄存器等信息。参考模型遵守序列文件中的指令顺序执行读写指令。

2 仿真实验

为评估参考模型的可实现性,将本模型用于自主国产CK610 多核处理器验证平台,详细流程如图4所示。由于功能级参考模型无法模拟硬件的时序信息,例如中断等。通过软硬件交互的仿真方法,在硬件RTL仿真过程中获取以上信息,并通过文件传输给参考模型。因此,参考模型需要接收一定格式的事件输入,包括含有中断信息的中断历史文件、含有在直接访问存储器传输过程中完成指令信息的DMA 传输文件、含有TLB条目信息的TLB 历史文件以及含有读写指令顺序信息的读写指令序列文件。

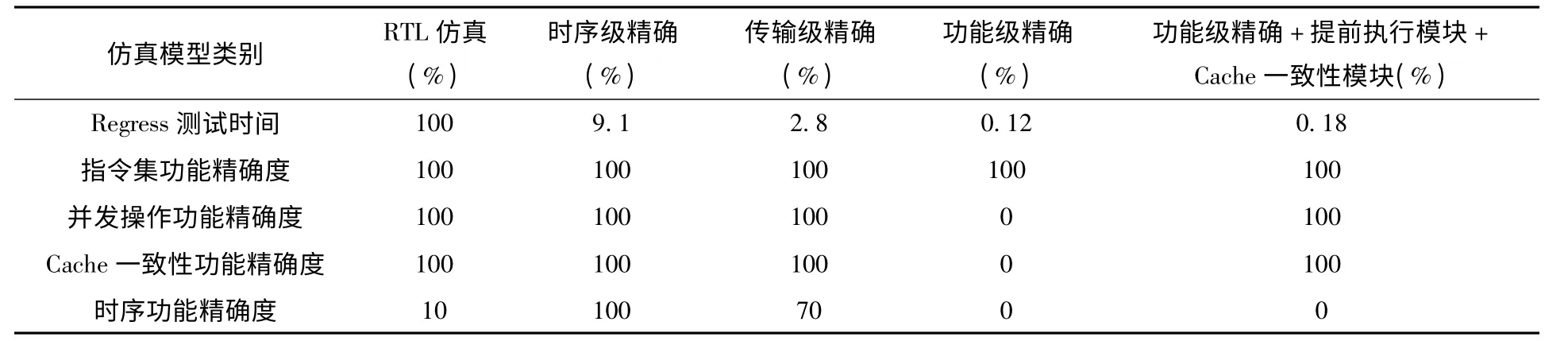

如表1所示,在CK610MP 多核处理器的设计验证过程中,本文分别构建了时序级精确、传输级精确和功能级精确模型,并在功能级精确模型上添加了提前执行模块和Cache 一致性模块两个技术。通过处理器所有Case的Regress 测试,可以发现本文提出的参考模型在仿真时间上是RTL的0.18%,并可以100%的并发操作和Cache 一致性功能精确度。与传统的时序级精确、传输级精确和功能级精确模型相比,本文模型通过利用提前执行模块和Cache 一致性模块两个技术,取得了仿真时间和仿真精确度较好的折中,可显著提高多核处理器的验证开发效率。

表1 各仿真模型运行时间结果表

3 结束语

本论文阐述了一种新的用于多核处理器验证的功能精确型多核参考模型,本参考模型通过指令提前执行模块技术和高速缓存一致性模块技术来精确模拟多核处理器的高速缓存一致性和并发功能,快速高效实现多核处理器功能级验证。若多核处理器设计出错,本参考模型能提供出错指令的详细信息,便于跟踪设计缺陷。仿真证明:与时序精确型多核参考模型和传输级精确型多核参考模型相比,本多核参考模型能快速完成仿真,在保证验证正确性的同时,提高了验证效率。

[1]Ahmed Jerraya,Wayne Wolf.Multiprocessor Systems-on-Chip[M].San Francisco:Elsevier Morgan Kaufmann,2005:1-9.

[2]黄凯,殷燎,林锋毅,等.一种多处理器原型及其系统芯片设计方法[J].电子学报,2009,37(2):181-186.

[3]黄永勤,朱英,巨鹏锦,等.“申威-1 号”高性能处理器的功能验证[J].软件学报,2009,20(4):1 077-1 086.

[4]张欣,黄凯,孟建熠,等.一种面向微处理验证的分层随机激励方法[J].计算机应用研究,2010,37(4):30-35.

[5]Felix Sheng-Ho Chang,Alan J Hu.Fast Specification of Cycle-Accurate Processor Models[C].Britain∶International Conference on Computer Design,2001:1 488-2 001.

[6]Zhou Haixiang,Ge Ning,Xu Lixin,etal.Transaction Level Modeling of SPARC Based on TLM2.0[J].Computer Engineering,2011,68(12):14-19.

[7]Mehrdad Reshadi,Nikil Dutt.Generic Pipelined Processor Modeling and High Performance Cycle-Accurate Simulator Generation[J].Design Automation and Test in Europe,2005,99(1):786-791.

[8]John L Hennessy,David A Patterson.Computer Architecture A Quantitative Approach[M].Fourth Edtion:Elsevier,2007:167-174.