边界扫描技术在某导航雷达控制电路板测试与诊断中的研究运用*

2013-11-28马溧梅

柳 颖 马溧梅 张 静

(海军七〇二厂 上海 200434)

1 引言

随着纳米数量级制造工艺的使用和大规模集成电路的发展,集成电路的集成速度快速增加,同时其封装管壳尺寸变得越来越小,FPGA、DSP器件以及BGA封装器件在最新产品中得到了大量的应用[1]。这些改变为电路设计带来了很大的便利,如其功耗的降低、面积的减小等;同时,它也带来了一些困扰。例如,由于功能模块或芯片内部节点变得无法探测,使得电路调试工作存在一定的困难,因为测试过程中无法使用测试探笔,导致大量故障变得很难测试,甚至根本没有物理测试点。由于芯片或器件封装的减小,管脚密度增大,从而大幅度提高了单位PCB电路板上的器件密度,增加了互联测试的难度,降低了芯片互联的可靠性[1]。这类芯片的测试与诊断问题对传统的诊断方法提出了更高的要求,由于传统测试技术面临的测试困难的增多,需要一种新的测试理念和测试技术来解决传统测试方法所无法解决的问题。边界扫描技术应运而生[8]。边界扫描技术作为一种国际标准,提供了一套完整的、标准化的超大规模集成电路测试性设计方法,能克服测试复杂数字电路的技术障碍,利用它可以实现芯片级、板极和系统级的测试。基于边界扫描测试技术的故障诊断突破了传统的管脚接触式检测理论和手段,可以解决其他技术无法完成的超大规模集成电路的测试问题,可以解决新型电子装备中含可编程超大规模集成电路器件(CPLD及FPGA)、微处理器和数字信号处理器(DSP)等器件的电路板的板级测试和系统级测试问题,己日益成为可测试性设计中应用最为广泛的技术之一,并己经形成了一系列的国际标准[7]。

本文介绍了边界扫描技术的原理、优点。通过提出某导航雷达控制电路板的测试与诊断问题,运用边界扫描技术,给出了该电路板的测试与诊断解决方法。可以将故障迅速定位到芯片的管脚以及芯片管脚之间的连线上,提高了测试的可靠性和测试效率。

2 边界扫描技术

2.1 边界扫描技术简介

边界扫描测试技术是联合测试行动组(JTAG)于1987年提出一种新型的电路板可测性设计方法。1988年,IEEE和JTAG组织达成协议,共同开发边界扫描测试架构,并于1990年形成了IEEE 1149.1标准,也称为JTAG标准[6]。到目前为止,边界扫描技术已经成为一种比较成熟的技术,现已为全世界绝大部分的IC设计制造商所采用。它为芯片的逻辑和封装提供了一种方便简捷的快速测试接口,从而替代了传统的利用探针测试芯片的方法。这种测试过程不仅体现在芯片制造生产期,还可以用来改进电路错误检查和隔离的能力。JTAG端口在几乎所有使用高性能数字器件的印刷电路板中都会出现,这就为采用基于边界扫描技术来测试PCB提供了基本条件。

2.2 边界扫描技术原理

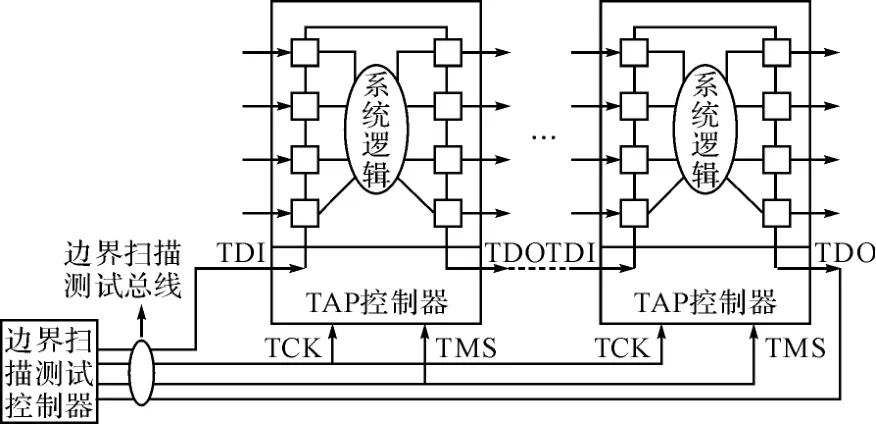

图1 边界扫描结构图

边界扫描测试机制是通过边界扫描测试总线和设计在器件内的边界扫描结构(如图1所示)实现的。边界扫描测试总线主要完成测试向量输入,测试响应向量输出和测试控制功能,由4根(5根)测试总线构成[6]。器件内边界扫描结构主要由TAP测试存取口(又称JTAG口)、TAP控制器和若干寄存器组成。TAP控制器接收来自边界扫描测试总线的命令并且控制边界扫描单元的行为,从而实现对器件管脚状态的设定、读取和隔离定位。TAP总共包括5个信号接口:测试时钟输入信号(TCK)、测试模式选择信号(TMS)、测试数据输入信号(TDI)、测试数据输出信号(TDO)、测试复位信号(TRST)。TRST是一个可选的测试线,当逻辑“0”施加于TRST端口时,TAP的测试逻辑异步强制进入复位方式。

2.3 边界扫描测试方法的优点

基于边界扫描(JTAG)的PCB测试能以非传统的方式获得PCB电气连接性的信息,它具有如下优点[1]:

1)方便芯片的故障定位,迅速、准确地测试两个芯片管脚的连接是否可靠,提高测试、检验效率;

2)采用无物理接触的“虚”导通访问,无需外加硬件电路,测试起来简洁快速,且准确安全[10];

3)对挂在JTAG接口的芯片上的存储器(SRAM、DPRAM、SDRAM、FIFO、FLASH 等)、模拟芯片以及功能电路进行测试;

4)对具有JTAG口的现场可编程器件实现在线编程功能[9]。

3 雷达控制电路板简介及总体测试思想

3.1 控制电路板简介

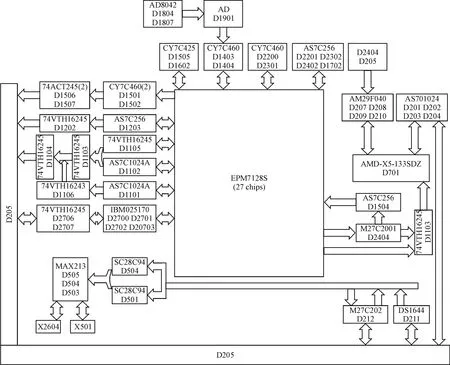

本文介绍的某导航雷达中的控制电路主要由27片可编程器件EPM7128SLC100和1片微处理器芯片AMDX5-133及大量的外围电路包括RAM,ROM,FALSH 组成。图2为电路的原理框图。该控制电路板在器件上使用了集成度较高的器件,芯片封装采用了QFP100、PLCC52等多种表贴器件,器件引脚中心距离小,采用探笔测试会增加测试的风险,破坏电路的工艺;并且电路上的处理器芯片不能从电路板上拔下,所以采用边界扫描技术是最佳的选择[3]。

图2 电路原理框图

3.2 控制电路板测试诊断分析

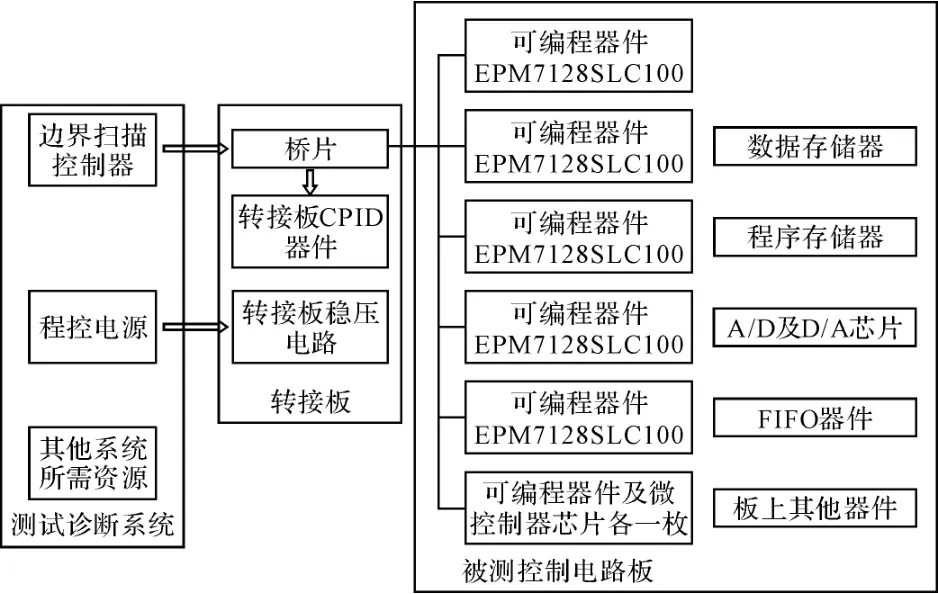

对该控制板的测试使用了北京博基兴业科技公司的ITEST-ATE电路板测试系统。根据被测控制板的电路特点,设计制作了专用的转接电路板,转接板用于实现测试系统与被测板件的连接,完成测试链路的控制以及与被测电路板上的边扫器件组成测试链路的功能。图3是测试与诊断系统整体框图。

图3 测试与诊断系统整体框图

3.2.1 链路设计

该导航雷达控制电路板上有28片边界扫描器件,27片EPM7128SLC100,1片微控制器芯片 AMD-X5-133SDZ。针对这种复杂的板子,在测试过程中分为6条链路,前5条链路中每条链路包括5片EPM7128SLC100LC100,第6条链 路 包 括 2 片 EPM7128SLC100LC100,1 片 AMD-X5-133SDZ,这样在测试过程中可以提高测试信号的稳定性和测试结果的可靠性。

3.2.2 RAM的测试

该导航雷达控制电路板主要有AS7C256、AS7C1024、DS1644、IBM025170这四种RAM。这些RAM一部分是挂在 EPM7128SLC100和 AMD-X5-133SDZ上面,一部分是跟D205接插件相连接的。对于挂在EPM7128SLC100上面的RAM,如图2的D2201,通过控制EPM7128SLC100上与RAM相连接的引脚,可以控制RAM的读写,把写入的数据跟读出的数据做比较可以检测出片子的好坏,以及引脚的焊接是否存在问题。对于连接在接插件上面的RAM比如D1203可以做一个接口板,让接口上面的所有引脚都连接到边界扫描引脚上面,这样所有的引脚都可以控制读写,同样可以检测出这些芯片的质量问题。

3.2.3 FIFO的测试

电路板上面的FIFO主要包括CY7C425、CY7C460,这些片子主要挂在EPM7128SLC100上面做数据缓冲用,因此测试这类片子比较容易,跟RAM的测试类似,通过写脚本控制EPM7128SLC100与FIFO相连接的引脚,控制FIFO读写数据,检测出其质量的好坏。

3.2.4 ROM的测试

被测电路板上的ROM主要包括M27C2001,M27C202,这些ROM主要为其他芯片提供地址线。比如D2404CY7C2001可以为RAM D1504AS7C256提供8位数据线,在测试中可以将D1504,D2404放到一起测试,通过EPM7128SLC100往D2404地址线送入数据,再通过EPM7128SLC100从D1504的IO端口读出数据,从而同时检测这两个ROM芯片。

3.2.5 FLASH测试

FALSH部分主要由四颗AM29F040组成,地址线一部分由M27C2001芯片提供,一部分由D205提供,数据线是与微控制器芯片AMD-X5-133SDZ连接。FLASH芯片可以通过测试软件自带的FALSH检测功能编程,通过循环读写数据,准确检测出芯片的好坏,该测试软件同时支持FLASH芯片的在线烧录。

3.2.6 AD部分测试

AD部分的测试,只能整体测试其模块功能的好坏,不容易定位到具体的引脚。D1901输出的数字信号控制FIFO的地址信号线,FIFO的数据信号线输出到EPM7128SLC100上面,主要通过对FIFO写入数据,再读出数据做比较,判断AD部分和FIFO好坏。

3.2.7 其他器件

对于控制电路板上面的74ACT245S,74LVTH16245ADL等74系列芯片,在测试RAM,FIFO等的过程中进行完整的测试,如有数据通过链路,则判定此类器件正常。

3.3 测试与诊断系统的开发流程

测试软件的开发工具为美国ASSET公司的Scan-Works开发平台。针对该控制电路板,测试软件的开发流程有以下几个步骤:

1)在ScanWorks开发环境中创建PCB系统板的工程,导入电路设计的网表文件。其中电路包括测试站的主板电路、转接板电路以及被测的控制电路板电路。网表形式为allego网表。以上三个网表分别导入。

2)选择创建扫描链的方式,一般选择手动建立。属于边界扫描的器件需要选择BSDL文件,添加到扫描链路中去,非边扫器件统称为“Cluster”器件。添加时没有先后顺序,添加完成后单击Build实现编译。BSDL编译没有问题后会生成后缀名为hgl的链路文件,该文件不仅包含了扫描链的信息还有扫描链上器件的信息。

3)一个工程中可以允许建立最多不超过七条的扫描链路,因此还需建立一个工程链路。本次测试过程使用了JTS10U桥片,使用该桥片扩展了六条扫描链路。在建立扫描链之前先找到这个芯片的编译文件,该文件的后缀名为adb。

4)桥片添加完成后,把电路板测试系统,转接板,还有被测板上面的边界扫描器件按照TDI、TDO的顺序添加到相应的链上。所有的器件都添加完成后,点make进行编译,编译没有问题就表明链路添加已完成。

5)设定相应规则后,分析网表,运行测试程序检查故障覆盖率。在本次开发过程中,故障覆盖率≥85%,故障检测率为93%。

4 结语

边界扫描技术的出现是可测试性设计和测试思想的一次飞跃,它提供了一种完整的、标准化的电路板可测试性设计和测试方法[2]。采用边界扫描测试技术实现某导航雷达控制电路板的互连性、簇测试以及器件功能的测试,达到故障定位的目的。通过在测试转接板上放置具有边界扫描功能的芯片与被测板上的控制芯片构成测试簇,提高了电路测试的故障覆盖率。该测试诊断方法的研究及运用同样适用于其他高集成度、高性能的复杂电路板件的维修测试与故障诊断,具有非常重要的实用价值。

[1]王石安,吴晓晔,徐鹏程.基于边界扫描的BIST技术[C]//第二十届全国测试与故障诊断技术研讨会论文集,2011,8:184-189.

[2]张学锋,王彤威,王国龙.边界扫描技术在微处理器电路板测试与诊断的研究[J].计算机测量与控制,2010,18(6):1250-1252.

[3]刘军.基于边界扫描技术的PCB测试[J].中国科技信息,2010,16:130-132.

[4]陈岩申,王新洲,张波.基于FPGA的电路板自动测试技术研究[J].计算机测量与控制,2010,18(7):1500-1502.

[5]李修杰.基于FPGA的边界扫描测试系统的研究[J].航空电子技术,2010(4):28-30.

[6]IEEE std 1149.1-2001[8].New York:The institute of Electrical and Electronics Engineers,Inc.,2001.

[7]陈亮,胡善伟,张重雄.边界扫描技术及应用[J].航空计算技术,2009(1):128-130.

[8]崔伟,冯长江,丁国宝.基于单片机的边界扫描实验系统的改进设计与实现[J].计算机测量与控制,2009,17(8):1477-1478.

[9]张学斌.基于JTAG的互连测试技术[J].电子产品,2004(5):5-6.

[10]吴明强,赵文彦,杜影.基于VXI总线的多功能边界扫描控制器的研制[J].计算机测量与控制,2006,12(8):856-858.