基于τ因子伺服信号内插时钟恢复的设计与实现*

2013-11-24王庆东罗中良刘宇芳

王庆东,罗中良,刘宇芳

(惠州学院计算机科学系,广东惠州 516007)

伺服信号时钟恢复的设计关系到微硬盘读写通道数据传输的稳定性和可靠性[1-3],高精度及高可靠的时钟恢复设计对微硬盘读写通道的性能起着重要的作用。

作者在文献 [4]给出了硬盘读写通道同步采样时钟恢复的典型模型,并对基于锁相环技术实现时钟恢复的通用解决方案进行了详细分析。但该模型和方案存在诸如如对噪声较为敏感、受游长受限码k的长度限制[4-5](一般k要小于8)等问题。本文在此方案基础上进行改进,采用基于τ因子内插时钟恢复技术实现时钟恢复,基于τ因子内插时钟恢复的优势在于读信号时对噪声的敏感性不强,同时也不会受线路以及结构所引起噪声的影响。可以使游长受限码的k>8。并在线性插值时钟恢复的基础上提出基于τ因子内插时钟恢复模型,推导出τ因子插值滤波器系数算法。

通过采用FPGA加DSP构成的系统进行试验验证,可以得到结论,即采用τ因子内插时钟恢复技术比线性插值算法能优化一倍的谐波含量。

1 基于τ因子内插时钟恢复技术

1.1 基于锁相环电路的时钟恢复技术

图1是硬盘读写通道同步采样时钟恢复的典型模型,图中伺服信号时钟恢复模型采用锁相环技术[5-6],并由锁相环电路的基本模块组成,例如采样器,鉴相器,鉴频鉴相器,压控振荡器,零相位开始控制等。从IBM公司的文献及Marvell公司带硬盘控制器芯片88i6310可知,目前都是采用这种方案,它采用锁相环技术的同步时钟对通道模拟信号同步采样,压控振荡器控制采样设备采样转换器的采样时钟,鉴相器产生相位误差,环路滤波器产生采样时钟和波特率的频率偏置Δf,Δf调整采样时钟和波特率同步[5]。

1.2 存在的问题

采用锁相环技术实现时钟恢复虽然是目前通用的解决方案,但也存在一些问题如对噪声较为敏感,也受游长受限码 (RLL)的k的长度限制,一般k要小于8,下面将对此方案进行改进,采样内插时钟恢复技术实现,内插时钟恢复的优势在于读信号时对噪声的敏感性不强,同时也不会受线路以及结构所引起噪声的影响。可以使游长受限码RLL的k>8。

1.3 基于τ因子内插时钟恢复技术

本文所设计的内插时钟恢复模型如图2所示。模型主要包括的模块有:内插器、模Ts累加器、时隙器、相位错误检测器、频率合成器、零相位起始判断等。

由图2内插时钟恢复可以看到内插器和模Ts累加器代替传统时钟恢复的频控振荡器,相位误差检查器输入实际采样值Yk+τ同时计算电路捕获过程中的相位误差,在跟踪过程中多路选择器则选择时隙器输出的估算采样值 ~Yk+τ。数据时钟是由模Ts累加器产生的屏蔽信号和异步采样时钟进行相与操作而成,相位误差检测器和时隙器生成内插采样值,PID环路滤波器控制闭环频率响应产生频率偏置信号,频率偏置Δf通过模Ts累加器进行累加产生内插时隙τ,通过τ可以估算内插器所需内插的采样值。

图2 伺服信号内插时钟恢复模型

1.4 定时同步算法

内插时钟恢复电路可以从采样序列中恢复出最佳采样点的值[7-8]。设带限连续信号),周期为T在满足Nyquist定理的条件下,以Ts为间隔采样得,通常T/Ts为无理数。经内插时钟恢复环路后,输出,其中Ti=T/K,K为小整数对进行K倍抽取,即得到与发送端符号同步的最佳采样值序列。内插时钟恢复电路包括一个内插滤波器和内插滤波控制电路,内插滤波器从采样序列中恢复出最佳采样值,是整个定时同步的关键。控制电路包括定时误差检测电路、环路滤波器和数控震荡器,向内插滤波器提供插值相位和插值输出时各个信号的权值。

1.5 τ因子内插器设计模型

理想离散时间相位插值滤波器是基于平滑响应和τ值延迟固定,理想的冲击响应如下:

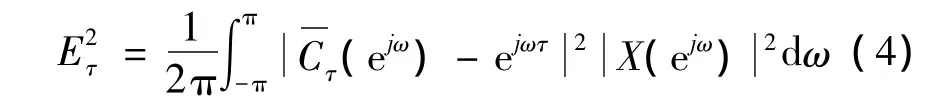

由于非关联无限冲击响应是无法实现的,因此插值滤波器的冲击响应设计成自适应理想冲击响应,并通过实际插值滤波器频率响应和理想插值滤波器的最小均方根误差来实现[6],本文考虑对输入信号的频谱的改进,即输入信号频谱与实际插值频谱相乘和输入信号频谱与理想插值频谱相乘的最小均方根误差:

式中的 X(ejω)是读通道的 (如 PR4,EPR4,EEPR4)部分响应频谱。在实际应用中,其均方根误差等式用限带输入信号频谱代替,预先确定常数0≤ω≤απ(0<α<1),则可以得:

那么式 (4)可以用下式表示:

式 (6)的解包括对滤波系数的实际插值滤波器和经典绝对平均的理解。实际插值滤波器可以用FIR多项式表示:

式 (7)中的R是每个插值滤波器的抽头数,采样时间Ts被规格化到1,一个计算插值滤波系数值算法可以通过计算推导得出:

通过其派生出的一个偏微分方程,并置为0,得:

代入式 (6)可导出得:

定义φ(r)为:

于是有:

式中所定义的R线性等式依据滤波系数Cτ(n)用矩阵表示为:

等式中的Cτ是一个向量结构:

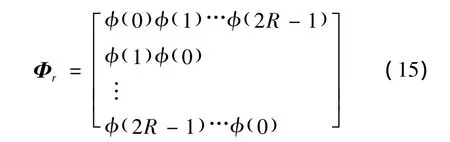

Φr是一个矩阵:

并且转置矩阵Φτ是为:

式 (16)的解:

2 试验验证

2.1 验证方案

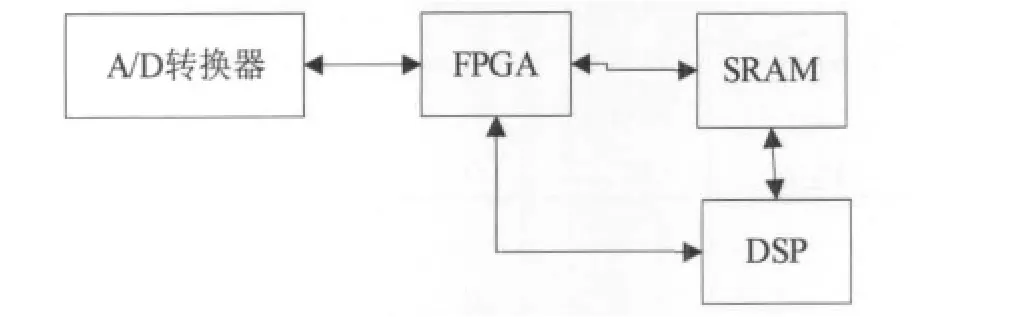

τ因子内插器模型硬件设计方案采用DSP加FPGA构建系统[5],实现ADC转换器采样通道设计、插值滤波器设计,采用FPGA实现τ因子插值滤波算法,SRAM保存滤波系数,且设计时分成两页,每页为1024字,一页保存滤波系数,另一页存放插值结果。DSP把滤波系数传入SRAM并把FPGA插值结果送入SRAM,ADC转换器采样线性公司12 bit转换器,设计框图如图3所示。

图3 内插时钟恢复硬件设计框图Fig.3 Hardware diagram of interpolation timing recovery

2.2 τ因子插值滤波器设计试验

试验条件为2R=6,α =0.8,X(ejω)=PR4 表1和表2分别为线性插值滤波的谐波频谱和τ因子内插滤波器的谐波频谱,表3为τ因子滤波系数。结果表明τ因子内插滤波器的谐波频谱要优于线性插值滤波频谱。

表1 线性插值谐波频谱Table 1 Harmonic spectrum of linear interpolation

表3 τ因子滤波系数Table 3 τ Factors filter coefficients

3 结论

指出采用锁相环电路的伺服信号时钟恢复电路的不足,研究采用插值时钟恢复技术,提出基于τ因子内插时钟恢复模型,并推导出τ因子插值滤波器系数算法,给出基于线性插值和基于τ因子内插时钟恢复试验测试结果,通过试验从频谱分析可以看出采用τ因子插值比线性插值的效果要好,特别是在谐波3次、5次、7次、9次等奇次谐波含量不超过基波含量的0.8%,而线性插值的谐波含量将近达到基波含量的2%。

[1]赵东超.硬盘驱动器高性能控制方法研究及其仿真系统的设计[D].西安:西北工业大学,2000:27-31.

[2]NAGARAJ K,LEWIS S,WALDEN R,et al.A median peak detecting analog signal processor for hard disk drive servo[J].IEEE Journal on Solid-State Circuits,1995,30(4):461-470.

[3]余嵘峰,余胜生,周敬利,等.一种3.5英寸硬磁盘驱动器伺服系统结构分析[J].电子计算机外部设备,1995,19(5):25-28.

[4]王庆东.硬盘读写通道伺服信号检测关键技术研究[D].武汉:华中科技大学,2007.

[5]王庆东,谢长生,王海卫,等.基于DSP和FPGA直接数字频率合成系统的设计[J].计算机工程与科学,2007,29(9):126 -128.

[6]秦军瑞,陈吉华,赵振宇,等.锁相环电路中压控振荡器的SET响应研究[J].计算机工程与科学,2011,33(1):87-90.

[7]李学初,高清运,陈浩琼.具有宽捕获范围的时钟恢复电路[J].南开大学学报,2008,56(3):139 -143.

[8]SHAKIBA M,JOHNSD,MARTIN K.General approach to implementing analogue Viterbi decoders[J].Electronics Letters,1994,30(27):1823-1824.

[9]MITA S,TAKASHI T,NISHIYA T.A PRML and EPRML spliced operation scheme designed to reduce power dissipation of read channel chips[J].IEEE Transactions on Magnetics,1998,34(1):153-159.

[10]ANDRIES P H,LUDO M G M T.Guaranteed scrambling[J].IEEE Transactions on Magnetics,2005,41(11):4323-4326.