考虑时延偏差的数字电路时延测试综述

2013-11-23李华伟

李华伟

(中国科学院计算技术研究所计算机体系结构国家重点实验室 北京 100190)

1 引 言

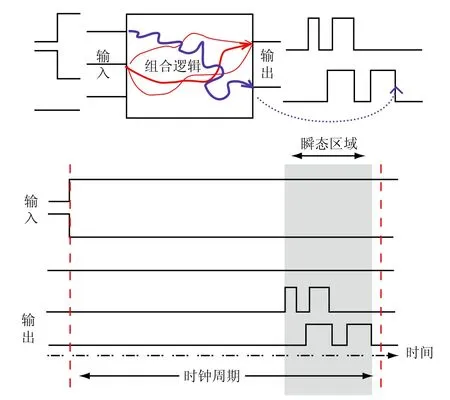

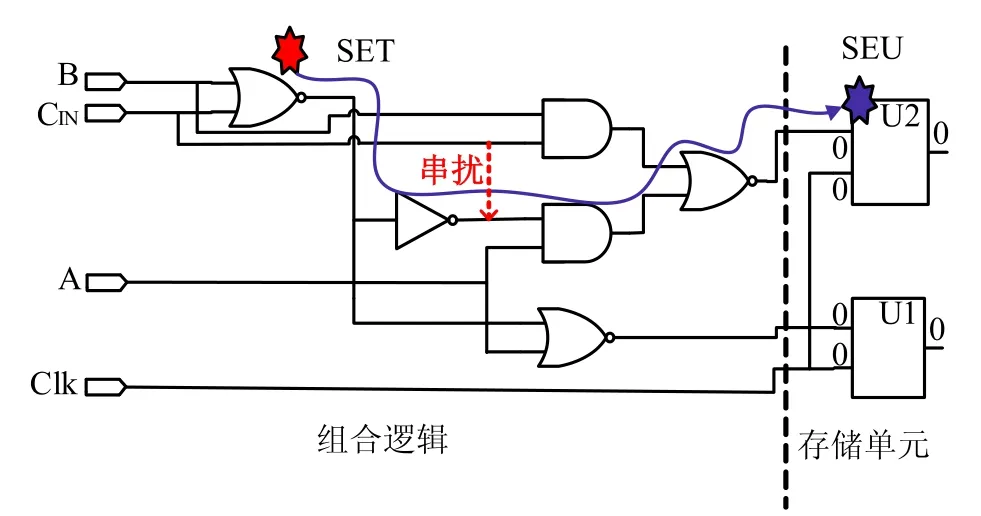

在集成电路中,门和线都具有传输延迟。考虑数字集成电路,如图 1 所示,由于组合逻辑的输入信号沿着具有不同延迟的多条信号传播通路到达组合逻辑的输出端,在输出端会产生由多个跳变信号组成的波形,构成电路的瞬态区域(如图 1 所示)。人们所接触到的电路以同步时序电路为主,且其在额定的时钟周期/时钟频率下进行工作。电路中最大延迟通路(如图1 组合逻辑中蓝色通路)对应着输出端最晚到达的跳变信号(如图 1 虚线箭头指向的输出波形中最后一个跳变信号),决定了同步时序电路能够正常工作的最小时钟周期。

因此,要保证电路正常工作,不仅要验证其逻辑功能的正确性,而且还要验证其时序的正确性。也就是要确保任何信号传播通路的时延小于额定工作周期,使电路能在时钟脉冲到来之前稳定在正常态。换句话说,就是确保每条通路满足电路正常工作的定时约束(Timing Constraint),这也是时延测试的目标。为了达到这个目标,时延测试需要能够检测电路中潜在的时延缺陷,因为在某些输入向量下这些时延缺陷会增大相关通路的传播延迟,可在电路实速运行时破坏电路的时序,从而造成电路功能失效。

图1 同步时序电路的关键通路与时钟周期图

时延测试面临最基本的挑战性问题是电路中的通路数随电路规模呈指数增长,故对每一条通路是否满足定时约束均进行测试是不可能的[1]。工业界的做法是仅选择少量的关键通路进行测试,这就引出了另一个难题:如何寻找关键通路,使得只需要测试少量通路就足以判断整个电路是否满足定时约束。寻找关键通路之所以困难,是因为通路的时延受很多因素的影响并产生偏差。例如工艺的不稳定性会带来参数偏差,如沟道长度、阈值电压、互连线的高度和宽度等,都会影响信号的时延。又如逻辑门的输入具有不同跳变情况时会有不同的时延,不同输入向量还会造成不同的噪声环境(如电源噪声、串扰效应等),同样会影响通路的时延。

传统的时延测试方法,或者说工业界目前正在广泛使用的时延测试方法,主要采用在结构上覆盖电路结点的跳变测试(Transition Test),辅助以针对设计人员分析给出的很有限的关键功能通路的时延测试。这种情况下,对电路时延缺陷的覆盖率很难给予定量的评估。并且由于前述时延偏差的存在,设计时静态分析的关键通路与流片之后实际芯片的关键通路有很大差距,测试质量难以保障。

本文将探讨考虑时延偏差的数字电路时延测试问题。其中,在第二节分析产生时延偏差产生的原因,第三节简要给出了时延测试的基础知识,第四节具体介绍了中国科学院计算技术研究所在针对各种时延偏差问题上研究时延测试方法所取得的进展,最后总结全文。

2 时延偏差产生的原因

集成电路芯片上引起时延变化的原因有:(1)制造过程中的时延缺陷;(2)静态的工艺参数偏差;(3)由电源噪声、串扰效应、多输入跳变等引起的动态偏差;(4)芯片生命期的环境变化(如温度变化等)、单粒子效应、老化效应等。本节将分别进行介绍。

2.1 时延缺陷

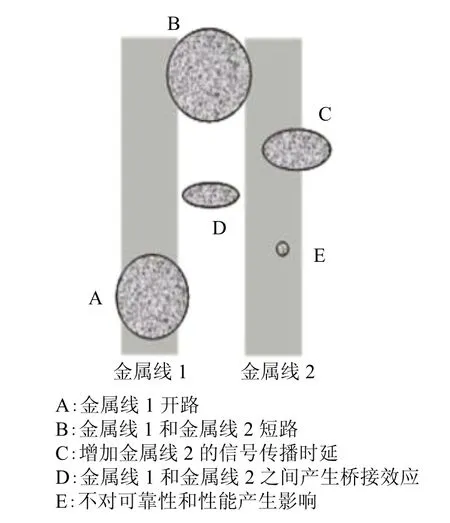

图2 两根毗邻金属线的缺陷大小与位置图

对于数字逻辑电路而言,通常只有引起时延异常增大的缺陷才被称为时延缺陷。超深亚微米工艺下,制造中的时延缺陷越来越严重。各种类型的时延缺陷包括:阻性开路与短路(Resistive Open and Short),门氧化短路(Gate Oxide Short),凹陷和阻性过孔(Unfilled and Resistive Via),桥(Bridge),开路(Open),高漏电流(High Leakage),随机粒子缺陷(Random Particle Defect),等等。图 2 显示了两根毗邻金属线间缺陷大小和位置各不相同的 5 种情况[2]。缺陷 A 会导致金属线 1 的开路故障,缺陷 B 会导致金属线 1 和金属线 2 之间的短路故障,这两种情况比较容易检测出来。对于缺陷 E,由于其大小不足以影响芯片的功能和可靠性,所以这种缺陷通常可以容忍。缺陷 C 虽然没有造成金属线 2 上的开路故障,但是它相当于在金属线 2 上增加了一个较大的电阻,使得金属线 2 的信号传输时延增加。缺陷 D 虽然没有造成金属线 1 和金属线 2 之间的短路故障,但它相当于用一个电阻将金属线 1 和金属线 2 桥接在一起,这种缺陷被称为桥接缺陷。桥接缺陷的影响与中间这个电阻的大小有关,电阻足够小时会引起功能失效,而电阻足够大时则会在金属线 1 和金属线 2 之间产生信号噪声,当电阻取中间值时会增加这 2 根金属线的传输时延。类似于 C 和 D 这样的缺陷随着工艺尺寸的缩小越来越多,它们在芯片使用过程中会由于各种老化效应逐渐演变成开路与短路故障,从而影响芯片的可靠性。由于这种缺陷对器件时延的影响较小,所以这种缺陷也被称为小时延缺陷(Small Delay Defect),它们一方面会影响芯片的可靠性,另一方面会在关键通路上累积而增大通路的时延,进而造成时延故障。

2.2 静态的工艺参数偏差

工艺偏差是指集成电路在制造过程中器件间物理参数的波动。相关文献[3]将工艺偏差分为两大类:系统偏差、非系统偏差。系统偏差是指在芯片制造过程中能够根据光学、化学等学科中已经成熟理论推断出的偏差。这部分偏差可以在芯片设计流程中进行定量的分析[4]。非系统偏差是指在芯片制造过程中引入的随机偏差。这类偏差一般通过统计学的方法来表征。非系统工艺偏差又可以分为片内偏差和片间偏差两类。其中,片间偏差指芯片与芯片间存在的全局性偏差,比如,在某一片芯片内的器件门长度整体高于其他芯片门长度的平均值;片内偏差指芯片内器件与器件间存在的局部性偏差,比如,在一个芯片内有些门长度高于平均值,而另外一些门长度低于平均值。

传统的电路制造工艺中,片间偏差是工艺参数偏差的主要偏差。由于在同一芯片上的偏差具有一致性,传统的电路设计方法通常采用考虑最优情况、最坏情况的基于边界(Corner-based)的设计方法来处理芯片间偏差的问题。通过在低电压、最恶劣工艺以及高温条件下来模拟最坏的全局环境偏差对电路定时带来的影响。然而,这种方法在纳米工艺以及高温下不再有效。片内偏差是纳米级集成电路设计出现的新问题,随着集成电路特征尺寸的缩小,同一芯片上同样的元器件在同一工作环境下呈现出不同的、随机的性能参数。所以,考虑片内偏差变得尤为重要。由于片内偏差具有相对于芯片更为“短程”的偏差,这使得传统的电路分析方法往往变得过于“悲观”,故而无法准确地考虑工艺参数偏差的影响。

130 nm 工艺节点以下线宽都已小于曝光的波长长度,这就使得曝光后制作出来的图形变形严重。尽管晶体管的特征尺寸快速降低到 65 nm、45 nm 以至32 nm,但是高昂的研制费用使得光刻工艺依然采用 193 nm 的大尺寸光波。光刻中大尺寸光波的显著干涉和衍射效应造成实际在硅片上成像的图形发生越来越大的偏差,复杂的工艺参数变化将导致互连线和器件几何尺寸(互连线的宽度 W、高度 H,晶体管的有效沟道长度、栅氧化层的厚度)及电学参数(阈值电压)的严重偏差。

国际半导体技术发展路线图指出,阈值电压电学参数的偏差在 2011 年已达到 42% 的严重偏差。这些偏差严重影响着逻辑门延迟、互连线延迟、信号跳变斜率、直至信号传播通路的时延。工艺偏差使得电路中器件的时延不再是一个确定值,而是一个服从某种统计分布的随机值。处理工艺偏差带来的影响通常采用统计定时分析(Statistical Static Timing Analysis,SSTA)的方法。2003 年的研究表明,在 180 nm 工艺时,电路的频率偏差就能达到 30%,越来越多的信号通路成为可能影响电路时延的关键通路[5]。就时延测试而言,需要针对这些关键通路生成测试向量,确定芯片能够正常工作的最小时钟周期。

2.3 动态时延偏差

动态时延偏差指与输入向量和环境相关的时延变化,主要包括:多跳变输入对门延时的影响,由串扰、电压降引起的信号完整性问题等。

工业界在特征化每个逻辑门或库单元的 pin-to-pin延迟时,一般假定其中只有一个输入信号发生跳变、而其他输入信号保持稳定。实际上,pin-to-pin 时延会受到其他输入上信号跳变的影响。因此,静态定时分析得到的通路时延是不准确的。只有当输入向量确定下来,才能准确地得到每个逻辑门实际的 pin-to-pin延迟。

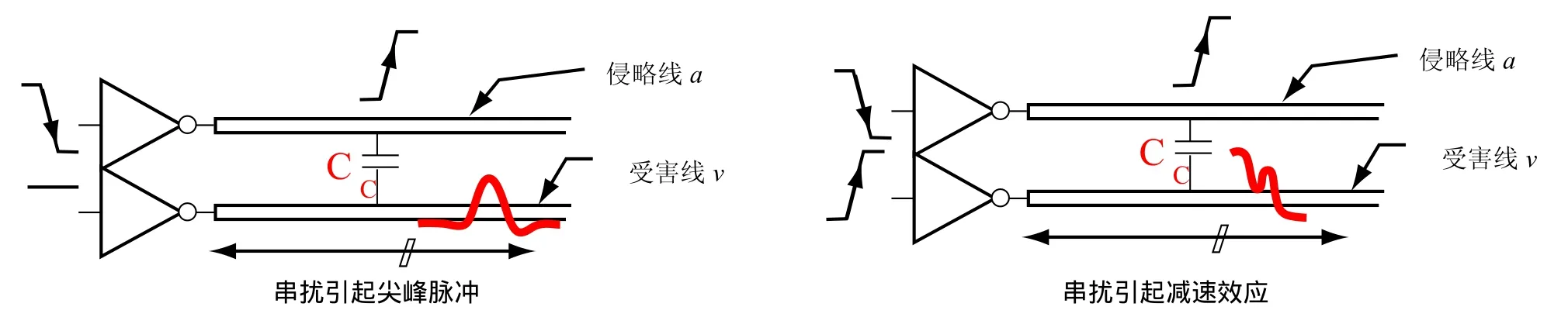

在没有输入向量的情况下,互连线的延迟也无法准确地静态估计。由于存在耦合电容,在不同的输入组合下,串扰能够在临近的两根线上引起尖峰脉冲或者减速效应,如图 3 所示。随着工艺特征尺寸的细化,互连线平面电容减小、高宽比增大、间距减小,导致串扰效应加剧。

图3 耦合电容引起的串扰效应图

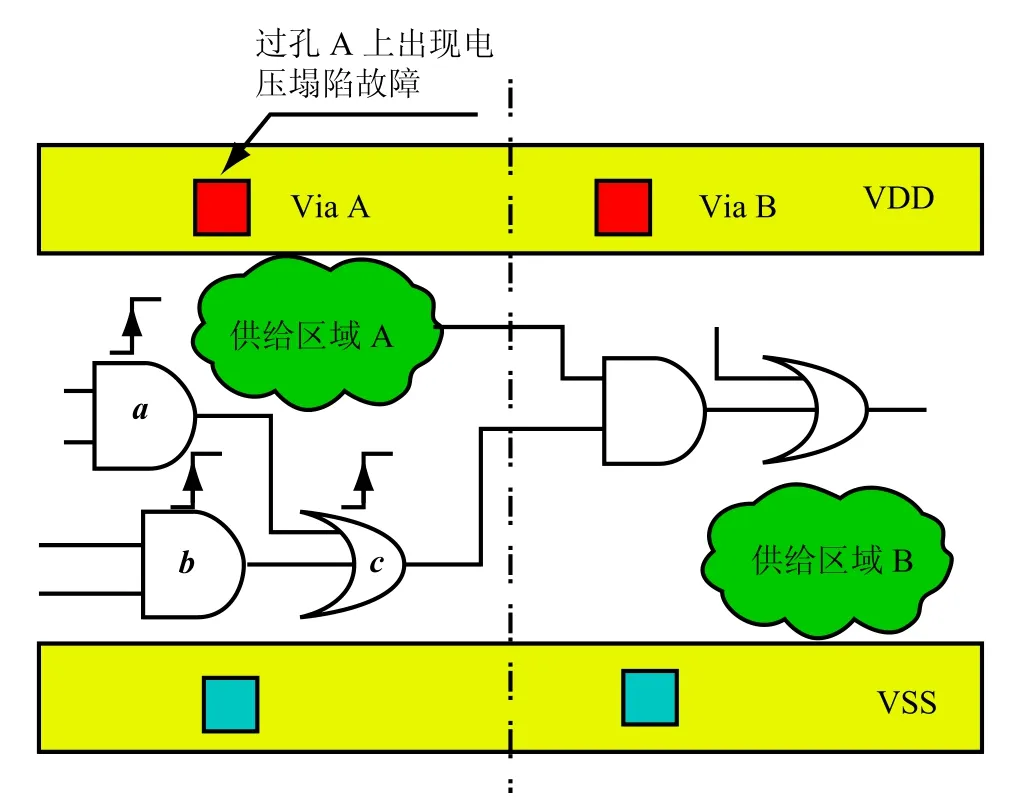

图4 局部供电区域与电压塌陷故障图

另一方面,局部供电区域中器件的信号翻转,会从供电过孔吸收或释放电流,造成电压降问题,严重时将在过孔上引起电压塌陷故障,使得该区域内的跳变时延增加,如图 4 所示[2]。 随着工艺细化,供电电压下降,器件的信号传播时延对供电电压的变化越来越敏感。2004 年 Intel 的研究表明,在 90 nm 工艺条件下,当额定电压为 0.9 V 时,实际工作电压每降低 1%,器件的传输时延增加 4%[6]。

串扰和电压降效应引起的时延问题,都可以通过时延测试来检测。

2.4 环境因素、单粒子效应与老化效应

环境中的问题也会对电路的时序造成干扰,例如温度升高会引起通路时延增大。因此测试要检测芯片正常工作的温度范围。

宇宙射线造成的单粒子瞬态错误同样会对电路时序造成影响。单粒子撞击会在存储器件中引起单粒子翻转错误(Single Event Upset,SEU),在组合逻辑中则引起单粒子瞬态错误(Single Event Transient,SET)。如果组合逻辑设计的时序余量不足,当 SET信号沿着某条关键通路传播到时序单元时,满足建立时间和保持时间,则被捕获到触发器中,造成类似于SEU 的状态翻转,如图 5 所示。进一步地,如果线间耦合电容较大或存在其他时延缺陷,串扰等引起的时延问题也会加剧时序余量不足,造成芯片抗单粒子辐照能力较弱。

图5 SET 在组合逻辑中传播图

图6 集成电路时延偏差问题的诸多来源图

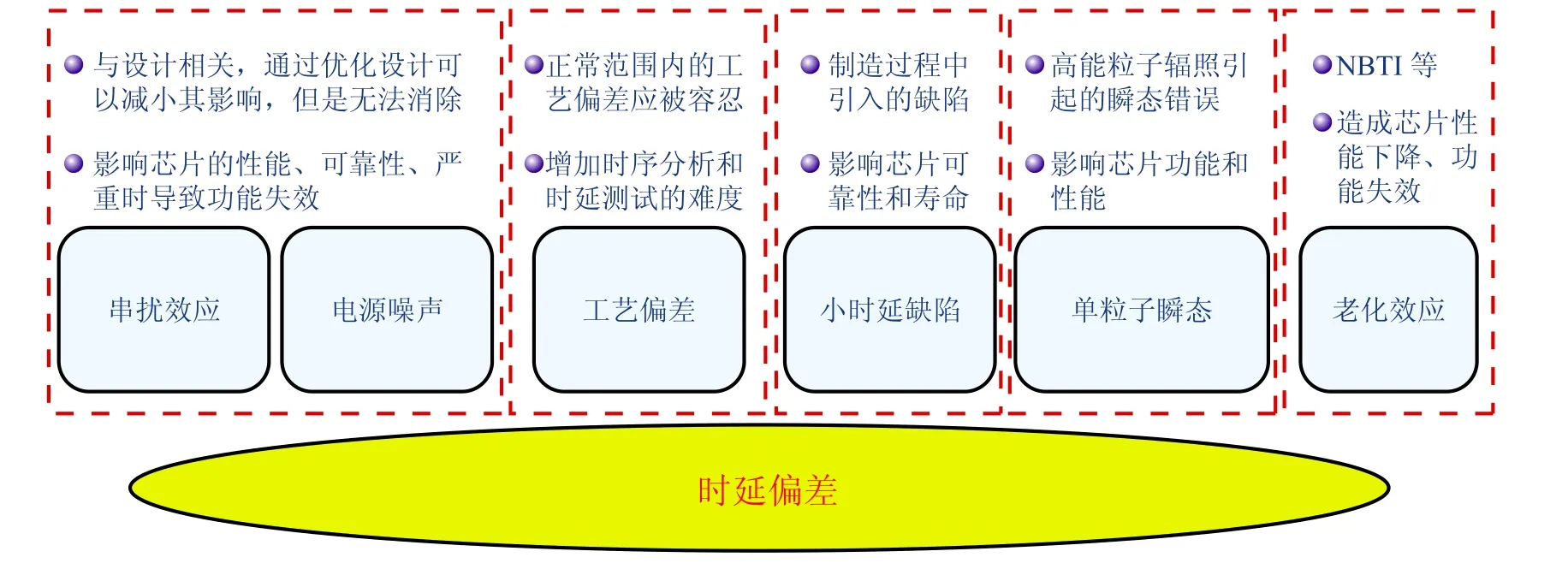

此外,电路的老化效应也会造成电路时延的增加,例如负偏置温度不稳定性(Negative Bias Temperature Instability,NBTI)效应。NBTI 是一种作用于 PMOS 晶体管的老化效应,指 PMOS 晶体管的阈值电压会随着电路运行时间的增加而不断升高,从而逐渐增加门的延迟,甚至最终导致芯片因为定时违规(Timing Violation)而出现功能失效。综上所述,时延偏差的各种来源都会或多或少地增加或改变电路的时延,除了多输入跳变作为电路设计固有的偏差之外,其他偏差来源都需要在设计与测试中有相应的对策,如图 6 所示。其中,小时延缺陷是制造过程中引入的缺陷,很难检测,但会影响芯片可靠性和寿命。串扰效应和电源噪声与设计相关,通过优化设计可以减小其影响,但是无法完全消除;它们能够影响芯片的性能和可靠性,严重时导致功能失效。正常范围内的工艺偏差应被容忍,但会增加定时分析的难度。在芯片生命期,高能粒子辐照引起的单粒子瞬态错误会影响芯片功能和性能,老化效应如 NBTI 等也会造成芯片性能下降和功能失效。这些时延偏差所引起的时延问题可造成电路时序错误和可靠性下降,因此,时延测试应该尽可能考虑所有这些因素,进行芯片性能分级和可靠性筛选。

3 时延测试基础

集成电路测试包含软件过程和机台测试过程。

软件过程中,不仅要进行测试生成,得到被测电路的输入激励,还要进行电路模拟,得到用于比较分析的正确响应。机台测试时,要使用测试仪将测试激励通过测试负载板施加到被测芯片上,并与存储在测试仪上的正确响应进行比较,判断芯片合格或者有故障。其中,测试生成决定了测试的故障覆盖率,而如何实施机台测试往往决定了测试的成本,因为提供高速的时钟信号,往往需要使用昂贵的测试仪。

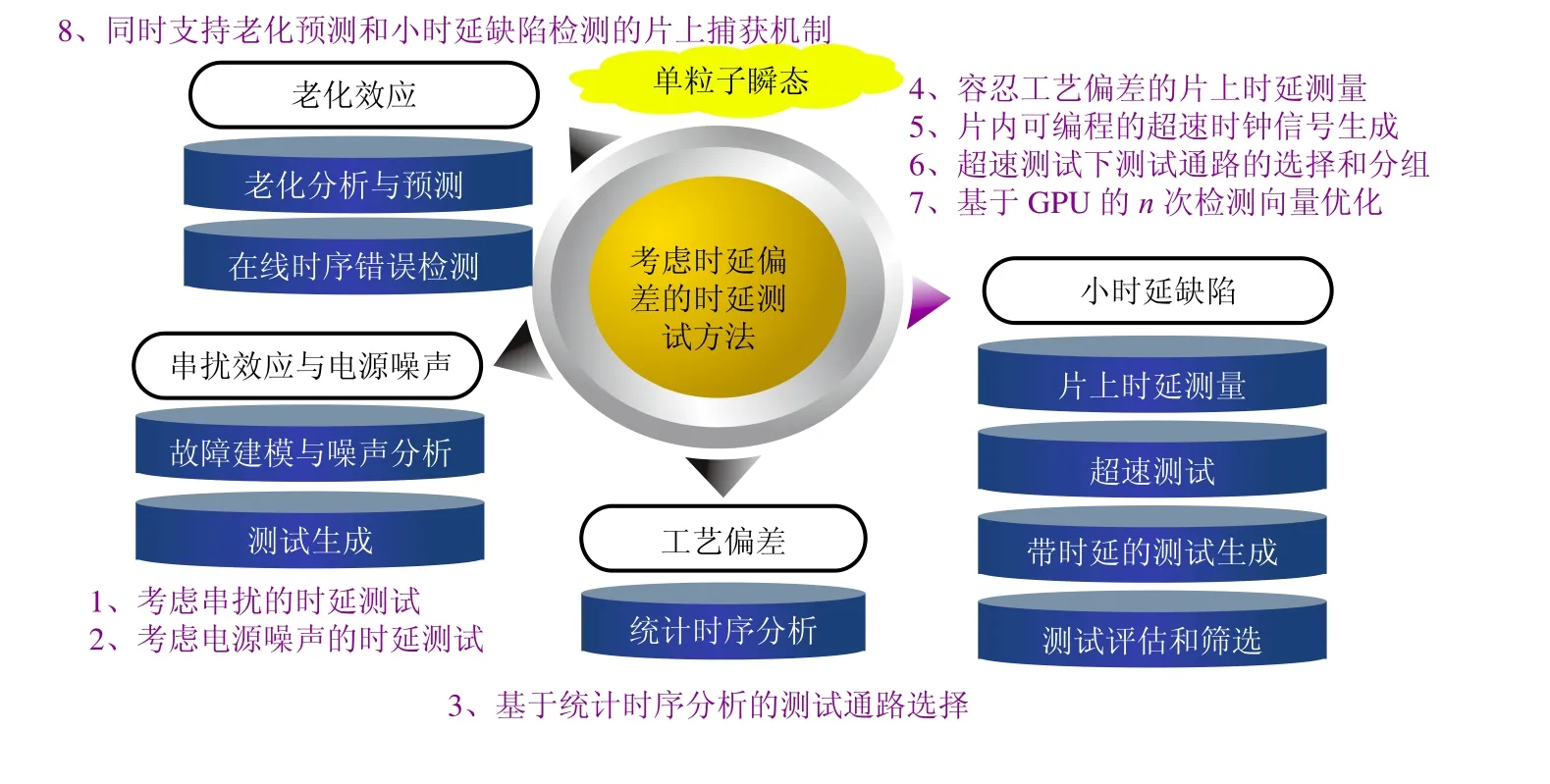

图7 考虑时延偏差的测试涉及的关键技术与相关成果图

具体到时延测试来说,测试生成需要对组合逻辑先后输入 2 个测试向量,V1 和 V2。其中,V1 将组合逻辑稳定在一定的状态,V2 则在电路中引入一个跳变,并沿着某些通路传播到组合逻辑输出,在测试周期结束时被捕获和观察,从而检测电路中可能的时延问题。时延测试的自动生成主要需要解决时延问题建模、基于电路定时分析的测试通路选择等问题。电路中的通路数与电路规模呈指数增长,因此只能对一小部分关键通路进行测试。

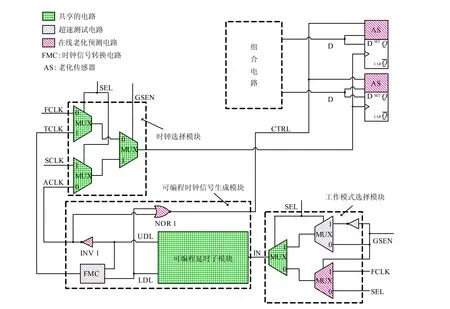

针对前面讨论的各种引起时延偏差的时延问题研究中,面向时延偏差的时延测试方法,可采用不同的技术提供解决方案。图 7 给出了目前国际上研究时延偏差的测试问题的主要方向:针对电源噪声与串扰效应,需要进行故障建模、噪声分析与测试生成;针对工艺偏差,需要进行统计定时分析;针对小时延缺陷的检测,有片上时延测量、超速测试、带时延的测试生成,测试评估和筛选等技术;针对老化效应,有分析、预测和在线时序错误检测技术。所有上述解决方案都能够提高芯片的时序可靠性,从而提高芯片的抗单粒子瞬态辐照能力。图 7 中还给出了中国科学院计算技术研究所在上述方向上开展研究所提出的八个方面的成果,在以下分别进行简述。

4 考虑时延偏差的测试方法

针对电路中的上述时延问题,在本节介绍中国科学院计算技术研究所十余年来所研究的时延测试方法。

4.1 考虑串扰的时延测试

图8 串扰故障模型的发展图

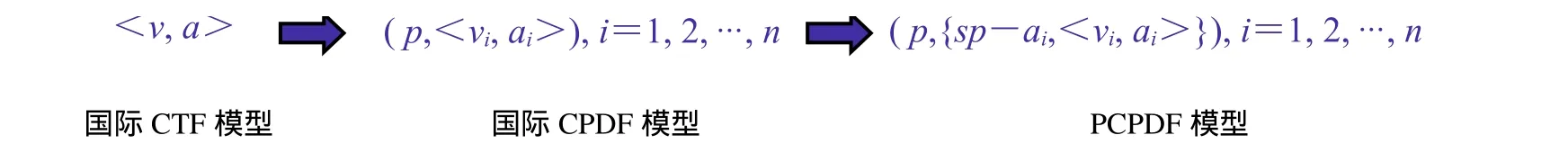

在考虑串扰效应的时延测试方法方面,中国科学院计算技术研究所在串扰故障建模和测试生成方面的多项研究逐渐形成了精确串扰源时延测试方法体系,包括:(1)提出精确串扰源通路时延故障模型(PCPDF)[7-8],统一了多串扰源时延故障的时序和逻辑约束,使得对电路时延分配的考虑只需在故障收集阶段,而不需在测试生成阶段;(2)提出基于跳变图的定时分析方法及加速策略[9-10],使用位图结构存储信号可能跳变的时刻;在与时间窗方法可比的时间复杂度下,能够有效识别后者所找到的虚假串扰源;(3)分别提出了基于结构 ATPG、可满足问题的测试生成算法[11-12],尽可能激发更多的串扰源以测试电路的最差性能,获得高质量的时延测试向量。

串扰减速效应主要表现为侵略线跳变信号干扰受害线跳变信号,引起受害线跳变时延增大。侵略线和受害线同时信号翻转才能产生严重的串扰效应。国际上先后引入了 CTF 模型[13]和 CPDF 模型[14]对串扰效应建模,但二者都仅考虑逻辑耦合,而未考虑时间耦合,导致无法精确激励串扰效应。图 8 给出了串扰故障模型的发展过程,其中 CTF 模型仅涉及侵略线 a和受害线 v 的收集,CPDF 模型考虑了受害线 vi所在的通路 p 需要是关键通路;PCPDF 模型进一步识别出了传播侵略线信号的子通路 sp-ai。PCPDF 模型在国际上首次在故障模型中引入时间参数,结合静态定时分析,通过精确激励串扰效应提高测试质量,同时将测试生成效率较国际方法提高了 1~2 个数量级。

4.2 考虑电源噪声的时延测试

电源噪声是由电路工作时器件信号发生翻转所引起的,它会增加通路信号传播时延。在芯片设计过程中,设计者往往需要评估电路中的关键通路在最坏电源噪声情况下的传播时延以指导电源网格的设计;在芯片测试过程中,当芯片要求高可靠性时,能最大化关键通路周围电源噪声的测试向量无疑可以提高测试质量。

中国科学院计算技术研究所通过对电源网格的结构特征分析得出结论:电源噪声不仅具有局部性特征,而且具有时间相关性特征。电源噪声的局部性特征表现在:对于单个器件而言,它的信号翻转所影响的范围是有限的,只会影响到它邻近供给区域内的器件。电源噪声的时间相关性特征表现在:器件翻转时所产生的电流大小与器件发生跳变的时间有关。基于电源噪声的这两个特征,中国科学院计算技术研究所在文[15]中提出了一种新的面向电源噪声的时延故障模型 PSNPDF,并给出了针对该模型的故障收集与测试生成算法。

首先,该方法使用电路中的可测关键通路来观测电源噪声引起的故障效应。这使得该方法所生成的测试向量比基于跳变时延故障模型所生成的测试向量具有更长的敏化通路,因此更容易观测出故障效应。其次,侵略子通路的选取同时考虑了电源噪声的局部性特征与时间相关性特征。为此,中国科学院计算技术研究所引入了时间窗口的概念来处理电源噪声的时间相关性特征。侵略子通路上的最后一个门要求与被测关键通路上的某一个门在同一供给区域,且在同一时间窗口内。测试生成在敏化被测关键通路的同时,也需要敏化侵略子通路上的跳变,从而激活关键通路周围的电源噪声,达到对故障效应的捕获。

这种方法简单高效,对 PSNPDF 的测试生成可以在对通常的强健测试生成算法的基础上做较少改动来实现,减少了测试生成的复杂度。基于 ISCAS’89 基准电路的实验结果表明,所收集的 PSNPDF 个数平均值为电路中 TDF 故障数平均值的 16.55%,故障集合精简,因此可以在较短的 CPU 时间内收集电路中的PSNPDF 并完成其测试生成。另外,该方法达到的平均 PSNPDF 覆盖率为 85.2%,略高于一款通用处理器芯片的跳变时延故障覆盖率[16],这说明该故障模型可以集成到现有的测试流程中,以提高测试质量。

4.3 基于统计定时分析的测试通路选择

统计时延模型和统计定时分析方法的发展[17],使得采用快速的概率分析方法而非蒙特卡洛方法来计算通路相关性[18]成为可能。中国科学院计算技术研究所在文[19-20]中采用了概率分析方法来避免枚举电路实例以及针对电路实例的分析过程,提高测试通路选择的速度。

该方法首先将测试通路选择问题转化为一个最小集合交集问题。基于统计时延模型,在多种工艺偏差构成的多维空间上,每一条测试通路 P 定义了一个空间 SP,在这个空间内通路 P 满足时延约束。给定测试通路集合 H,H 定义的空间记为 SH,表示 H 中每条通路定义的空间的交集。若SH越小,则表示 H 的测试效果越好。将测试通路集合 H 能捕获电路时延缺陷的概率定义为:

其中 dH表示 H 中最长通路的延迟,dcircuit表示电路中最长通路的延迟。

该方法使用了贪心法来得到一个较高的DFCP(H),其核心问题是对于给定的通路集合 H,计算 H 中所有通路都满足时延约束的概率 prob(dH<clk)。为了计算这个概率,采取了如下方法:

(1)H 含有一条通路:基于统计时延模型,通过概率分析中的求和(Sum)运算计算出此通路的延迟的概率密度函数,然后通过积分得到此通路满足时延约束的概率。

(2)H 含有两条通路:基于统计时延模型,分别计算出两条通路的延迟概率密度函数以及相关系数,继而得到两条通路延迟的联合概率密度函数,最后通过函数积分计算出这两条通路都满足时延约束的概率。

(3)H 含有三条通路:基于三条通路各自满足时延约束的概率和两两同时满足时延约束的概率,提出了基于集合交集上下界估算的方法和基于经验公式模拟的方法来计算三条通路同时满足时延约束的概率。第一种方法通过计算三个集合交集的上下界后取均值来估算三条通路都满足时延的概率。第二种方法首先估算三条通路中的两条通路满足时延约束对第三条通路满足时延约束的概率增量,然后根据这个增量来估算两条通路满足时第三条通路满足时延约束的条件概率,最后将这个条件概率乘以前两条通路都满足时延约束的概率就得到了三条通路都满足时延约束的概率。

(4)H 含有多条通路:通过将其中的 N-2 条通路抽象为一条通路后,调用三条通路同时满足时延约束概率的计算公式来计算 N 条通路同时满足时延约束的概率。在通路选择过程中,每次计算的概率结果都可以在后续的通路选择过程中得到复用,因此整个测试通路选择过程速度很快。计算复杂度为 O(M×N),其中 M 为候选关键通路的数目,N 为选择的测试通路的数目。

针对基准电路的实验数据表明,相比于典型的基于蒙特卡洛仿真的测试通路选择方法,该方法的计算时间降低了 1~2 个数量级,同时选择出来的测试通路集合对小时延缺陷的检测能力十分接近[20]。

4.4 容忍工艺偏差的片上时延测量

使用外部测试仪(ATE)对通路的小时延缺陷进行调试,一方面非常昂贵,另一方面调试结果的可信度将受到接口部位的寄生电阻、寄生电容以及传输线的阻抗等因素的影响。所以片上植入测量电路来测量通路时延是一种提高测量准确度、降低成本的办法,但是测量电路本身在制造过程中存在工艺偏差问题,如何能保证测试的准确性和精度?

中国科学院计算技术研究所在文[21]中提出了一种新的片内通路时延测量结构,如图 9 所示,设计了一个包含多级时延测量单元的片内通路时延测量电路。在这个设计的片内通路测量电路当中,从最后一级到第一级时延测量单元,相应每一级的测量分辨率是以2 的倍数递增。所设计的通路时延测量结构只需非常少量级数的时延测量单元就能达到一个非常大的时延测量范围。进一步地,在所提出的片内通路时延测量结构当中,还采用了一种校准电路,用来校准每一级时延测量单元在芯片制造存在工艺偏差情况下的测量分辨率。此外,被测通路引入连线之间的时延差也被进行了测量,从而可以有效地提升片内通路时延测量的精度。

图9 片内通路时延测量电路结构 OCDM 图

实验结果表明,采用该通路时延测量技术,能有效地对电路中通路的时延进行测量。在通路时延测量电路当中只需设计非常少量级数的时延测量单元就能达到一个非常大的时延测量范围,此外,还能大幅减少通路时延测量的时间开销。通过同以往基于游标延迟线的通路时延测量电路进行比较,通路时延测量电路所需要的硬件开销有大幅地降低:相同的测量范围,硬件开销仅为国际方法的 1/5,同时能有效地容忍工艺偏差。

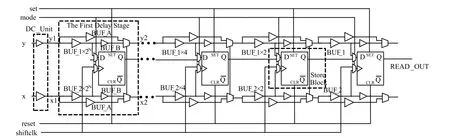

4.5 片内可编程的超速时钟信号生成

超速测试通过缩短测试通路的 slack 提高对小时延缺陷的检测能力。实现超速测试有两个关键问题,一是如何提供高频测试时钟?例如测试频率比工作频率提高 1 倍以上。使用外部测试仪不仅非常昂贵,而且对于本身就在 2 个 GHz 下工作的高速电路,几乎已经很难在外部提供更高频率的测试时钟信号了。二是如何对测试通路分组进行高频测试、并控制功耗?超频测试会带来高于正常工作的功耗,一方面会对测试的准确性造成影响,另一方面带来昂贵的封装费用、甚至造成芯片的毁坏。

为了解决第一个关键问题,中国科学院计算技术研究所在文[22]中设计了一个支持超速时延测试的电路结构——加载-捕获时钟生成器(LCCG),如图 10 所示,可通过测试向量中的控制信息对其进行配置,从而在芯片中生成一个高精度且频率可调整的测试时钟。只需要通过在 LCCG 电路设置非常少量级数的时延控制单元,就能达到一个非常大的时钟频率调控范围。此外,该结构还支持通过测试向量配置时延测试方式及其所需要的时钟信号,不仅可以支持捕获加载时延测试方式,而且还能有效地支持移位加载时延测试方式。实验结果表明,采用该结构可生成不依赖于功能时钟的高频测试时钟,其硬件开销大约相当于40 个标准的 MUX-SCAN 触发器的面积。与国际同类方法相比,该结构硬件开销较低、能够更加有效地支持电路在多种时延测试方式下进行更高频率的超速测试,也能很轻易地融入芯片设计流程当中。

4.6 超速测试下测试通路的选择和分组

针对超速测试的第二个关键问题,需要将测试向量分组提供测试频率并降低测试功耗。中国科学院计算技术研究所在文[23]中提出了一种面向超速测试的快速有效的可测通路选择方法。与国际上普遍采用的长通路分组、跳变故障测试方法不同,该方法采用了短通路分组、单通路敏化的策略,主要基于以下考虑:短通路具有较好的单通路可测性,同时能够有效地控制测试功耗,并且短通路在工艺偏差下具有更好的检测小时延缺陷能力。

该方法使用通路时延故障模型与单通路敏化约束条件来避免过高的测试功耗,并简化测试分组的难度。通路选择程序能够迅速而又准确地定位通路长度在某一个给定区间的通路,并判定其可测性。通过利用不可测通路的信息,可以大幅减少 ATPG 的调用,从而减少 CPU 运行时间。通路选择程序实现了三种不同的策略,分别是短通路优先策略、高测试质量优先策略与高测试频率优先策略,在实验中比较了这三种策略。

图10 加载-捕获时钟生成器 LCCG 图

在 ISCAS’89 电路上的实验结果表明,该方法能在较短的时间能找到一个可测通路集合,并达到平均 84% 跳变时延故障覆盖率;和实速测试下已知定时的测试生成方法相比,获得的超速测试下的测试集 SDQL 值[24]仅为前者的 10%,其意义是用统计时延质量评估的小时延缺陷的检测能力提升 10 倍,从而有效地提高了测试质量。通过使用合适的通路选择策略,可以找出更多通路长度接近测试时钟周期的可测通路,从而提高检测小时延缺陷的能力。在提出的三种策略中,高测试质量优先策略能够取得最好的测试质量,同时它的运行时间是最多的。在高测试质量优先策略中,如果增加在通路选择过程中所付出的努力,可以明显提高故障覆盖率,并且提高测试质量,同时 CPU 时间在可接受的范围内。因此,推荐使用高测试质量优先策略。

4.7 基于 GPU 的 n 次检测向量优化

除了采用考虑串扰、电源噪声、工艺偏差、小时延缺陷的测试生成技术提高时延测试的质量之外,还可以基于 n 次检测[25]的概念,通过对每个简单的跳变故障用不同的测试向量检测多次来提高未曾建模的时延故障的检测能力。但是 n 次检测测试向量集拥有与n 成线性增长的向量数,会带来生产测试无法承受的测试成本。因此,在可接受的测试成本下,对 n 次检测测试向量集进行优化和精简对于提高测试质量非常关键。

图11 在线电路老化预测和小时延缺陷检测的双功能电路图

通常测试优化技术需要反复大量调用故障模拟引擎,因而依赖于强大的故障模拟工具。中国科学院计算技术研究所在文[26]中提出并实现了基于图形处理器(Graphics Processing Unit,GPU)的 1 至 n 次检测的故障模拟器 nGFSIM,对于任一指定的整数 n可只运行一次就报出 1 到 n 次检测的故障覆盖率。nGFSIM 与同时期不采用 GPU 的商业工具相比,获得了 25 倍的加速比。基于 nGFSIM 的强大计算能力,中国科学院计算技术研究所在文[27]中提出了一种近似最长的敏化路径(ALSP)计算方法以及一种基于 GPU 的同时考虑最长敏化路径和 n 次检测覆盖率的时延测试向量选择方法,用于从不考虑时延的 n次检测测试向量集中选择出高时延测试质量且精简的测试向量集。ALSP 计算方法仅需两遍电路遍历,就可以从当前测试所检测的跳变故障集估计每个跳变故障的最长敏化路径长度。在得到 ALSP 后,可同时优化测试路径长度和 n 次检测覆盖率,从大容量不考虑时延的 n 次检测向量集中选择出一个高时延测试质量且容量小的测试向量集。实验结果表明,与商业工具产生同样大小的测试集相比,该方法选择出的测试向量集可达到更高的 1 到 n 次检测跳变时延故障覆盖率,并且具有更高的时延测试覆盖率。

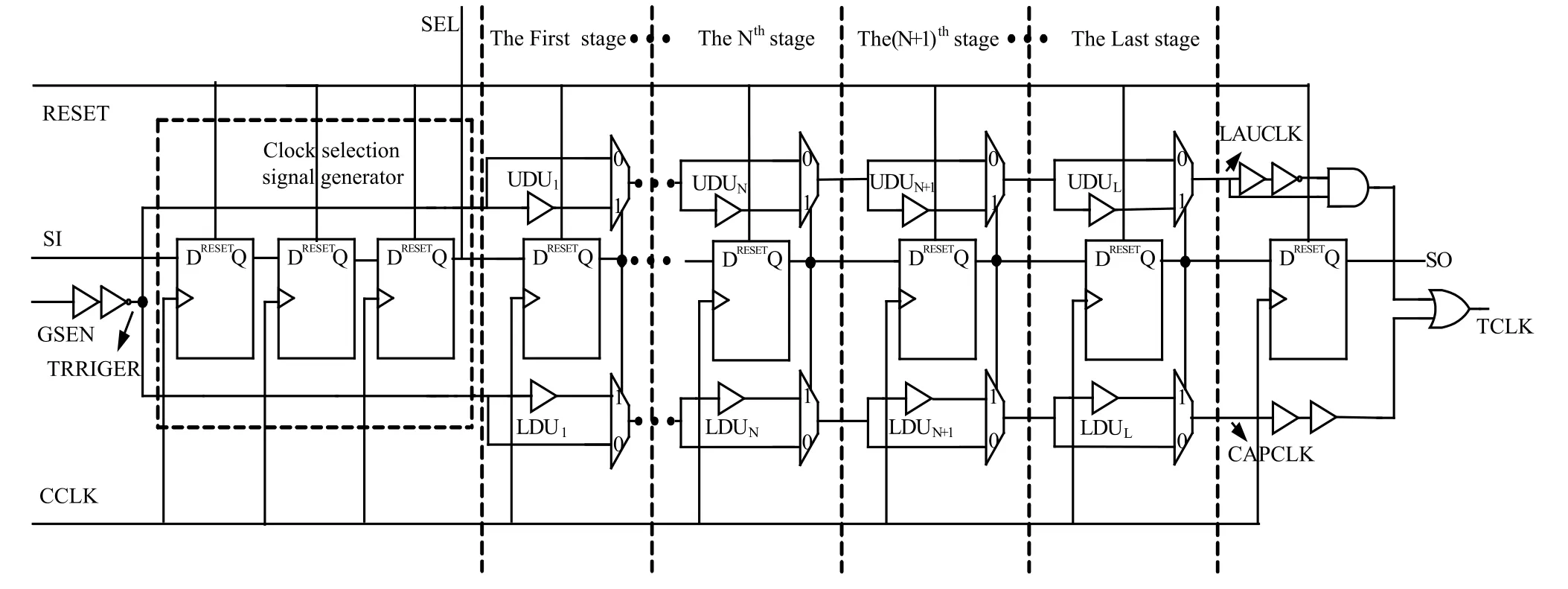

4.8 同时支持老化预测和小时延缺陷检测的片上捕获机制

在线电路老化预测和生产测试时用于检测小时延缺陷的超速时延测试均要求提前于功能时钟捕获电路的响应。基于以上考虑,中国科学院计算技术研究所在文[28]中提出了一个在线电路老化预测和小时延缺陷检测双功能的片上信号捕获电路,如图 11 所示,双功能电路由可编程时钟信号生成模块、工作模式选择模块、时钟信号选择模块、老化传感器等组成。可编程时钟信号生成模块可以为超速时延测试提供激励(Launch)和捕获(Capture)时钟信号,或者为在线电路老化预测提供时钟信号并使用这些时钟信号形成电路响应的捕获区间,其结构与图 10 类似。工作模式选择模块和时钟信号选择模块则通过两个全局信号 SEL和 GSEN 来控制,以便双功能电路在不同的工作模式间切换并且为不同的工作模式选择相应的时钟信号。AS 表示老化传感器,它可以被嵌入到与组合电路相连接的触发器里。当组合电路输出的跳变信号出现在捕获区间内时,AS 单元将产生一个报警信号,表示电路的老化已经超过了预先设定的阈值。图 11 中用绿色十字交叉线填充的模块是可以在超速时延测试和在线电路老化预测中复用的电路。

GSEN 和 SEL 信号在超速时延测试时由外部的测试仪提供,并且可以在执行在线电路老化预测操作时进行复用。当图 11 中的组合电路执行功能操作时,双功能电路处于空闲模式。在空闲模式里,双功能电路仅仅将系统功能时钟送入系统时钟树,同时自身进入抗 NBTI 老化状态。

双功能电路的抗 NBTI 老化设计使得生产测试时所用的硬件电路可以被复用到在线操作上来。同时,利用反向的短沟道效应为双功能电路设计选择最佳的晶体管沟道长度,从而最大程度地抑制了工艺偏差对于片上电路的负面影响。HSPICE 仿真结果表明,双功能电路在 10 年生命期内的老化只有 3.2%,而实现相同功能但不具备抗老化能力的电路其老化超过7.6%。另一方面,面积开销的评估结果表明,双功能电路所需总面积开销较独立地实现在线电路老化预测和超速时延测试的方案减少了近 1 倍。

5 结 语

本文首先探讨了先进制造工艺下,造成电路时序可靠性下降的时延问题。小时延缺陷的累积会影响电路时序;串扰和电源噪声越来越严重,电路时序易受环境干扰;工艺偏差使得关键通路分析变得更复杂。中国科学院计算技术研究所多年的探索表明:(1)时延测试生成需要对缺陷类型和产生原因的准确理解,结合电路布局布线和物理参数可提高测试质量;(2)为了应对工艺偏差,在统计定时分析基础上,以概率分析方法选择测试通路,可达到更完备的时延测试;(3)为提高小时延缺陷的检测能力,可采用超速测试或 n 次测试向量优化技术;(4)为了降低时延测试带来的高昂测试应用成本,可采用片上的测量或检测装置,并尽可能将用于离线测试的电路复用于电路生命期的在线检测。目前,国内外各项研究仅在一定程度上针对上述问题分别提供了解决方案。综合考虑各种时延问题、系统性地解决时延测试难题,确保芯片在工作频率下稳定可靠工作,仍然是集成电路测试领域持续的挑战。

[1]李华伟, 李晓维. 时延测试研究综述 [J]. 信息技术快报,2006, 4(1): 30-32.

[2]付祥. 面向时延偏差的测试生成方法研究 [D]. 北京: 中国科学院计算技术研究所, 2010.

[3]Blaauw D, Chopra K, Srivastava A, et al. Statistical timing analysis: from basic principles to state of the art [J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2008, 27(4): 589-607.

[4]Yang J, Capodieci L, Sylvester D. Advanced timing analysis based on post-OPC extraction of critical dimensions [C]// Proceedings of Design Automation Conference, 2005: 359-364.

[5]Borkar S, Karnik T, Narendra S, et al. Parameter variations and impact on circuits and microarchitecture[C]// Proceedings of Design Automation Conference, 2003:338-342.

[6]Tirumurti C, Kundu S, Sur-Kolay S, et al. A modeling approach for addressing power supply switching noise related failures of integrated circuits [C]//Proceedings of the Conference on Design, Automation and Test in Europe, 2004, 2: 1078-1083.

[7]Li HW, Li XW. Selection of crosstalk-induced faults in enhanced delay test [J]. Journal of Electronic Testing:Theory and Applications, 2005, 21(2): 181-195.

[8]Li HW, Zhang Y, Li XW. Delay test pattern generation considering crosstalk-induced effects [C]// Proceedings of the 12th Asian Test Symposium, 2003: 178-183.

[9]Zhang MJ, Li HW, Li XW. Multiple coupling effects oriented path delay test generation [C]// Proceedings of the 26th IEEE VLSI Test Symposium, 2008: 383-388.

[10]Li HW, Shen PF, Li XW. Robust test generation for precise crosstalk-induced path delay faults [C]// Proceedings of the 24th IEEE VLSI Test Symposium, 2006: 300-305.

[11]Zhang MJ, Li HW, Li XW. Path delay test generation toward activation of worst case coupling effects [J]. IEEE Transactions on Very Large Scale Integration Systems,2011, 19(11): 1969-1982.

[12]Shen PF, Li HW, Xu YJ, et al. Non-robust test generation for crosstalk-induced delay faults [C]// Proceedings of the 14th Asian Test Symposium, 2005: 120-125.

[13]Chen WY, Gupta SK, Breuer MA. Analytic models for crosstalk delay and pulse analysis for non-ideal inputs[C]// Proceedings of International Test Conference,1997: 809-818.

[14]Krstic A, Liou JJ, Jiang YM, et al. Delay testing considering crosstalk-induced effects [C]// Proceedings of International Test Conference, 2001: 558-567.

[15]Fu X, Li HW, Li XW. Robust test generation for power supply noise induced path delay faults [C]// Proceedings of the 2008 Asia and South Pacific Design Automation Conference, 2008: 659-662.

[16]Wang D, Fan XX, Fu X, et al. The design-for-testability features of a general purpose microprocessor [C]//Proceedings of IEEE International Test Conference, 2007:1-9.

[17]Blaauw D, Chopra K, Srivastava A, et al. Statistical timing analysis: from basic principles to state of the art [J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2008, 27(4): 589-607.

[18]Wang LC, Liou JJ, Cheng KT. Critical path selection for delay fault testing based upon a statistical timing model [J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2004, 23(11): 1550-1565.

[19]He ZJ, Lv T, Li HW, et al. Fast path selection for testing of small delay defects considering path correlations [C]// Proceedings of 28th VLSI Test Symposium, 2010: 3-8.

[20]He ZJ, Lv T, Li HW, et al. Test path selection for capturing delay failures under statistical timing model[J]. IEEE Transactions on Very Large Scale Integration Systems, 2013, 21(7): 1210-1219.

[21]Pei SW, Li HW, Li XW. A high-precision on-chip path delay measurement architecture [J]. IEEE Transactions on Very Large Scale Integration Systems, 2012, 20(9): 1565-1577.

[22]Pei SW, Li HW, Li XW. An on-chip clock generation scheme for faster-than-at-speed delay testing [C]// Proceedings of Design, Automation and Test in Europe, 2010: 1353-1356.

[23]Fu X, Li HW, Li XW. Testable path selection and grouping for faster than at-speed testing [J]. IEEE Transactions on Very Large Scale Integration Systems, 2012, 20(2):236-247.

[24]Sato Y, Hamada S, Maeda T, et al. Invisible delay quality-SDQL model lights up what could not be seen [C]// Proceedings of International Test Conference, 2005:47.1.

[25]McCluskey EJ, Tseng CW. Stuck-fault tests vs. actual defects [C]// Proceedings of International Test Conference, 2000: 336 -343.

[26]Li HW, Xu DW, Han YH, et al. nGFSIM: a GPU-based 1-ton-detection fault simulator and its applications [C]//Proceedings of International Test Conference, 2010: 343-352.

[27]Li HW, Xu DW, Cheng KT. GPU-accelerated fault simulation and its new applications [C]// Proceedings of 2011 International Symposium on VLSI Design, Automation and Test, 2011: 1-4.

[28]Jin S, Han YH, Li HW, et al. Unified capture scheme for small delay defect detection and aging prediction[J]. IEEE Transactions on Very Large Scale Integration Systems, 2013, 21(5): 821-833.