基于FPGA和SDRAM的雷电地闪探测单元存储系统设计

2013-10-27陈晓静长江大学电子信息学院湖北荆州434023

陈晓静 (长江大学电子信息学院,湖北 荆州 434023 )

李开成,李 沁 (华中科技大学电气与电子工程学院,湖北 武汉 430074)

基于FPGA和SDRAM的雷电地闪探测单元存储系统设计

陈晓静 (长江大学电子信息学院,湖北 荆州 434023 )

李开成,李 沁 (华中科技大学电气与电子工程学院,湖北 武汉 430074)

针对雷电地闪信号存储的特点,提出了基于FPGA和SDRAM的地闪探测单元存储系统的总体设计,介绍了SDRAM控制器设计中的关键问题及解决方案,给出了SDRAM接口硬件电路,详细介绍了SDRAM控制器的核心部分——时序控制器的状态转换设计,最后给出SIGNALTAPII的运行结果。实际雷电信号测试结果证明该存储系统的设计能够满足雷电地闪探测单元系统的需要。

FPGA;SDRAM;地闪探测;存储系统

雷电灾害是指雷雨云中电能释放、击中物体或所形成的强烈电磁辐射而造成损失的灾害现象。随着高科技的发展,雷电灾害越来越严重,雷电监测与气象灾害预警技术的研究显得尤为迫切。雷电地闪探测单元是全能型雷电探测设备的一个子课题,全能型雷电探测设备的研制和应用将会满足有关部门雷电监测和气象灾害预警应用的需求。雷电地闪探测单元[1]的主要任务是拾取天线接收的地闪磁场信号和大气电场信号,并提取雷电信号的特征量包括波达时间、磁场/电场峰值、方位角等信息,同时保存地闪波形数据供探测站主机读取。雷电地闪信号采集属于多通道高速数据采集,因此采用FPGA完成雷电地闪探测单元的设计。探测单元中的存储系统必不可少,因为探测站主机需要采集处理的数据不仅包括地闪信号,而且还包括云闪、光探测单元等其他信号,这些信号具有并发特性,因此要求各探测单元必须具备存储的环节,以防止主机不能及时处理数据而造成的数据丢失。考虑到雷电地闪信号采集速率高、存储容量大、存取速度快以及成本因素,地闪探测单元存储系统采用SDRAM来设计。

1 系统设计

1.1SDRAM存储容量计算及选型

根据雷电信号存储的要求,需要存储至少10次雷电闪击的数据,每次闪击包括雷电特征量和三通道的波形数据。雷电特征量包括波达时间、方位角、磁场/电场峰值等,每次闪击特征量占用空间不到100字,所以1K字的存储空间足以存放10次闪击的雷电特征量。三通道包括两路从正交环天线输入的磁场信号,一路从平板电场天线输入的大气电场信号。波形数据所占容量大小与通道数、通道采样率、采样位宽、采样时间有关,地闪信号频率覆盖范围在300kHz以下,并考虑留有裕量,探测单元的采样频率定为2MHz,采样时间应保证能完整保存全部闪击的波形,1s的采样时间足以满足要求。按照采样频率2MHz,采样位宽14bits(约2字节),3通道,1s采样时间,10次闪击计算,需要存储容量大小为2×3×2M×10字节=120M字节。

该设计选用SDRAM型号为MT48LC32M16A2❶512MbSDRAMfront.fm.rev.L 10/07 EN.Micron Technology,2000.,该芯片的主要特点为:3.3V电源供电,工作频率133MHz,所有信号传输在系统时钟的上升沿进行,内部采用流水线技术,列地址可以在任何时钟周期内改变,可被配置为猝发长度为1、2、4、8或整页猝发读写模式,具有自刷新节电功能,可实现自动预充电,行刷新周期64ms,133MHz工作频率下CAS延时为5.4ns,芯片位宽为16bits,存储体共有4个BANKS,每个BANK有8192(213)ROWS,每个ROW有1024个(210)COLUMNS,1片MT48LC32M16A2容量大小为32M字,则2片可满足要求。

1.2SDRAM控制器设计需解决的关键问题和总体设计

1)SDRAM控制器设计需解决的关键问题 SDRAM控制器是基于FPGA平台实现,FPGA选用StratixII公司的EP2S60F672*Stratix II Device Handbook,volume 1.Altera Corporation,2007.,该型号的FPGA内部包括24176个ALMS,48352个ALUTS,2544192 bits 的RAM,36个DSP模块,144个18bits×18bits的乘法器,4个enhanced PLLs,8个fast PLLS,718个I/O口,足以满足雷电信号的采集和处理的要求。 SDRAM控制器要完成3通道16位的数据存储及读取的控制,其设计需解决以下关键问题。

设计关键问题1:采集字长和存储字长不匹配的问题。雷电地闪探测单元需要并行采集3个通道,每个通道位宽16bits,而两片MT48LC32M16A2并行连接组成的位宽为32bits,某一时刻只能并行存储2个通道的数据,因此存在采集字长和存储字长不匹配的问题。解决方法是采用缓存和分时存储的办法。为每个通道设计一个FIFO缓存器,采集的数据首先放入缓存,写SDRAM时先并行存入通道0和通道1的FIFO缓存数据,之后再存入通道2的FIFO缓存数据,从而达到了较快的采集速率,充分利用了存储容量,并解决了字长匹配问题。

设计关键问题2:通道数据存放格式。为简化FPGA程序的设计,通道数据在SDRAM中的存放需遵循一定的规律,如表1所示。设计在BANK0的ROW0行中存放雷电特征量共占用1024个双字单元,从ROW1开始所有单元全部存放波形数据。每个ROW的前512COLUMS存放通道0和通道1的数据,其中通道0占低字单元,通道1占高字单元,后512COLUMS存放通道2的数据,通道2占低字单元,高字单元为无关随机数。每次闪击的采样时间为1s,按2MHz采样速率计算需要2000000/512=3906ROWS存放。

图1 SDRAM控制器设计框图

设计关键问题3:通道数据的读取。通道数据的读取在PCI总线读命令下启动,其读取要遵循通道数据存放规律,通道0和通道1的数据能够并行输出组成32bits,通道2存放地址与其他两通道不同,所以需要分时输出。可设计2个容量为1k字的READ FIFO,一个READ FIFO用于缓冲存储器的低字单元数据,包括分时出现的通道0和通道2的数据,另一个READ FIFO用于缓冲存储器的高字单元数据,包括通道1的数据。FIFO输出数据再送入PCI控制单元被PCI总线所读取。

2)SDRAM控制器总体设计 控制器设计框图如图1所示,设计结构包括3个容量为1k字的WRITE FIFO,2个容量为1k字的READ FIFO,1个时序控制器模块,1个SDRAM驱动模块以及特征量提取单元:WRITE FIFO[2]起缓存数据的作用,解决采集字长和存储字长不匹配的问题以及采样速率10MHz和SDRAM存储速率133MHz不同的矛盾;READ FIFO也是起缓存数据的作用,解决了SDRAM读取速率133MHz和PCI总线读取速率50M不同的矛盾;SDRAM驱动模块完成命令、地址译码的功能*SDR SDRAM Controller White Paper. Altera Corporation,2000.;时序控制器模块用于产生协调各部分模块工作的时序控制信号,是SDRAM控制器设计的核心;特征量提取单元用于提取雷电信号的特征量包括波达时间、磁场/电场峰值、方位角等信息,该单元与波形存储模块并行工作,当波形采集完后,各特征量也提取完毕,并按数据存放格式的要求存放在存储器的ROW0单元。

1.3SDRAM接口硬件设计

存储系统由2片MT48LC32M16A2并行连接组成,如图2所示,其中MT48LC32M16A2(1)用于存放低字,MT48LC32M16A2(2)用于存放高字,2片使用共同的地址线和控制线,不同的数据线和数据屏蔽线,组成容量为32M×32bits的存储系统。其中的地址线SA是行地址列地址分时复用线,行地址线占SA0~SA12,列地址线占SA0~SA9,地址线BA包括BA0~BA1。

1.4时序控制器的FPGA设计

图2 SDRAM接口硬件设计

图3 SDRAM时序控制器的状态转换图

时序控制器模块用于产生协调各部分模块工作的时序控制信号,是SDRAM控制器设计的核心,其状态转换图设计如图3所示。系统复位后,首先进入状态1即SDRAM初始化状态,执行一些SDRAM能正常读写所需要的一些预操作包括预充电、载入模式字、载入寄存器2的值以及载入寄存器1的值等,初始化完毕后进入状态6即SDRAM刷新状态,同时对磁场信号的峰值大小进行判断,超过阈值(标志thrld=1)并符合地闪雷电特征,则认为雷电数据到来,使能WRITE FIFO的写操作并维持1s的雷电采样时间长度,当WRITE FIFO半满标志halfen=1时进入状态2,即块写SDRAM波形数据状态,此状态下进行2次分时块写SDRAM某一行的操作,第1次将2个磁场通道的WRITE FIFO中32位数据并行直通式写入某行的前512列,第二次将电场通道的WRITE FIFO中的16位数据高位补0后补齐32位数据,直通式写入某行的后512列,行地址从1开始。状态2完毕后进入SDRAM刷新状态7,当WRITE FIFO半满标志halfen=1时再次进入状态2,重复上述过程,当写完3906行后(1s采样过程结束,标志nrdsts=1),进入状态3,即块写SDRAM特征量状态,此状态下将把特征提取模块所获得的所有特征量写入SDRAM的行0,行地址为0。状态3完毕后返回SDRAM刷新状态7,延时后进入状态4即块读SDRAM特征量状态,将SDRAM的行0中存放的特征量读出至READ FIFO中,保证PCI局部总线控制模块读取时不为空。状态4完毕后,SDRAM控制器通过PCI总线向主机发送一中断信号,通知主机有雷电数据到来可以进行读取数据的操作。主机在合适的时候进行读READ FIFO操作,若READ FIFO被读为半空状态(标志halfnullen=1),则状态7切换到状态5,即块读SDRAM波形数据状态,此状态下进行2次分时块读SDRAM的操作,第一次将某行的前512列读出至2个READ FIFO,数据宽度为32位,第2次将某行的后512列读出至1个READ FIFO,高16位数据为无关数,直到读完所有3906行为止(标志位allend=1),重新返回等待雷电数据来到的状态6。由于READ FIFO的写入速率远大于读出速率,所以不会出现被读空或写满的情况。

2 SIGNALTAPII运行结果

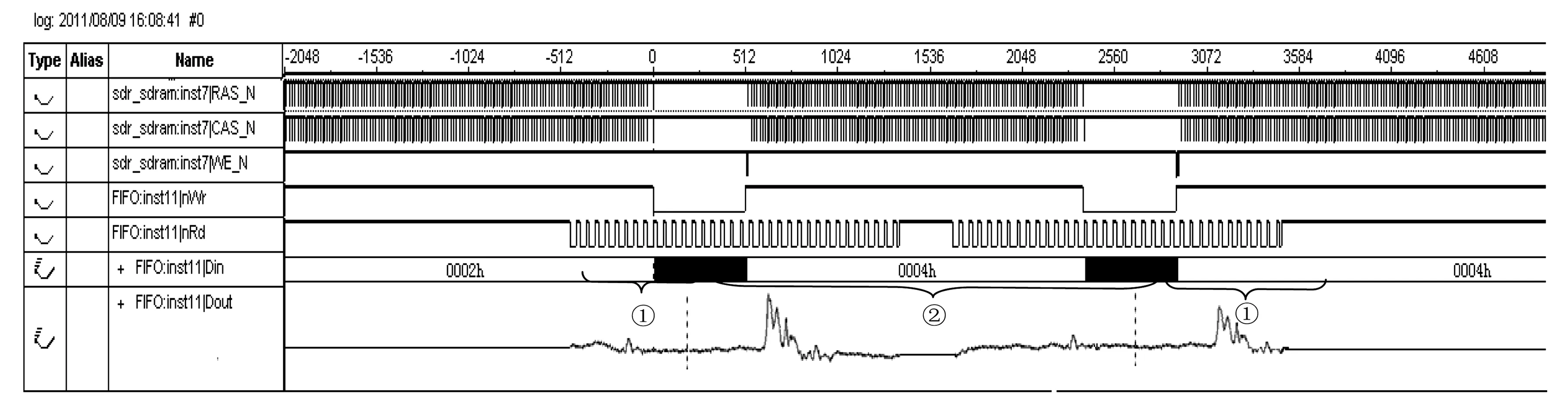

由雷电采集硬件平台完成对雷电信号的前置放大、滤波处理,当检测到有过阈值且符合地闪雷电特征的信号产生时,启动探测单元的存储系统开始工作。以下是采用QuartusII软件测试到的SDRAM的工作情况(见图4):

(1)观察从SDRAM中读出的通道0(磁场通道1,如①所示)和通道2(电场通道,如②所示)的数据波形。观察节点包括SDRAM的控制信号RAS_N、CAS_N、WE_N,以及READ FIFO的写读控制信号nwr、nrd,输入数据信号Din,输出数据信号Dout,其中nrd信号来源于PCI控制单元[3]。 从图4可以看出SDRAM在PCI总线的读控制命令下能够正确读出结果,每次读操作实现了512个数据的传输,并成功实现了通道0和通道2的分时传输。

图4 从SDRAM中读出的通道0和通道2数据波形

(2)观察PCI总线上的3路波形。观察节点包括READ FIFO的数据输出,图5显示实现了通道0(磁场通道1)和通道1(磁场通道2,如③所示)并行传输,通道2(电场通道)分时传输。

图5 PCI总线上的3路波形

3 结 语

在分析雷电信号存储特点的基础上,提出了SDRAM控制器设计需要解决的关键问题以及具体的控制器设计方案,最后用实际雷电信号测试了存储单元的工作性能,试验证明该存储系统的设计能够满足雷电地闪探测单元系统的需要。

[1]陈晓静,李开成,张明,等.雷电地闪探测单元的研制[J].电测与仪表,2012,49(5):52-55.

[2]高子旺,顾美康.一种基于FPGA的低复杂度SDRAM控制器实现方法[J].计算机与数字工程,2010,38(1):194-196.

[3]王诚,吴继华.Altera FPGA/CPLD设计(基础篇、高级篇)[M].北京:人民邮电出版社,2005.

2013-01-12

国家自然科学基金项目(51077058)。

陈晓静(1980-),女,讲师,博士生,现主要从事电磁测量与仪器方面的研究工作。

TP334.7

A

1673-1409(2013)19-0071-04

[编辑] 洪云飞