基于FPGA的HDB3译码器设计与仿真

2013-10-27佘新平许鹏甲长江大学电子信息学院湖北荆州434023

佘新平,许鹏甲,梁 浩 (长江大学电子信息学院,湖北 荆州 434023)

基于FPGA的HDB3译码器设计与仿真

佘新平,许鹏甲,梁 浩 (长江大学电子信息学院,湖北 荆州 434023)

HDB3码(三阶高密度双极性码)是基带传输码型之一,其具有编码规则简单、无直流分量、低频分量少、连0数不超过3个、提取同步方便等优点,有利于信号的恢复和检验。在石油井下信号的传输过程中,使用基于FPGA的HDB3编译码方式有利于改善传统方法所采用的曼彻斯特编码方式带来的地面解码电路复杂的问题。提出了HDB3码的译码思想,并利用FPGA软件仿真实现了HDB3译码。

三阶高密度双极性码;编码;译码; FPGA

随着科学技术的不断发展,数字通信在日常生活中到处可见,在数字通信中编译码器的应用更是广泛。译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。大多数编译码器是有损的,目的是为了得到更大的压缩比和更小的文件大小。而HDB3码因具有无直流成分,低频成分和连0个数最多不超过3个等明显优点,具有时钟恢复和更好的抗干扰性能,这使它更适合于长距离信道传输。传统的石油井下信号在传输过程中通常采用曼彻斯特编码方式,HDB3码远比曼侧斯特编码方式简单,同时HDB3码具有较强的检错能力,是基带电信设备之间进行基带传输的主要码型之一。

1 HDB3编码算法的基本编程思想

首先定义输入码元的长度,在输入的源码中,当码元位置为1时,如果上一个非0符号为正,则下一个非0符号为负,HDB3码输出为“-1”,反之下一个非0符号为正,HDB3码输出为“+1”,与此同时,计零标志位清零,数1标志位将数1的个数累加。HDB3译码算法的编程思想同编码思想一样,也需要对输入的HDB3码定义输入码元长度。在进行译码时,如果HDB3码的当前位置码元与上一个非0符号相同,则将当前代码的位置及其前面的非0符号位一并清0;否则,源码照常输出,如果源码位置为“-1”,全部变为“+1”输出。

表1 HDB3译码举例

2 HDB3码的译码规则

HDB3码的译码是编码的逆过程,其译码相对于编码较简单。根据HDB3码的编码规则,第一个V符号不可能出现在前3个位置,即每一个破坏符号V总是与前一非0符号同极性[1],这就保证了后面的代码位置减3有意义而且不会溢出。因此,从收到的HDB3码序列中,容易识别V符号,同时也肯定V符号及其前面的3个符号必是连0符号,于是可恢复成4个连0码,然后再将所有的-1变成+1后便得到原消息代码(见表1)[2]。

3 HDB3译码器的设计

3.1设计思路

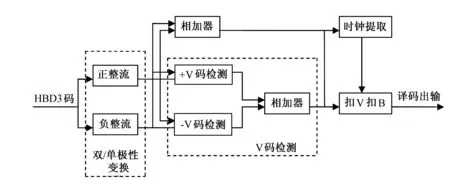

若要处理HDB3码,则需要先将其双极性转换成适合FPGA的单极性。且外接整流电路,将HDB3码分解为分别代表其正负脉冲的正脉冲序列和负脉冲序列,同时处理2列脉冲,利用其相关性检测破坏符V是否存在。若检测出V,则要对其前3个码进行清零处理,需要把前3个码存储起来作延时输出[3]。

图1 HDB3译码器模型

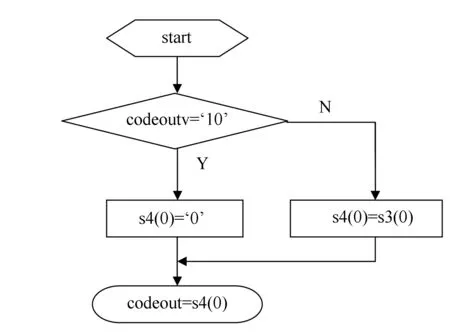

图2 V码、误码检测程序流程图

经过整流电路的处理,把HDB3码分成2列序列,一列只含有正脉冲编码,另一列则只含有负脉冲编码。同时对2条脉冲进行检测,检查任一条脉冲序列2个相邻之间的传输时间内,另一个脉冲序列是否有脉冲存在,如果没有脉冲存在,则说明被检查的序列存在破坏符V,且为2个相邻脉冲的后一个脉冲。通过V的检测后可以把2序列相加在一起,以单极性输出。若判断出V的存在,就把V和前3个码都清零。在没有误码情况下,B只会以B00V的形式出现,因此出现V时,不管是否有B,只需要将前面3位清零即可实现译码操作。

3.2设计建模

HDB3译码器模型如图1所示。相加器就是一个或操作,V码检测模块若检出V码便会向后面的扣V扣B模块的寄存器输出一个清零信号,最后输出NRZ码。把相加器与V码检测合成一个模块,加入n连0的检测。由编译码规则可知,HDB3码不可能有4连0出现。若检测出4连0吗,即为误码,还有2个相邻同极性脉冲之间的连0数必定是2或3[4],否则必有误码。

图3 扣V码/扣B码的流程

1) V码、误码检测 把经过双/单极性转换的2列脉冲信号以一个2位逻辑向量codein标识,即codein=“00”代表无脉冲,“01”代表有正脉冲输入,“10”代表有负脉冲输入。用flagzf标识前一个脉冲的正负极性,flag=0为正,flag=1为负,以判断相邻2脉冲的极性是否相同来判断出有没有破坏符V的存在。n连0的检测与编码器相似,若检出4连0或2相邻脉冲为同极性但它们之间的连零数不符合要求(不是2或3),则发现错误提示(coderror=‘1’)。V码、误码检测程序在接收到第一个脉冲后(zf=1)才开始执行,之前的输出都为0。其程序流程如图2所示,其中用cnt0记录连0的情况, 用codein表示待编码的输入信号,codeoutv为输出V码情况,coderror=‘1’为错误提示。

2)扣V码/扣B码的实现 这个模块的工作比较简单,把V码、误码检测模块的输出codeout的低位加到4位移位寄存器作延时输出,对输入进行分析,若是‘10’,即有破坏符V,把寄存器最后一位清零输出,反之,则按原样输出。程序流程如图3所示。

4 软件仿真

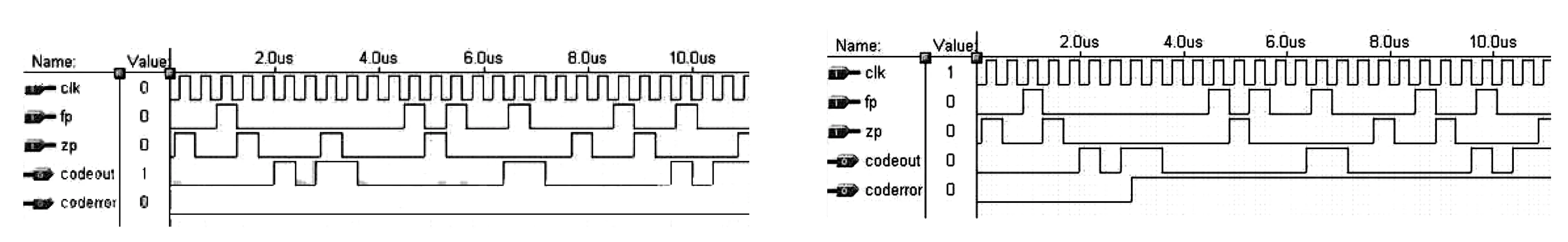

运用QuartusⅡ对编写好的VHDL程序进行仿真,仿真结果如图4所示。

参考编码器的输出结果,编码器的“-1”由11表示,而译码器的“-1”由10表示,用10替换11,把编码器的输出结果作为译码器的输入。分析仿真结果,输出相对输入有4个半周期的延时,这同样是由于HDB3码的编译码规则所致。不包括延时,其输出为10110000000110000001,结果与编码器的输入一致,说明译码器的译码功能正确。分别对译码器的检错能力做测试,结果如图5~7所示。

图4 HDB3码译码器仿真波形 图5 HDB3码译码器检测长连0的仿真

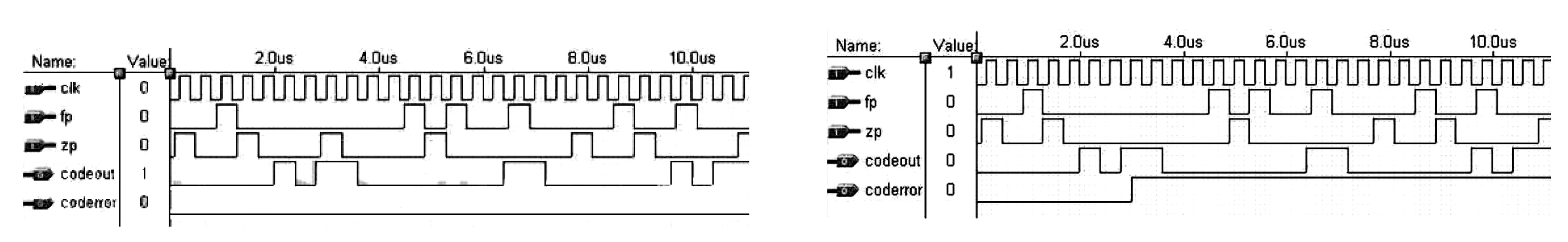

图6 HDB3码译码器检测同极性“11”的仿真 图7 HDB3码译码器检测同极性“101”的仿真

因为HDB3码连0数不可能多于3个,相邻2脉冲若同极性,其之间的连0数应为2或3,因此若检查出码流中有超出3个连0,同极性“11”或“101”即为误码。图5为长连0检查,图6为同极性“11”的检测,图7为同极性“101”的检测。当有误码被检出,coderror为1。由检错的仿真结果可知,设计的译码器能检出HDB3的部分误码。若有误码被检出,coderror为1,且之后的译码结果也不可能正确,所以用户可以根据检错提示进行相应操作。例如,当译码器检测出误码时,请求发信端把出错的码流段重发。

[1]蒋青,吕翔.一种基于FPGA技术HDB3译码器的设计[J].微电子学,2007,37(2):298-300.

[2]敖天勇,侯卫周,杨毅,等.基于CPLD的HDB3码编译码器设计[J].山西电子技术,2007(2):5-7.

[3]汉泽西,孙燕妮.基于FPGA的HDB3译码器[J].电子科技,2007(3):66-69.

[4]乔继红,顾伟娟.基于CPLD的HDB3码编译码器的设计[J].北京工商大学学报(自然科学版),2005,23(1):50-52.

2012-12-24

中国石油科技创新基金项目(2011D-5006-0302)。

佘新平(1964-),男,硕士,副教授,现主要从事天线通信技术方面的教学与研究工作。

TN96

A

1673-1409(2013)07-0037-03

[编辑] 洪云飞