一种基于高性能DSP的雷达视频处理平台

2013-10-24曲伟

曲伟

(中国船舶重工集团公司江苏自动化研究所,江苏 连云港 222061)

雷达视频信息的压缩与传输是雷达数据处理的重要环节,它将来自雷达接收机中的目标信息回波视频信号进行采样、压缩与传输,在显控台中进行图形图像叠加,实现多窗口画面一次信息与二次信息的综合显示,获取敌我态势、目标运动参数、系统运行状态等大量信息,辅助指挥员做出判断和决策[1]。

针对雷达视频数字化、传输网络化的发展趋势,本文基于最新大规模逻辑FPGA和高性能DSP芯片,结合图像处理理论,对雷达视频回波信号进行数字化采集、压缩与网络化传输,并对适用雷达图像的压缩算法进行了算法验证,为今后研究基于雷达视频目标回波信号的目标检测、特征研究和模式识别等提供了依据,以适应雷达视频处理通用性和可扩展性发展的要求。

1 平台设计

1.1 总体框架

雷达视频处理具有如下特点:

(1)采样速率高:雷达是靠天线按一定的方向特性做360°旋转,每间隔一定的角度向空间发射电磁波,电磁波在传输途中遇到目标后产生二次辐射,其中一部分返回雷达处 (称为回波),由此可以获取目标的空间坐标、速度、特征等信息。由于电磁波按照光速传播,且目标尺寸可变(最小几米),因此要求视频信号采样足够高,不能丢失目标。

(2)数据处理负荷任务重:按照每秒4 096个方位,每个方位5 000个采样点,256级量化(8 bit),则需要处理数据为 4 096×512×8=160 Mb/s,数据量大且集中。 为此,需要进行数据组织等预处理工作,合理设计软件与硬件分工,优化数据处理流程,便于传输[2]。

(3)强实时性:由于军用与民用雷达应用实时性的要求,必须设计高速率的数据传输通道,对雷达视频信号庞大的数据量进行压缩,减少传输数量,提高通信速度,实现目标实时显示、辅助决策。

结合以上特点,基于高性能DSP和FPGA构建了雷达视频压缩与传输平台,系统设计的原理框图如图1所示。

每个平台支持一部雷达视频信号,每部雷达接口信号包括二路模拟视频(对海、对空等)与三路脉冲信号(正北、触发、方位等)。模拟信号经过高速A/D变换后,以数字信号输入到FPGA中。FPGA对模拟视频信号与脉冲信号进行同步采样,对数据进行重组。DSP通过EMIF接口获取每帧数据,缓存压缩后,通过以太网进行网络发送。

1.2 数据采样

本平台距离分辨率达到2 m,A/D转换器的采样频率需要达到75 MHz。平台采用模拟器件公司的高速低功耗的芯片AD9215作为模数转换芯片,1 Vp-p差分输入信号幅度,线性数据编码格式输出,最高采样频率达到105 MHz。AD9215采样时钟由FPGA内部锁相环提供,软件控制时钟采样频率。最高设定频率75 MHz,基本量化距离为2 m。

平台面向的并不是微弱小信号,因此3路雷达模拟信号经无源阻抗匹配网络衰减后,直接进入模数转换器进行模数转换。

1.3 FPGA数据处理

由于雷达视频信号中含有大量的杂波,并且具有较强的随机特性,如果不先对其进行一定的处理,DSP高速并行处理能力将受到限制,且直接影响雷达视频处理的实时性。为此,需要FPGA对雷达视频信号进行处理。FPGA设计框图如图2所示。

FPGA选用Altera公司的Stratix II系列EP2S30F672C4N芯片[3],主要资源应用如下:

(1)时序控制与通信接口∶使用内部33 KB逻辑单元(LE);

(2)片内时钟树设计并输出A/D采样时钟:使用内置增强型PLL锁相环与快速PLL锁相环;

(3)双端口RAM数据缓存:使用嵌入式内存块,器件内存总量为1.3 MB。

雷达模拟视频信号通过A/D变换为原始雷达数字视频信号,与其他3路脉冲雷达信号一起送入FPGA。通过FPGA的可编程电路进行时序控制和预处理,同时产生地址和控制信号,从而将数字视频信号送入双口RAM的指定地址,便于DSP进行读取。

双口RAM存储器容量为16 KB,使用时分为上下两个体,各8 KB,轮流写入采样后的视频。为防止小目标丢失,须设定采样频率75 MHz,基本量化距离为2 m;由于RAM存储容量限制,如果直接把数据存入RAM中,那么采样距离只有8 km×2=16 km。为此,在FPGA中对数据进行10选1处理。在连续采样10点中统计最大值,存入RAM。采样距离为 8 km×2×10=160 km。如果需要提高采样距离,则可以降低采样频率(15 MHz,10 m精度)或提高统计极值长度(如 20∶1,320 km)。

FPGA按照乒乓模式缓存数据一帧,同步采样模拟视频信号与脉冲信号,数据重组,降低DSP工作负荷,充分发挥其信号处理特长,提高实时性。

1.4 数据压缩与网络发送

(1)DSP数据处理硬件平台

DSP通过EMIF接口从FPGA读取视频数据,并进行缓存压缩,然后通过以太网发送视频数据。处理流程如下:

DSP芯片选用 TI公司的 TMS320C6455BZTZ,该芯片属于高速定点数字信号处理芯片。为提高实时性,本设计中选用1.2 GHz最高运行时钟,内置大容量一级缓存、二级缓存与 ROM,该芯片可以满足视频压缩、解压缩技术指标的要求。TMS320C6455BZTZ具有64位外部总线,可外接引导用Flash,并可实现与FPGA芯片的数据传输;内置DDR2内存控制器(DDR2 533),总线16 bit/32 bit可选,可用于连接DDR2内存,缓存图像数据;内置 10/100/1 000 Mb/s以太网介质访问控制器(EMAC), 可 以 支 持 MII、RMII、GMII和 RGMII等 多种网络接口,扩展系统的功能,满足设计需要[4]。 DSP处理流程如图3所示。

图3 DSP处理流程

网络芯片负责将压缩视频数据传送到交换机或显控台,选择Intel公司的PHY芯片LXT971ALE,支持10BASE-T/100BASE-TX网络模式,外接隔离变压器,可以满足本设计中百兆以太网的要求。

(2)雷达视频实时压缩算法

雷达视频回波信息中包含大量的冗余数据[2],主要体现陆地、岛屿等静态物体的回波,通过雷达显示图像为各帧之间不变的像素;雷达数据中噪声和杂波较多,占总数据量的80%以上;运动物体的回波在相邻几次扫描中位移变化很小,通常会有相当的部分重叠,在视频图像上各帧间图像的变化很少,甚至只有几个像素差别。

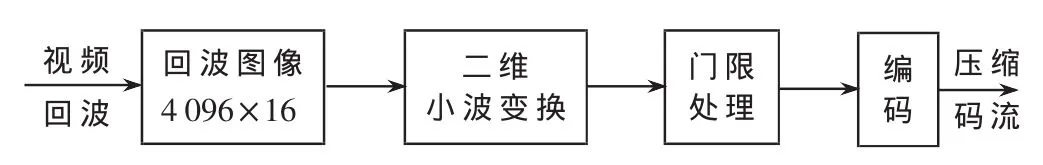

利用雷达视频信号的空间和时间相关性特点,对雷达视频信号进行二维压缩,把N个相邻的方位角数据组成一幅M×N的回波图像进行压缩,其中M为一个方位角上视频回波信号采样点数。压缩算法采用小波变换,具有多分辨分析能力,与实际雷达多量程P显、粗A显示、精A显示等,由全貌到细致、由粗到精的显示方式相一致。视频网络中的不同显控终端可以以各自不同的分辨率来观察其视频图像。压缩实现框图如图4所示。

图4 压缩实现途径

各部分实现方法如下:

(1)二维小波变换

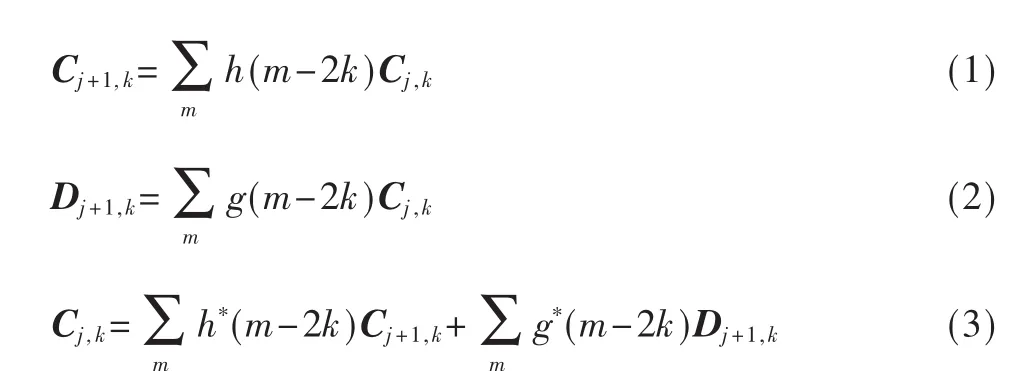

二维小波变换就是先对图像的每一行做一维小波分解,然后在行变换的基础上再对每一列做一维小波分解。采用Mallat算法实现多尺度一维离散小波变换,计算公式为:

式(1)和式(2)为小波分解公式,式(3)为小波合成公式。Cj+1,k为j+1尺度分解后的低频系数向量,Dj+1,k为j+1尺度分解后的高频系数向量。h(k)和g(k)为分解滤波器组;h*(k)和g*(k)为合成滤波器组,是h(k)和g(k)的共扼复数。

回波图像经过分解后,频带被分为 LLn、LHn、HLn和HHn(n为分解级数)4个子带。其中LL子带反映了下一尺度的概貌,其余3个子带分别反映图像在水平、垂直和对角线方向的高频细节信息。递归这一过程,对分解后的低频子带继续分解,直到满足压缩指标或精度要求。

(2)门限处理

回波图像经过多尺度二维小波分解后能量几乎总是集中在低频的子图像(LL)中,并从低频到高频(LH、HL、HH)递减分布。低频部分反映雷达视频回波图像的主要特性,高频部分反映回波图像的细节信息。由于高频成分对显示效果贡献不明显,因此对高频成分采用硬门限处理方法以提高后续编码的效率,同时保留原始信号的一些尖锐特性,防止小目标丢失。

(3)编码

门限处理后,图像数据包含大量零数据(无效数据位与低于门限的图像数据),因此本算法中采用游程编码和Huffman编码相结合的编码方法。首先进行游程编码,统计零数据个数,然后进行Huffman编码形成压缩码流,通过网络进行传输。

2 设计验证

视频处理平台设计完成后,对接雷达视频,并实际验证平台性能。采用黑色背景、绿色目标,在屏幕上可看出明暗及亮度变化,每次扫描能反映出雷达回波对目标显示的更新。

平台主要性能指标如下:

(1)单路视频码率:≤10 Mb/s;

(2)基本量化距离:2 m;

(3)视频灰度等级:8 bit;

(4)实时性:视频延时<40 ms。

针对雷达视频数字化、传输网络化的发展趋势,本文基于最新大规模逻辑FPGA和高性能DSP芯片,结合图像处理理论,将雷达视频信号进行数字化采集、压缩与网络化传输,并对雷达图像适用的压缩算法进行了算法研究,单路视频码率小于10Mb/s;最大视频采样数率为75 MHz,视频延时<40ms。为今后研究基于雷达视频目标回波信号的目标检测、特征研究和模式识别等提供了基础,在指火控系统等领域具有广泛的应用前景。

[1]李侠,董鹏曙,黄树军,等.现代雷达技术[M].北京:兵器工业出版社,2000.

[2]索继东,莫翠君.VTS雷达图像的压缩[C].大连海事大学校庆90周年论文集,大连∶大连海事大学出版社,1999.

[3]Altera company.The Stratix II handbook[EB/OL].[2007-05-01].http∶//www.altera.com.cn/support/devices/stratix2/dev-stratix2.html.

[4]TI company.TMS320C6455 Fixed-paint digital signal processor databook[EB/OL].[2012-03-28].http∶//www.ti.com/product/tms320c6455.