一种针对MCM互连的10 Gbit·s-1自适应收发器

2013-10-17宁永成王增福

戈 勇,莫 巍,宁永成,王增福

(1.中国航天科技集团公司质量技术部,北京 100029;2.西安电子科技大学微电子学院,陕西西安 710071)

系统级封装(System In a Package,SIP)是实现系统小型化的重要方法[1]。通过低温共烧陶瓷(LTCC)技术,多芯片组件(Multi-Chip Module,MCM)能够集成的器件更为丰富,介质损耗进一步降低,组装密度大幅提高,是实现SIP的重要手段[2-4]。在SIP设计实现过程中,面对片间急剧膨胀的数据交换需求,如何实现MCM上芯片间的高速互连,已成为IC设计与MCM设计的共性课题。

针对板级互连,以串化器/解串器(Serializer/Deserializer,SerDes)为基础的串行数据传输技术,在数据传输率、传输距离、信号稳定性及功耗等方面均优于并行数据传输技术,成为实现板上高速数据链路的主要手段。该技术领域朝着高速、低功耗的方向不断发展:Intel圣克拉拉研究实验室在长为24英寸PCB走线上,用32 nm CMOS技术完成了速率为11.8 Gbit·s-1的SerDes收发器,功耗仅为78 mW[5];针对传统的 FR4基板,北京大学采用0.13 μm CMOS工艺设计了一种5 Gbit·s-1,功耗为 50 mW 的 SerDes 收发电路[6];同样针对FR4基板,国立台湾大学采用65 nm工艺,设计了一种 21 Gbit·s-1的 SerDes均衡收发器[7]。

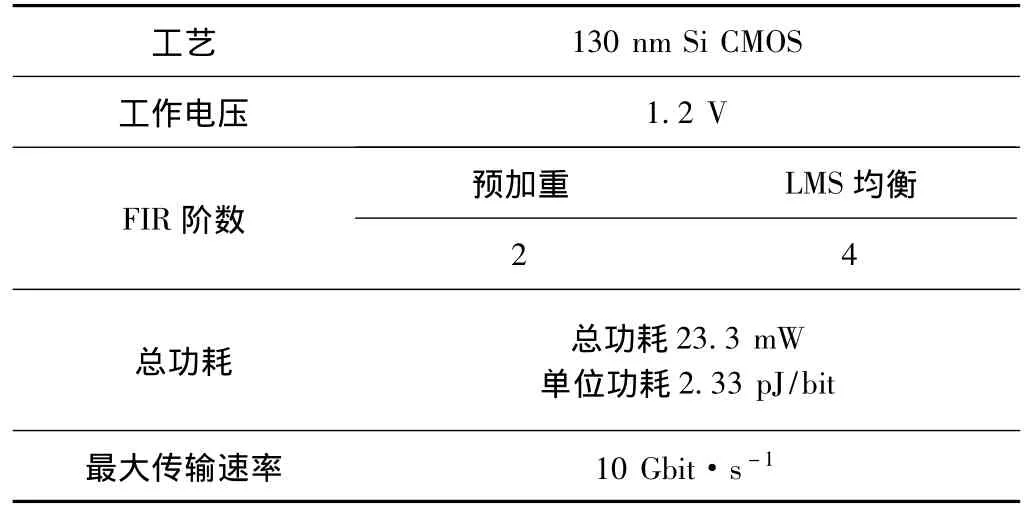

而针对MCM互连的SerDes收发器设计鲜有报道,由于互连负载特性不同,MCM上的SerDes收发器设计不能简单引用针对PCB板的设计方法。为此,本文首先建立了MCM互连的传输线模型,仿真分析了MCM互连的插入损耗情况。在此基础上,针对10 Gbit·s-1的数据传输率需求,采用0.13 μm CMOS工艺,通过选用和完善自适应均衡及预加重方法,设计了一种高补偿、去码间干扰的SerDes收发器,总功耗仅为23.3 mW。

1 MCM互连模型的信号特性

随着信号传输速度的提高,由互连引起的诸如趋肤、介质损耗、反射、码间干扰及串扰等效应在MCM中逐渐变得明显,成为限制系统性能的关键因素,甚至造成系统的功能错误。而S参数互连模型能够精确地表征通道的插入损耗、回波损耗及串扰等特性,因此基于MCM的收发器设计前要获得精确的互连S参数。

本文选用基于测量结果的四端口S参数模型,采用差分的四端口S参数模型库[8],为了避免输出端反射,在输出端采用 50 Ω的终端匹配阻抗。通过Cadence Spectre仿真,得到图1所示的MCM互连S参数,10 GHz处的互连插入损耗约为-30 dB。

图1 S参数分析

2 MCM收发器设计

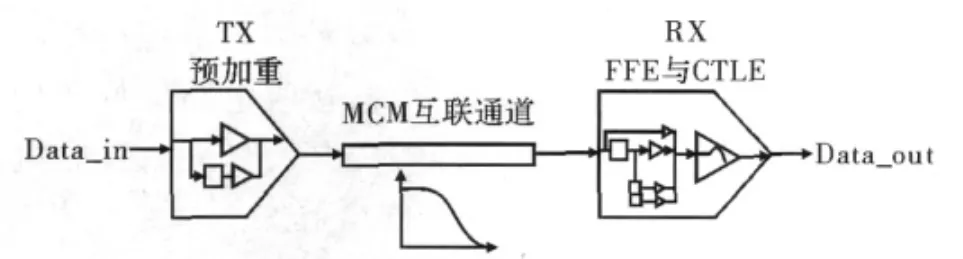

高速信号传输系统需要采用多种手段来克服各种通道效应[9-10]。图2为MCM收发器设计的结构框图,并行输入数据经过串行化后,通过预加重的发送电路,进入MCM互连通道,发送到接收端。在接收端,采用连续时间线性均衡器和基于LMS(Least Mean Square)算法的自适应均衡器来补偿通道导致的高频损耗,信号经时钟数据恢复电路,最终通过解串器转化成并行数据。

图2 系统收发结构图

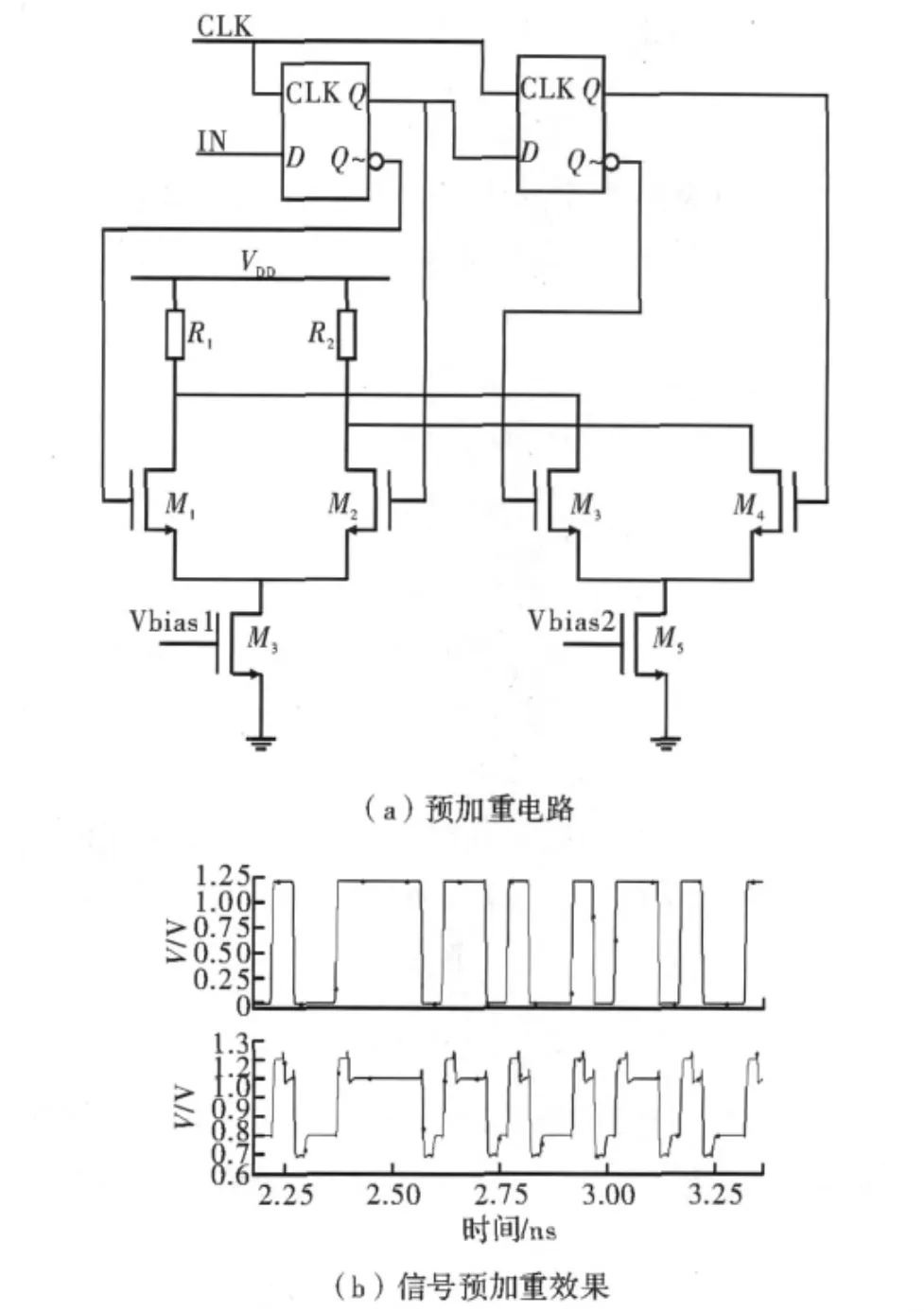

2.1 预加重发送电路

预加重电路由(Current Mode Logic,CML)方式的Buffer线性组合而成,如图3(a)所示。该电路由CML Buffer单元组成,每一个CML Buffer由一个尾电流源来控制,通过调节尾电流源的大小,可以改变本阶Buffer上输出信号的摆幅。这种方法的预加重原理是:将已发送的前一数据与当前数据相比较,如果相同,则将当前比特正常发送;如果不同,则当前数据信号的电压值按一定比例增大后发送。

通过仿真发现,增加CML Buffer阶数可以提高信号预加重能力,但会降低电路的稳定性,因此本文采用两阶结构的预加重形式。预加重结果如图3(b)所示,上方波形为发送的二进制信号,摆幅为1.2 V,下方波形为经过预加重之后的信号,预加重的峰峰值为500 mV,去加重的峰峰值为300 mV。

图3 预加重电话与信号效果图

2.2 均衡接收电路

2.2.1 自适应LMS算法均衡器

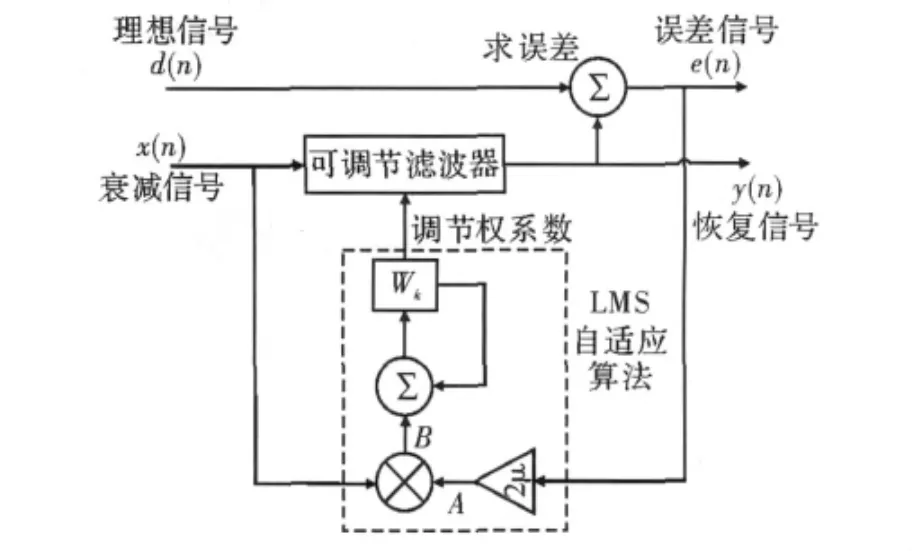

由于MCM互连带来的高损耗和码间干扰现象,将会使接收端的信号产生严重失真,因此需要高补偿、大带宽的接收器来恢复信号。本文采用自适应FFE均衡电路,其核心是运算稳定的LMS算法模块[11],自适应LMS算法模型如图4所示。

图4 自适应LMS均衡模型

基于LMS算法的自适应均衡器,主要处理过程按照功能可以分为滤波、求误差和权值更新3个计算过程。该算法的判据为最小均方误差准则,即理想信号d(n)与滤波信号y(n)之差e(n)的平方的期望值最小。滤波器输出y(n)表示为

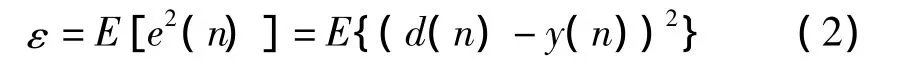

其中,w(n)为权系数,n为时间序列,N为滤波器阶数。根据各个信号定义,均方误差ε可以表示为

计算机求极值通常采用迭代算法,可以求出每次采样值的较佳权系数。LMS算法以最快下降法为原则,即

这里,μ是有系统稳定性和迭代运算收敛速度决定的自适应步长,▽(n)为n次迭代的梯度。对于LMS算法,▽(n)为式(2)中E[(e2(n))]的斜率

对于式(5)的均值,为减少求解每次迭代的计算量问题,用瞬时值-2e(n)X(n)代替期望值-2E[e(n)X(n)],即

LMS算法的一个重要特点是将期望值近似用瞬时值替代,大幅简化了计算量,每次迭代只需M+1次乘法和M次加法,其中M为滤波器的阶数。只要选择了收敛的步长μ和合适的阶数M,该算法就能完成自适应均衡作用。

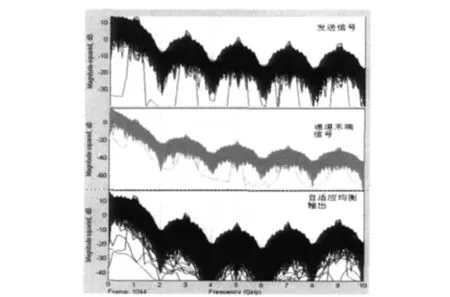

采用Modelsim和Simulink仿真工具,对阶数M为4,步长μ为0.007 8的LMS自适应均衡器进行联合仿真,如图5所示,波形依次为发送信号、通道末端信号和自适应均衡输出波形的幅频响应曲线。可见,恢复之后的信号高频分量衰减度大幅降低,约为-5 dB。

图5 自适应均衡前后的频域比较

2.2.2 有源CTLE模拟均衡器设计

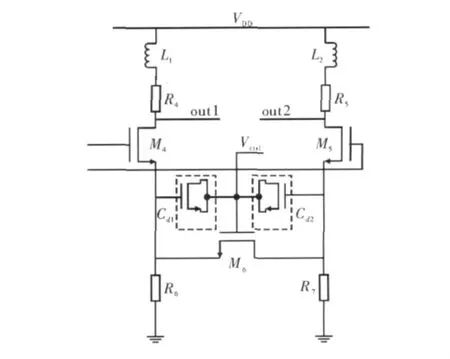

为更好地恢复信号,针对LMS均衡器后-5 dB的信号衰减,设计了有源 CTLE模拟均衡器,如图6所示。

图6 有源CTLE均衡电路

与无源CTLE(Continuous-Time Linear Equalization,CTLE)均衡电路相比[12],有源CTLE电路引入了电感,使得电路出现了一个新的零点。使电路中第一极点和新引入的零点相同,就扩展了信号带宽,通过增大电感还可以起到高频补偿的作用。系统通过改变退化电容Cd和晶体管M6的控制电压,调整电路的增益,从而实现CTLE均衡电路的自适应功能。图7显示了不同控制电压Vctrl下接收电路带宽的变化,虚线表示没有引入电感的接收电路带宽图,实线表示引入电感后接收电路带宽图。经过对比可以发现,接收电路的低频增益随着控制电压Vctrl增加而增大,引入电感后接收电路在高频下能获得比低频更高的增益。

图7 CTLE带宽变化图

3 仿真及分析

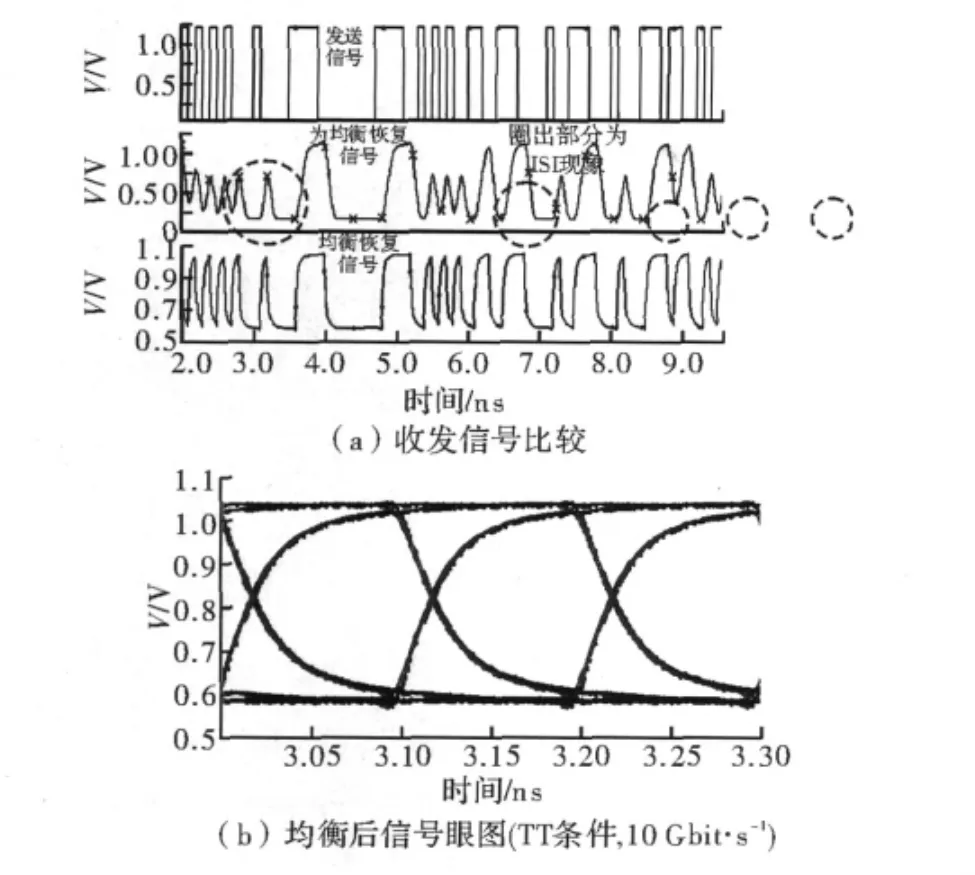

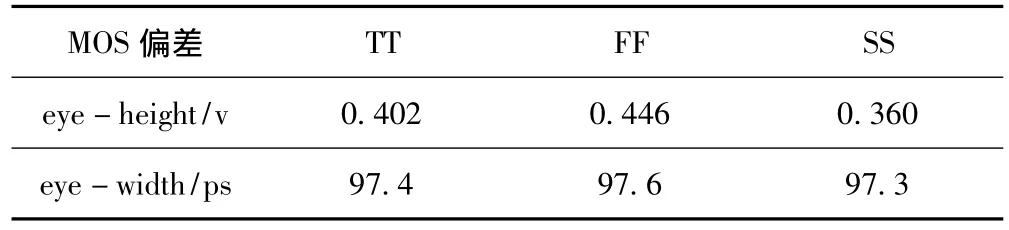

通过Cadence Spectre仿真工具,利用SMIC 0.13 μm标准 CMOS工艺库,采用随机信号发生器产生的10 Gbit·s-1信号,对收发器及MCM互连构成的系统进行了仿真,如图8所示。图8(a)是发送信号、自适应均衡恢复信号和传统收发器恢复信号的对比图。可见,设计的收发器消除了码间干扰,高频损耗部分也得到了较好的补偿,从而简化了后级的电平恢复电路设计,减少了误码率。其典型工艺条件下(TT情况)接收信号的眼图如图8(b)所示,表1为接收眼图质量随工艺偏差的波动情况,表2为电路实现的相关参数。

图8 收发信号比较图与均衡后信号眼图

表1 眼图随工艺偏差变化情况(10 Gbit·s-1)

表2 电路相关参数指标

4 结束语

依据MCM互连结构及其信号传输特性,采用基于CML Buffer的两级预加重发射器、基于LMS算法的自适应均衡和有源CTLE组成的接收器。仿真结果表明,文中提出的收发器能够补偿高达-30 dB的通道损耗,消除了串行比特流中的码间干扰,总功耗仅为23.3 mW。这种方法适用于MCM高速互连结构的设计。

[1]MAURELLI A,BELOT D,CAMPARDO G.SoC and SiP,the Yin and Yang of the Tao for the new electronic era[J].Proceedings of the IEEE,2009,97(1):9-17.

[2]ASSIA A H.LTCC system for high frequency applications[C].Proceedings of the International Multi Conference of Engineers and Computer Scientists,2012.

[3]LEE CHENGKUO,PRAKASH P.Packaging technology for devices in autonomous sensor networks[J].Springer Series on Chemical Sensors and Biosensors,2013(13):1-41.

[4]童志义.低温共烧陶瓷技术现状与趋势[J].电子工业专用设备,2008(11):1-9.

[5]SPAGNA F,CHEN Lidong.A 78 mW 11.8 Gbit·s-1serial link transceiver with adaptive RX equalization and baudrate CDR in 32nm CMOS[C].IEEE Solid-State Circuits Conference Digest of Technical Papers(ISSCC),2010:366-367.

[5]周维娜.5 Gbit·s-1SerDes模拟自适应均衡器研究与设计[D].北京:北京大学,2009.

[6]WANG Huaide,LEE Jri.A 21-Gb/s 87-mW Transceiver With FFE/DFE/analog equalizer in 65-nm CMOS technology[J].IEEE Journal of Solid-State Circuits,2010,45(4):909-920.

[7]WANG Bo,CHEN Dianyong,LIANG Bangli.Modeling,simulation and analysis of high-speed serial link transceiver over band-limited channel[C].11th International Conference on Computer Modeling and Simulation,2009:574-578.

[8]AARON C,HU Jianyun,XU Jie,et al.Using transmission lines for global on-chip communication[J].IEEE Journal on Emerging and Selected Topics in Circuits and Systems,2012,2(2):183-93.

[9]JAEHA K,CHEN E-Hung,REN Jihong,et al.Equalizer design and performance trade-offs in ADC-based serial links[J].Circuits and Systems,2011(5):2096-2107.

[10]樊昌信,张甫翊,徐炳祥,等.通信原理[M].北京:国防工业出版社,2001.

[11]王增福.高速串行传输技术的研究和设计[D].西安:西安电子科技大学,2012.