高分辨率频率合成器在机载电子设备中的应用

2013-10-17周炳利张二剑

周炳利,张二剑

(陕西凌云电器集团有限公司设计所,陕西宝鸡 721006)

某机载电子设备通过接收、处理地面信号而获得解算数据,其接收、处理性能直接影响着机载电子设备的计算精度,需要频率源在低噪声、高稳定度的基础上具有较高的频率分辨率和频谱纯度。

早期的机载电子设备是用单环锁相技术获得低噪声、高稳定度频率源的,但不足是频率分辨率较低。为获得低噪声、高稳定度、高分辨率的微波频率源,现代机载电子设备采用多环锁相技术或数字合成技术,研制了宽带、高分辨率、低相位噪声的频率源[1-2]。

1 锁相频率合成器基本原理

1.1 单环锁相频率合成器

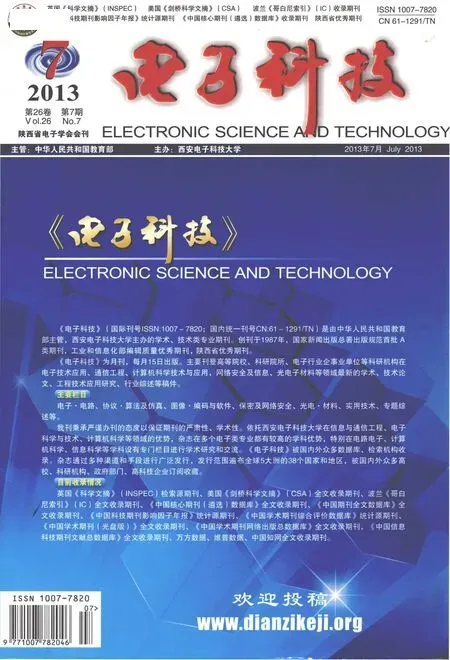

单环锁相式频率合成器是由鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)和可变程序分频器等组成,锁相环(PLL)对高稳定度的参考振荡器锁定,环路串接可编程程序分频器,通过改变程序分频器的分频比N,从而获得N倍的参考频率输出[3]。现代单环锁相频率合成器采用双模分频技术扩展输出频率范围,图1是采用双模分频技术的单环锁相频率合成器原理框图,分频比为N=(P+1)A+P(B-A)=PB+A;输出频率为:fo=fr(PB+A)。

图1 双模分频技术的单环锁相频率合成器

1.2 三环锁相频率合成器

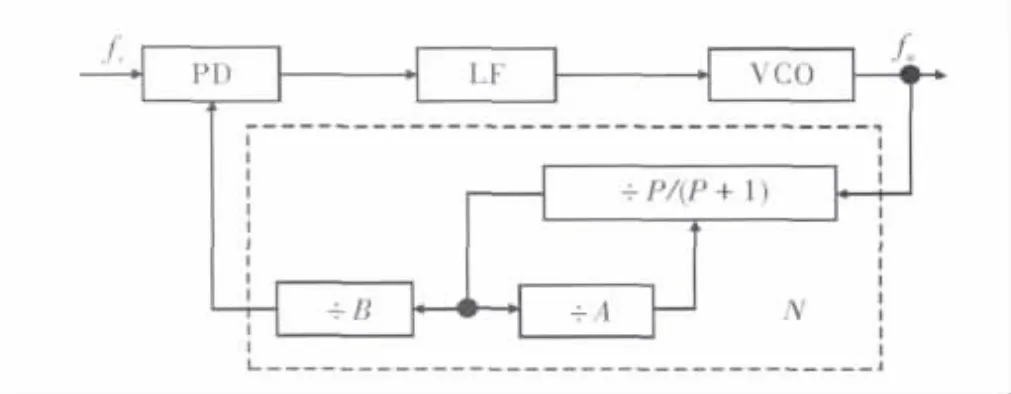

三环锁相频率合成器由3个锁相环组成,其中高位锁相环提供低分辨率、高频率的输出;低位锁相环提供高分辨率、低频率的输出;再通过频率相加的锁相环,将两个分量相加,从而获得高工作频率、高分辨率的输出[4-5]。如图2所示,A环输出fa经后置固定分频器M分频后为fA=Nafra/M,fA的分辨率ΔfA=fra/M,比单环分辨率提高M倍。由于固定分频器M后置,fA一般较低,因此A环是输出频率较低的高分辨率环,又称低位环;B环的输出fb=Nbfrb,其工作在所需的输出频率范围,因此B环又称高位环;C环为混频相加环,输出频率fo=fb+fA,输出频率分辨率Δfo=ΔfA,即Δfo也就提高了M倍,而A环的参考频率并未降低。

图2 三环锁相频率合成器原理图

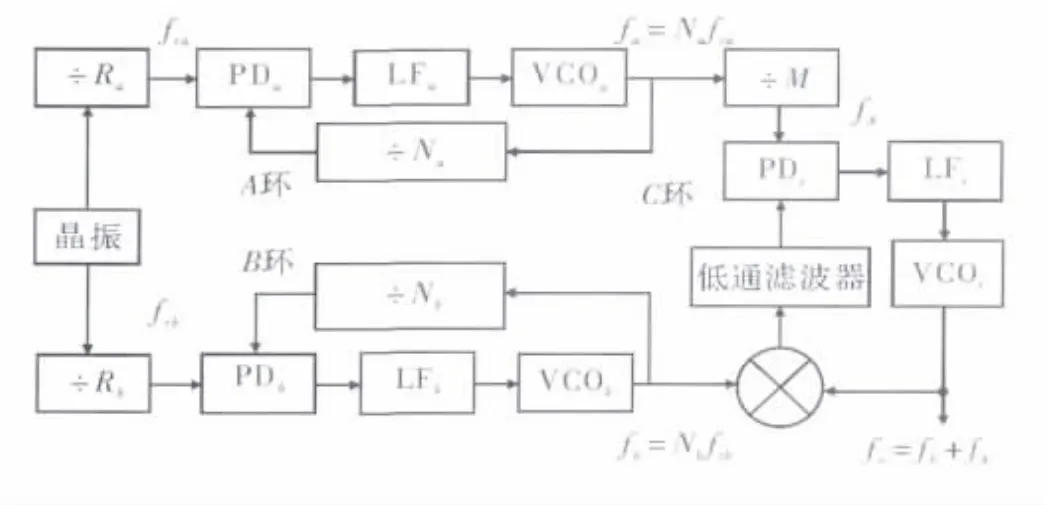

图3 C波段高分辨率频率合成器电路图

2 C波段高分辨率频率合成器设计

2.1 技术要求

工作频率为C波段;波道间隔100 kHz;付波道间隔1 kHz;相位噪声:≤-90 dBc/Hz@1 kHz;杂波抑制≤-70 dBc。

2.2 方案选择

技术要求在C波段以100 kHz为主波道间隔,副波道间隔1 kHz,工作频率高、副波道间隔小、频率分辨率高。单环锁相技术难以全面满足指标要求,而PLL与DDS混合技术在本方案频段杂波难以滤除、使用硬件多、体积重量大、功耗难以降低;而三环方案集成度高、体积小、重量轻、功耗低。

三环方案与单环方案相比,高频率环提供高频率输出,在输出频率相同的情况下,分频比可大幅缩小,有利于减少环路的寄生输出和相位噪声,并改善捕捉性能;低频率环的主要作用在于保证必要的波道间隔,分频比也可减小,同样有利于低频环性能的改善。三环最大的特点在于将单环中较大的分频比分裂成两个分频比均较小的单环,同时将两个单环尤其是高频率环的参考频率大幅提高,从而解决了要求参考频率高、分频比小与分辨率高的矛盾。三环与单环方案相比,缺点是电路相对冗杂,对印制板布局、布线、供电和地线的要求较高。

2.3 方案设计

方案选用ADI公司生产的集成锁相环芯片ADF4107实现三环频率合成器、选用IAM-81018做混频器、VCO按频段要求分别选用集成压控振荡器HE102和HE882,选用频率为10 MHz晶振,其相位噪声可达-155 dBc/Hz@1 kHz。3个环路硬件结构基本相同,不同的是C环加入了一个混频器和低通滤波器,文中称为内插混频式锁相环。图3为C波段高分辨率频率合成器电路框图。

ADF4107是一个工作频率为7 GHz的集成锁相环电路芯片,主要由低噪声数字鉴相器(PD)、可变参考分频器R(14 bit)、可编程A(6 bit)、B(13 bit)分频器和一个双模分频器(P/P+1)构成,加上外部的环路滤波器(LF)和压控振荡器(VCO)就构成了一个完整的锁相环频率合成器。压控振荡器输出的信号经N(BP+A)次分频后送入鉴相器,与参考频率鉴相后经电荷泵的作用输入到环路滤波器中,环路滤波器将电流转换成压控振荡器的控制电压,同时对噪声及鉴相输出的纹波等干扰进行抑制,鉴相器内部有一个可编程延迟单元,用以控制翻转脉冲的宽度,该翻转脉冲保证鉴相器的传递函数无死区,因此降低了相位噪声和参考杂散。

ADF4107通过芯片的数字串口对A、B、R、P等寄存器进行预置和改变,CLK、DATA以及LE控制数据传输,当LE为高电平时,在每个CLK的上升沿,已锁入内存的24位数据被送入相应的寄存器。方案采用CPLD进行控制,CPLD最快工作时间为10 μs,同时还具有较多的宏单元,可快速实现对ADF4107芯片的串口控制。

使用ADI公司提供的4000系列锁相环芯片的仿真软件ADI SimPLL,可方便地对各环路滤波器进行仿真,该软件提供有多种类型的环路滤波器,用户可根据需要选择滤波器类型,为不引入有源器件的电源噪声,方案选用三阶无源环路滤波器,选定VCO的参数,软件则自动计算出各环路的参数及相位噪声、锁定时间等。

C环中的低通滤波器设计成一椭圆函数型,选择差频信号、滤除混频器所产生的杂波分量,在1 MHz以下衰减≤0.2 dB,而3 MHz以上衰减>60 dB,矩形系数好,Q值高且带内起伏小。

2.4 优化设计

C波段高分辨率频率合成器除了在原理设计和元器件选择方面应精心挑选外,还应在电路布局、布线、供电、接地及屏蔽方面采取相应的优化措施:首先供电链路必须避免电磁耦合,ADF4107作为锁相电路的主芯片,对其供电时,在电源输入端应加入一个0.01 μF电容,必要时鉴相器电源可连接到一个单独滤波良好的电源上;同时应为VCO的供电提供射频旁路,除了在供电链路上加47 μF的电解电容外,还可再加射频扼流圈和1 000 pF~0.1 μF电容;其次PCB板铺地时,按传输信号的不同可分成4块:接口链路、参考信号链路、低频信号链路及微波信号链路,呈掌状分布,在大面积接地处一点相连,不成环路。VCO顶层或底层的覆铜应全部保留;并在电路板的顶层用覆铜形成屏蔽面来环绕VCO的压控输入线,可以起到一定的屏蔽作用,压控输入线应尽量短,以减少外部噪声源的调制机率。

2.5 主要电性能

C波段高分辨率频率合成器保持了单环锁相式频率合成器频谱纯度高、频率稳定度高的特性,还进一步提高了频率分辨率,与PLL和DDS混合合成技术相比杂散性能也得到了改善。经测试输出杂散<-70 dBc,在1 kHz处的相位噪声<-92 dBc/Hz@1 kHz,频率分辨率为1 kHz。

3 结束语

文中设计的C波段高分辨率频率合成器输出频带宽、频率分辨率高、相位噪声低、电路稳定性好、环境适应性强,经验证,满足某机载电子设备的要求,同时还可提高某设备的计算精度和可靠性。

[1]郑继禹,张厥胜,万心平.锁相技术[M].2版.西安.西安电子科技大学出版社,2012.

[2]邓贤进,李家胤,张健,等.宽带锁相扫频源设计[J].现代电子技术,2005(24):123-126.

[3]马文瑞,杨培君.一种新型扫频仪的设计[J].电子科技,2011,24(5):69-72.

[4]梁刚,闫源红,李亚红.频率合成器的设计[J].电子科技,2009(10):14-17.

[5]李静,徐艳.直接数字频率合成信号的软件设计[J].电子科技工程,2012(8):109-111.