一种DC/DC转换器的短路保护电路设计

2013-10-17薛超耀马任月

袁 政,薛超耀,马任月,卢 晶

(西安电子科技大学电路CAD研究所,陕西西安 710071)

DC/DC转换器因其体积小、重量轻、效率高、性能稳定等优点得到了广泛的应用[1]。随着单片集成技术的发展,开关变换器在精度和性能上的要求不断提高[2]。而DC/DC变换器作为系统内部能量使用者和外部能量提供者的接口器件,其性能和可靠性直接关系到系统的安全[3]。作为功率处理器件,DC/DC变换器一直是系统可靠性设计的薄弱环节,其中过流和短路是实际工作中常见的两种异常工作模式。当DC/DC变换器工作在过流或短路状态时,若不能及时正确处理,不仅会加速元件老化,甚至会导致DC/DC变换器自身损坏,使整个系统陷于瘫痪,严重时还会引起触电、火灾等安全事故。因此,完善的短路保护[4]设计是高可靠DC/DC变换器的基本要求。

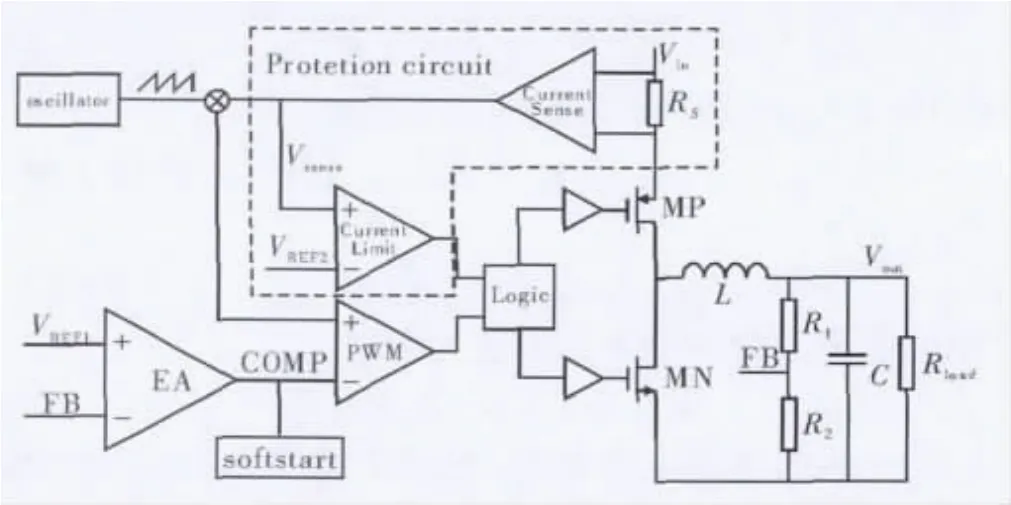

DC/DC变换器是一个负反馈系统,它通过输出电压VOUT进行得到的采样信号FB与基准电压VREF1进行误差信号,EA的输出电压COMP与通过电流采样的电压进行比较输出占空比可变的脉冲信号,来控制功率通道的导通时间,实现输出稳压。当VOUT较大时,通过减小占空比达到减小功率管MP的导通时间;反之,通过增大占空比达到增大功率管MP的导通时间。

图1 DC/DC整体结构框架图

当DC/DC变换器工作在短路状态时,输出电压为零,输出电压的采样电路无法正常工作,导致放大电路无法工作而使系统回路断开,DC/DC变换器处于失控状态[5-6]。对于峰值电流型控制,由于电流反馈环路的作用,保持电路工作在一个固定占空比,占空比的大小取决于EA输出电压的高嵌位电压设计。但是,受电路中各种条件和因素的制约,难以将占空比控制到最小值达到降低短路时芯片的功耗。在输出短路时,每个开关周期功率管导通阻抗在大电流时产生大量的热,并全部消耗在DC/DC变换器内部。若无短路保护措施,在短时间内,输入电流变大,使DC/DC变换器的电流环路也工作在过载状态,会因芯片过热而影响其寿命;严重时造成DC/DC变换器输入损坏。短路保护的主要目的是降低短路时的功耗。理想的保护方式是在发生短路时关断功率通路,使DC/DC变换器不再损耗能量,但在故障消失时自动恢复正常。评价短路保护的优劣主要看短路时功耗的大小和短路释放时能否及时恢复到正常的工作状态。短路时电路的功耗越小,短路释放时恢复到正常的工作状态电路所需的时间越短,电路的可靠性越高。

1 传统保护电路设计

由于过流和短路在原因和现象上的相似性,具备过流保护功能的电路也具备一定的短路保护功能。当输出电流过大时通常采用过载保护电路将输出电流控制在某一最大值,确保电路不会因为输出电流过大而损坏芯片。

图1中虚线中的电路为过流保护和短路保护放在一起的框架图。当输出短接到地时,此时采样电压FB为0,误差放大器不能正常工作,其输出COMP端电压为高电平,若没有短路保护电路,系统则以大电流输出,直至烧坏整个芯片。传统保护电路如图1所示,当输出短路时,通过电流采样电路将输出电感电流进行采样转化成采样电压Vsense,与基准VREF2进行比较,当Vsense大于VREF2时,关断功率管 MP。其Vsense与IL的关系

其中,AV为采样放大器的的电压增益。

当Vsense>VREF2,功率管关断,电感电流开始下降,则有

电感电流的最大值ILmax表达式为

此时的电感电流较大,超过正常工作时的最大输出电流,会因短路功耗大而缩短承受短路的时间,从而影响产品及系统的可靠性。因此,对过流和短路有针对性地分别设计保护电路,有利于提高产品的可靠性。

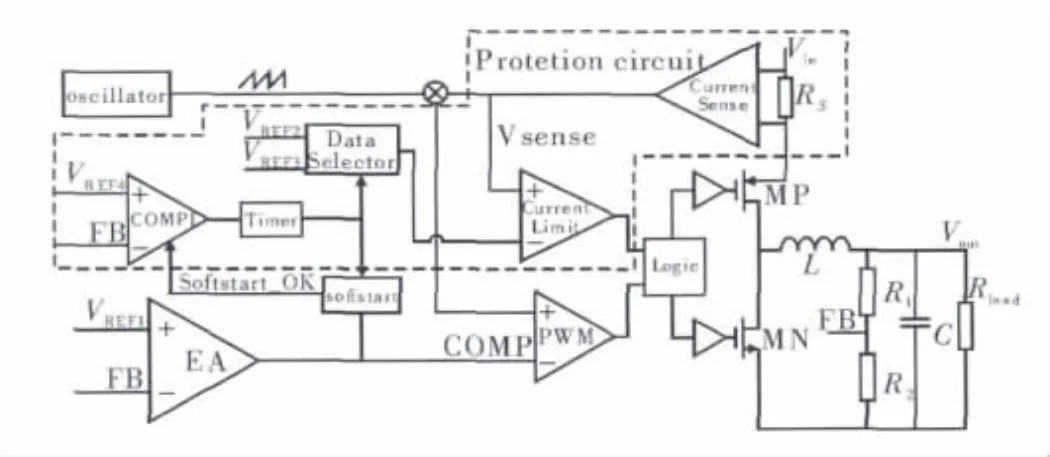

2 新型短路保护电路

图2为新型含有短路保护电路的DC/DC变换器的整体框架图。图2中虚线部分的电路包含短路保护和过流保护两种功能,该电路实现了将短路和过载两种异常状态分开处理。

图2 含新型短路保护的DC/DC整体结构框架图

在工程应用中,通常将输出电压小于设定输出电压的0.3倍视为电路处于短路状态。在图2中取VREF4=0.3VREF1,在电路正常软启动时,通过产生Softstart_OK信号使比较器COMP1不工作,此时电路正常启动。当电路检测到输出负载较大但不是短路状态时,通过数据选择器Data Selector将VREF2传输到Current_limit比较器的输入端将电感电流限制在ILmax。当电路检测到输出电压低于正常输出电压的0.3倍时,即VFB<VREF4,系统认定为负载短路,此时启动短路保护电路。当VFB<VREF4时,启动计时器Timer,并迅速将Softstart复位,并通过数据选择器Data Selector将VREF3传输到Current_limit比较器的输入端将电感电流限制在一个微小的ILmax1。当计时器达到一定时间后释放Softstart并通过数据选择器Data Selector将VREF2传输到Current limit比较器的输入端将电感电流再次限制在ILmax,并同时Softstart输出Softstart_OK信号使COMP1比较器不工作。当 Softstart完成后释放 Softstart_OK使COMP1比较器不工作,若VFB>VREF4,则电路恢复正常工作;反之,则继续上述动作,直至电路恢复正常工作,否则一直重复上述动作。在短路时,Vsense与IL的关系不变。但是Current_limit比较器的输入端基准电压变小为VREF3,则有

电感电流的最大值ILmax1表达式为

选择合适的VREF3,即可有效降低短路时的输出电流,进而提高芯片工作效率,延长芯片使用周期,提高产品及系统的可靠性。

3 新型短路保护电路

图3为短路检测与控制逻辑电路,当发生短路时,启动短路保护电路之后,并不再进行短路检测直到短路机制完成所有工作后才再次检测。图中左侧虚线部分为锁存电路,只要发生短路,及时锁存当前状态,直到短路保护的所有动作完成之后释放当前状态,再次检测是否发生短路,若没有发生就正常启动电路,反之继续启动短路保护电路。锁存检测到短路状态之后保持当前 状态,并不让电路反复检测,以免电路无法再次启动。

图3 短路检测和逻辑控制电路图

当系统正常工作时,VFB>VREF4,此时电路不会进入短路保护状态,并且 Timer_OK信号为低电平,Softstart_OK为高电平,则Reset信号为低电平,Timer_Reset信号为高电平,此时Timer_Reset信号对计时器进行清零处理,直到下次计时器工作时,重新计时并且数据选择器将VREF2连接到Current_limit的输入端以获得较大的电流限电流。

在系统发生短路瞬间,VFB>VREF4变为VFB<VREF4,COMP1比较器输出从高电平跳为低电平,脉冲发生电路迅速产生高电平脉冲使Timer_Reset信号为低电平,Reset信号为高电平,对 Softstart进行清零处理,Softstart_OK变为低电平,直到下一次Softstart电路工作时重新计时Timer_Reset信号为低电平,并且由于Reset信号为高电平和Softstart_OK变为低电平,DIFF触发器会从QB端输出高电平,达到屏蔽比较器输出的效果以避免无限重复触发短路保护电路。此时Timer_OK信号变为高电平,锁存当前状态并将VREF2连接到Current_limit比较器的输入端以确保发生短路时没有较小的限电流流过电感。由于Timer_Reset信号为低电平,计时器Timer开始工作。当Timer计时结束,Timer_OK信号为低电平,并且此时脉冲发生电路的输出为低电平,则Timer_Reset信号为高电平,及时对Timer进行清零处理,等待下一次计时,同时Reset信号为低电平,Softstart电路开始工作,电路正常工作。当Softstart电路输出Softstart_OK为高电平时锁存电路的输出端QB变为低电平,此时再次VFB比较VREF4的大小,若VFB>VREF4,电路恢复正常工作,反之再次进入短路保护状态,重复上述动作,直至检测到VFB>VREF4,电路恢复正常工作。

4 仿真结果分析

图4为一款输入电压为12 V,输出电压为5 V,正常工作时负载电流为2 A的DC/DC芯片的测试波形图,图中波形为负载处于短路状态时的电感电流IL的波形图。从图中可以看出,短路时电流会达到6 A,但在加入短路保护后短路电流会降低到几十mA。

图4 DC/DC芯片的测试波形图

5 结束语

该电路已成功应用于一款高压同步DC/DC转换器类芯片,目前该芯片已经投入生产。在原有的限流电路的基础上设计一款新颖的短路保护电路,大幅减小了芯片在发生短路时的输入电流,降低了短路时的功耗,有效延长了芯片的使用寿命,并具备短路状态结束后自启动的功能,在众多高科技产品中得到广泛应用,如蓝牙耳机,笔记本电脑等[5-6]。

[1]DAI Guoding,XU Yang,LI Weimin,et al.The design and realization of internal compensation circuit for current-mode PWM step-down DC—DC converters[J].Chinese Journal of Electron Devices.2010,33(1):53-57.

[2]HAN Jifeng,ANNETTE V J,GABOR C T.A new approach to reducing output ripple in Switched-capacitor-based stepdown DC-DC converters[J].IEEE Transactions on Power Electronics,2006,21(6):1548-1555.

[3]尹华,刘锐.PWM型 DC/DC变换器过流/短路保护电路的设计[J].微电子学.2008,1(38),108-115.

[4]Terou Suzuki.DC-DC converter including short-circuit protection circuit[P].United States Patent,US7443641b2,2008.10

[5]罗志聪,林伟.一个功率可控型蓝牙CMOS功率放大器设计[J].微电子学与计算机,2009,53(6):208-211.

[6]黄世震,罗志聪,孙奇燕,等.一个新颖应用于E类功放的功率控制电路[J].微电子学,2009,21(2):95-98.