基于FPGA的PROFIBUS-DP从站IP软核的设计**1

2013-09-28莫太平张明志

莫太平 王 丹 张明志

(桂林电子科技大学电子工程与自动化学院,广西桂林 541004)

近年来,芯片的设计不断向着功能增强和集成度提高的方向发展,IP核的重用是设计人员赢得迅速上市时间的主要策略。随着CPLD/FPGA的规模越来越大,设计越来越复。IP软核是用VHDL等硬件描述语言描述的功能块,但是并不涉及具体电路元件实现这些功能。软IP核进行系统设计可以提高设计性能,降低开发成本,缩短设计周期,其灵活性强、仿真方便,降低了设计风险。由于不涉及物理实现,为后续设计留有很大的发挥空间,增大了IP的灵活性和适应性,因此使用基于FPGA的IP软核实现PROFIBUS-DP从站的设计。

1 系统总体设计

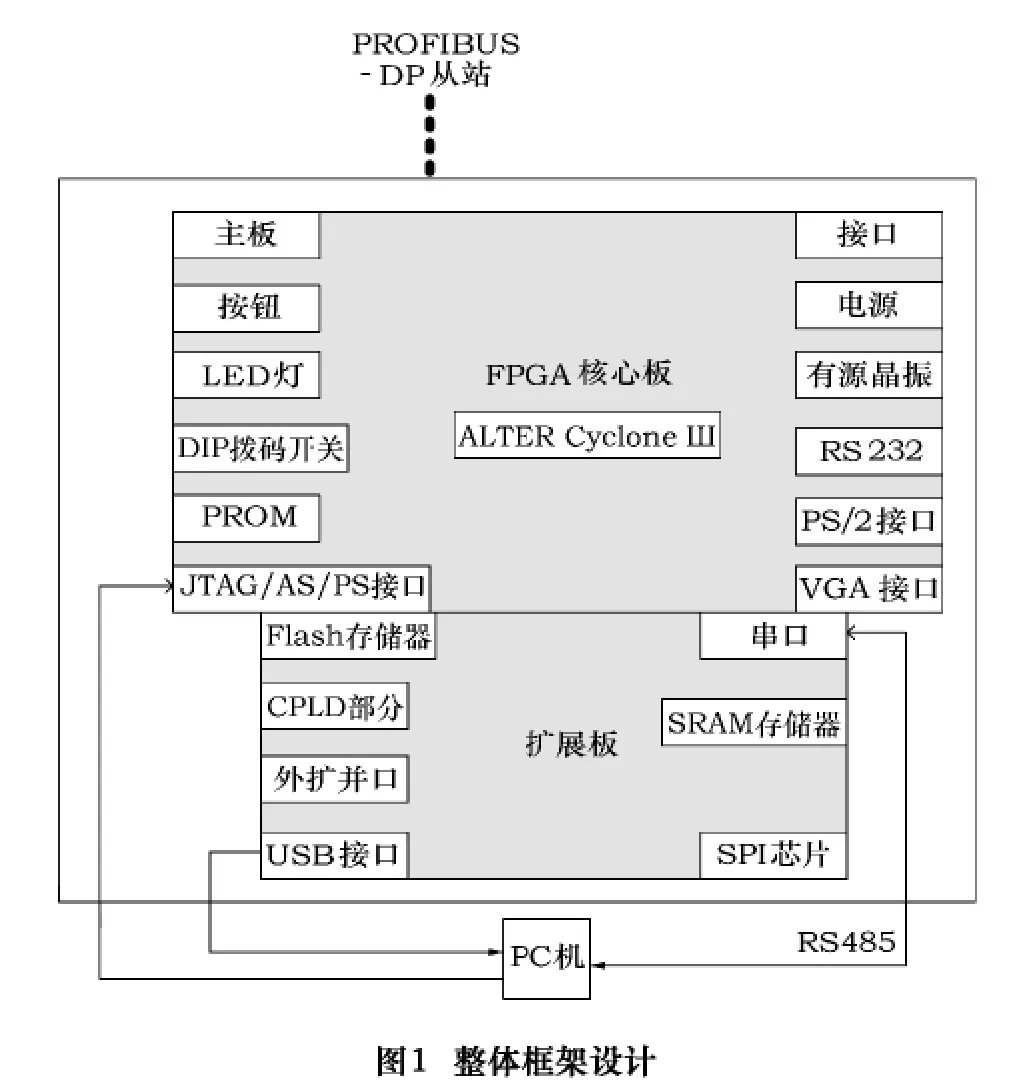

PROFIBUS-DP从站运用自上而下的设计思路,先确定电路的总体框架,然后设计各个模块,并对IP模块功能仿真。需要用Verilog编写模块测试激励文件,如为串口通信接收[1]模块编写输入信号波形,并搭建PC机与模块之间的串行通信环境。通过顶层文件将功能验证正确的模块组合起来形成一个整体设计,并对整体设计中的IP软核进行功能仿真和综合后仿真,最后将综合后的系统文件下载到目标FPGA芯片中进行实际功能验证。系统的整体框架结构及其组成模块如图1所示。

PROFIBUS-DP从站接口采用功能模块设计,系统主要由扩展模块及FPGA芯片组成,构成其核心部分,其他还有RS485、开关设定地址及电源模块、USB接口、有源晶振等部分组成。

1.1 系统实现

HDL文本形式提交给用户,不含任何具有物理信息,经过RTL级设计、优化以及功能验证,用户运用IP软核与综合正确的门电路设计网表,借助于FPGA综合工具可以很容易地与PROFIBUS-DP合成一体。能同时提高设计效率和节约硬件资源。

1.2 FPGA部分设计

FPGA[2]的设计开发流程主要包括行为综合、逻辑综合、技术映射和布局布线。一般情况,设计者使用描述语言(如VHDL,Verilog)描述电路。FPGA部分的主要任务是完成对PROFIBUS报文的组帧、拆帧、FCS校验以及对报文最基本的分析,对应的是PROFIBUS的链路层功能。主要由锁相环模块、串口时钟模块、接收模块和发送模块及相应的缓冲模块、处理模块、定时器模块和寄存器模块组成。

1.3 PROFIBUS-DP从站通信

DP从站是进行输入和输出信息采集和发送的外围设备(VO设备、驱动器、HMI、阀门等)。基于FPGA的PROFIBUS-DP[3]从站通信控制器要实现的功能目标是,在加入总线系统后,能作为一个从站节点进行正常的总线通信。通信控制器的工作过程可以概括为在PROFIBUS-DP通信端,将总线上传送的串行数据转换为从站用户层的数据,同时将从站用户层的数据进行分析打包并转换成符合UART规范的串行数据返回到总线。

2 IP软核设计

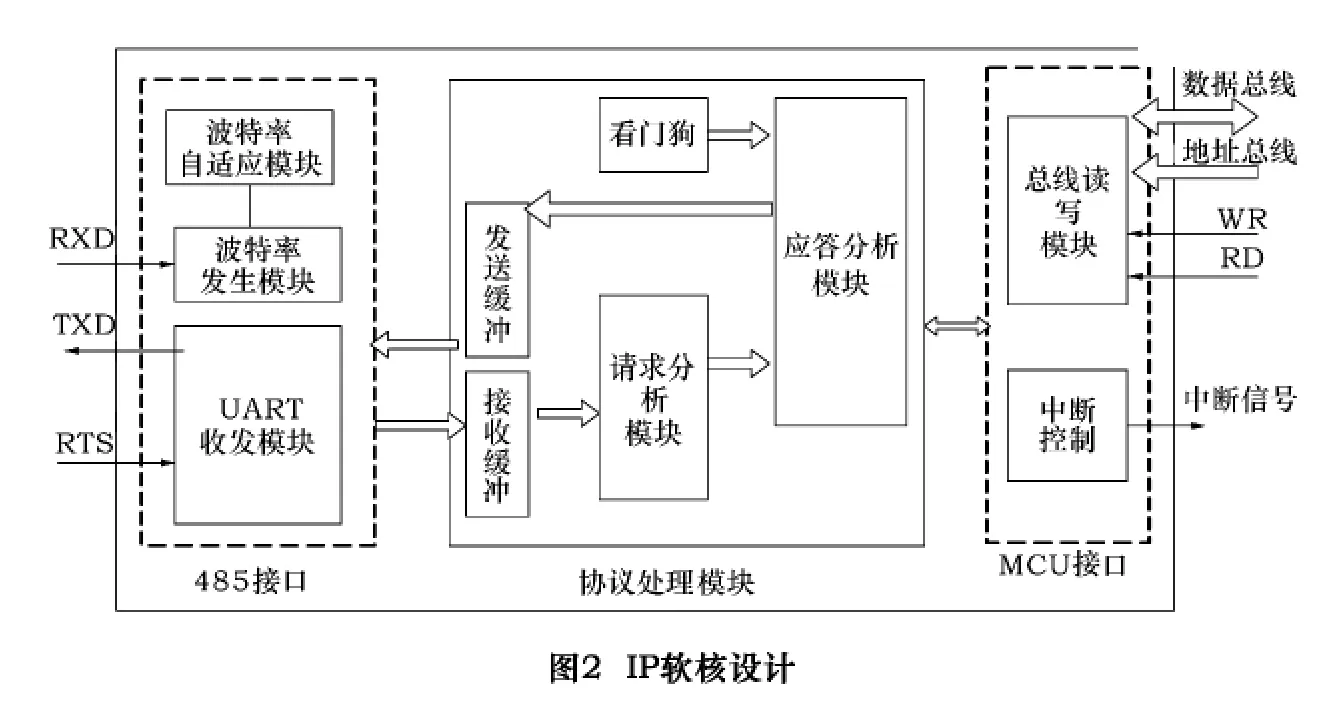

如图2所示,软 IP[4]是以综合形式交付的,因而必须在目标工艺中实现,并由系统设计者验证。其优点是源代码灵活,可重定目标于多种制作工艺,在新功能中重新配置。

(1)看门狗时钟分频器

看门狗的作用在于监视总线通信端[5]是否在看门狗溢出时间内收到主站的通信请求。溢出时间以1 ms为时基,系数由主站发送的参数帧进行设置。

(2)波特率发生模块

PROFIBUS-DP支持9.6 K~12 M之间的多级波特率传输。一共有10级。在同一网络上所选用的传输波特率必须相同。

(3)485接口模块

PROFIBUS-DP的物理层,用与总线连接,接收和发生信息;有波特率自适应功能协议处理模块:根据接收到的帧信息分析处理;实现从站状态的转换。

(4)协议处理模块

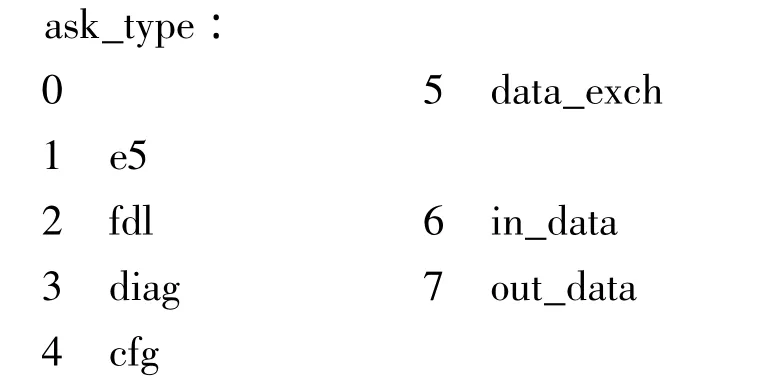

通过RS485接口实现RS485信息的接收,然后在接收缓冲模块中实现完整的PROFIBUS-DP帧的接收。当一个完整的帧被接收后,通过请求分析模块分析出所接收的帧的类型,并作相应的处理。答分析模块结合接收到的帧信息和从站所处析出应答类型以及作相应的处理。得出应答发送缓冲中组成要发送的帧结构,再通过485接口发送出去。MCU接口用与用户程序通信,数据的输入输出等。

2.1 请求分析模块

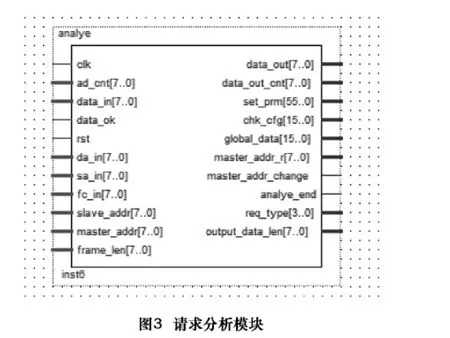

如图3。

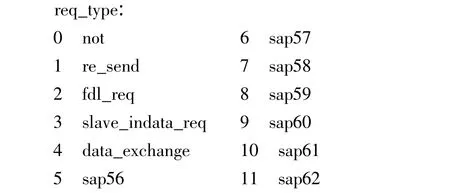

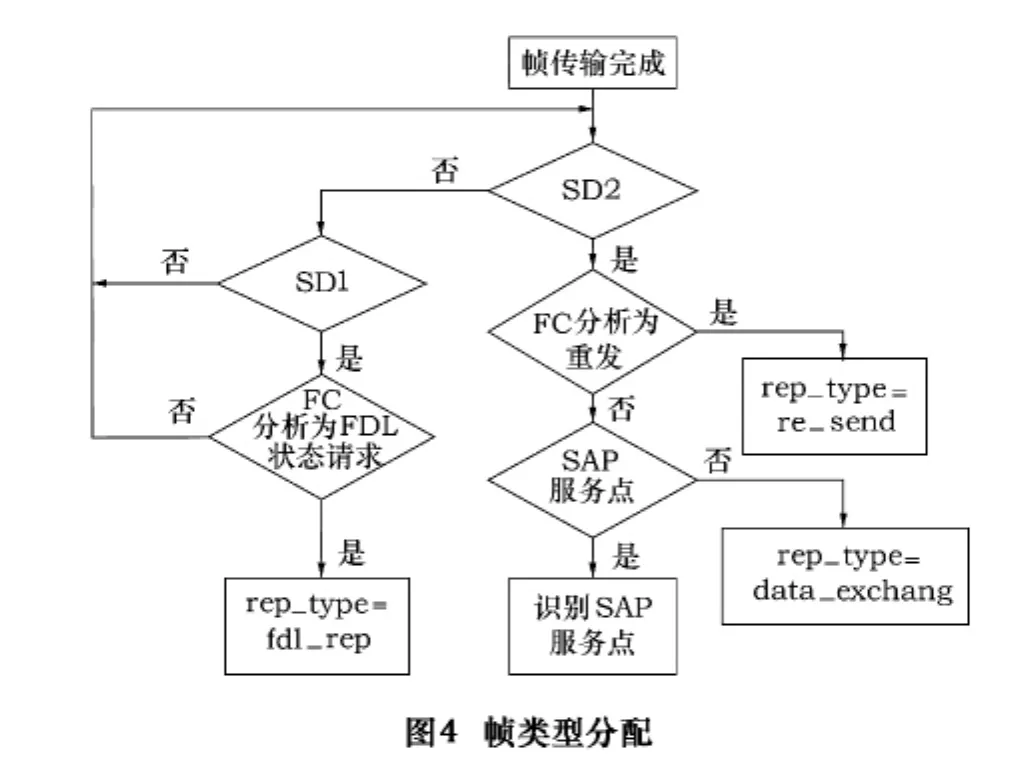

根据请求分析模块分析帧[64]在传输完成时的帧类型,具体判断流程图如图4所示。

当帧传输完成后,根据是否满足SD2的条件来进行帧的分类,最后会分为三种类型:rep_type=fdl_rep;识别SAP服务点;rep_type=data_exchang。因而产生相对应的应答分析模块的数据。

2.2 应答分析模块

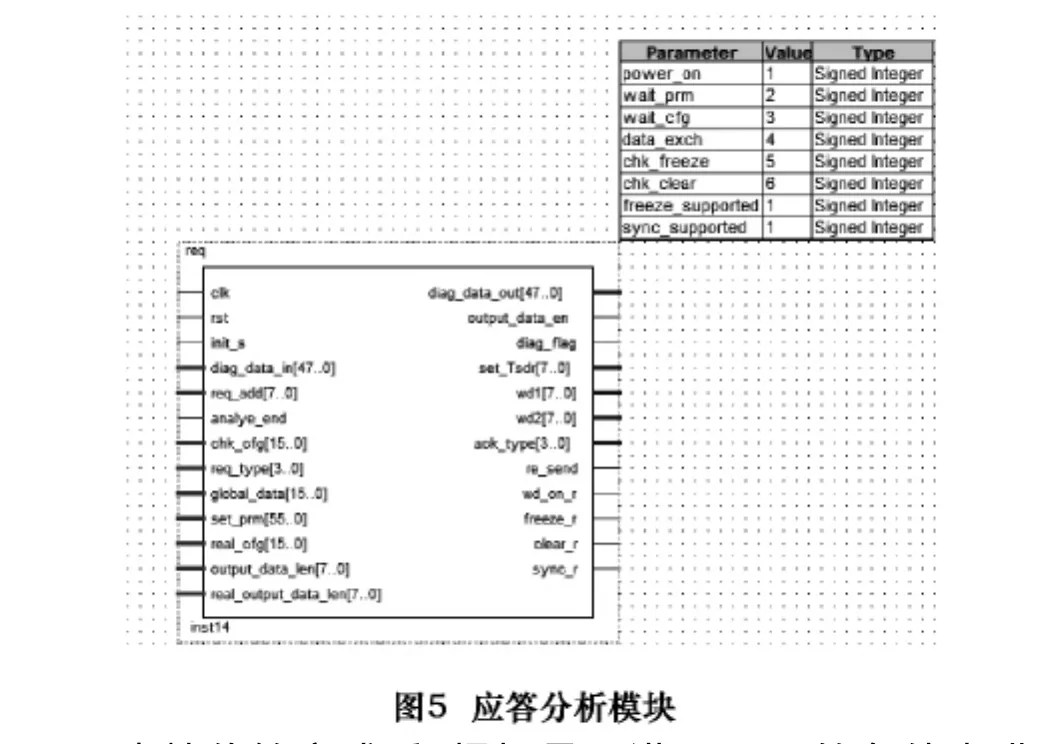

如图5。模块完成应答分析,以及从站状态转换。

3 系统仿真与实现

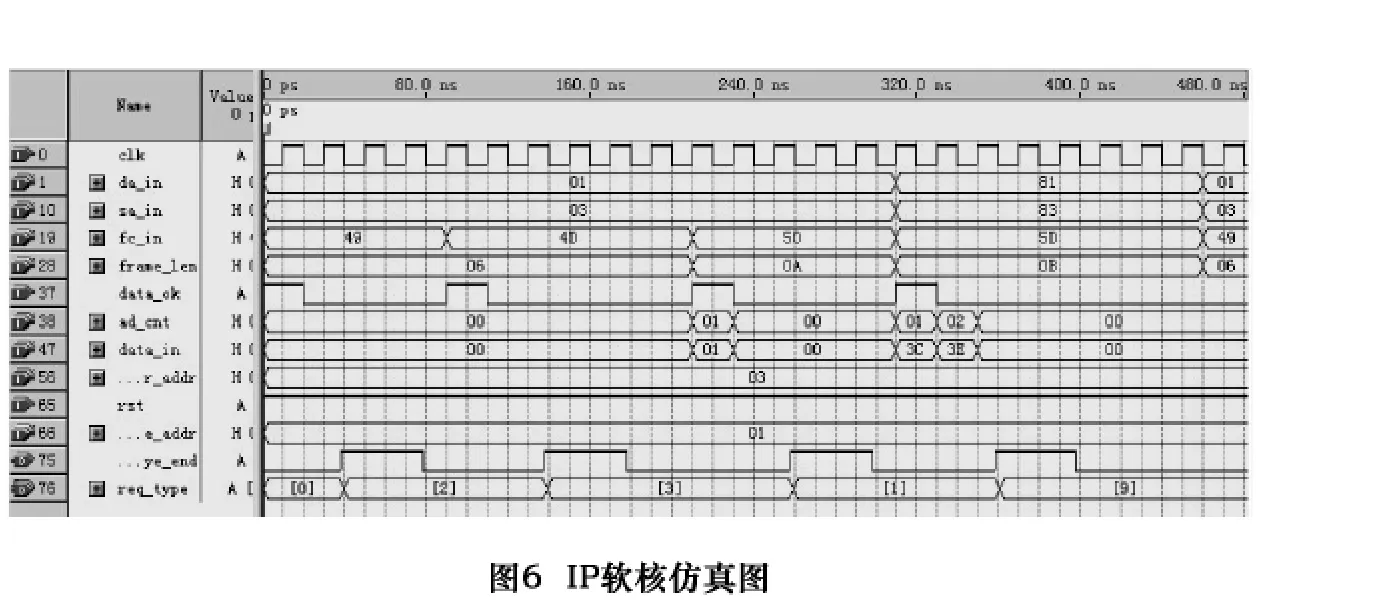

在本设计中,IP核[7]的应用仿真,将利用所设计的IP核实现发送接收模块之间的仿真。基于FPGA的PROFIBUS从站IP软核设计的布局布线后仿真波形图如图6所示,成功完成仿真。

4 结语

本文介绍了一种FPGA芯片PROFIBUS-DP从站的设计方法。从仿真效果上看,运行稳定、控制精度高、系统响应速度快,系统采用软IP核代替传统专用芯片,设计灵活、调试方便,大大缩短了开发周期,提高了系统可靠性。利用FPGA的信号处理性能提高了系统的整体性能。

[1]刘欣.FlexRay通信控制器原型IP设计[D].北京:中国科学院,2007.

[2]石晓亮.基于FPGA的PROFIBUS-DP从站设计[D].杭州:浙江大学,2008.

[3]THOMESSE JP.Field bus technology in industrial automation[J].Proceedings of the IEEE,2005,93(6):1073-1101.

[4]钱小辉.基于IP核的CPCI总线多通道数据采集卡的设计与实现[D].西安:西安电子科技大学,2011.

[5]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003:120-128.

[6]白光泽,邢燕.基于Verilog HDL的SPI IP核的设计及仿真实现[J].制造业自动化,2010,33(12).

[7]潘勇,袁慧梅,侯长宏.基于FPGA的误码仪IP核的设计与实现[J].仪表技术与传感器,2009(3).