基于EZ-USB FX2的弹载测试仪通讯接口的设计

2013-09-27中北大学仪器科学与动态测试教育部重点实验室太原030051

(中北大学仪器科学与动态测试教育部重点实验室,太原030051)

(中北大学仪器科学与动态测试教育部重点实验室,太原030051)

设计了一种基于FPGA和USB技术的弹载测试仪的通讯接口,重点介绍了EZ—USB FX2系列芯片CY7C68013的特点、固件程序的设计及FPGA模块的设计,采用GPIF传输模式简化了系统的硬件电路并且大大提高了数据传输的速率。最后,实验验证了该接口的可行性及实用性。

通讯接口;USB;FPGA;固件;GPIF

弹载测试仪往往工作在振动,高低温、强冲击等恶劣环境下,很多情况下在炮弹的发射过程中,弹载测试仪的通讯接口容易发生损坏,导致采集到的数据无法读出,为了保证在各种恶劣环境中能提取出所采集到的数据,设计了一种弹载测试仪的通讯接口。该接口可以与弹载测试仪分离出来,不随炮弹一起飞行,大大提高了系统的可靠性。在正常情况下,该接口可以与弹载测试仪进行通讯,对弹载测试仪进行各种控制[1]。当弹载测试仪的读数接口在恶劣环境下损坏时,此通讯接口亦可以与弹载测试仪的备用接口进行通讯将弹载测试仪中的数据提取出来以供分析。并且该接口采用USB与FPGA技术,改善了数据传输的瓶颈问题

1 系统总体结构和工作原理

该系统主要由USB模块、FPGA模块和FIFO数据缓存模块3部分组成。整体的结构如图1所示,其中FPGA作为主控单元,一方面通过EZ—USB接受上位机传送过来的各种命令,并通过通信协议判断命令类型,然后将命令转发给数据存储装置,以启动对数据的读取或擦除工作;另一方面读出数据存储装置中的数据并放入FIFO缓存,最后通过USB总线回传给上位机以进行下一步处理。

图1 系统结构框图

2 USB模块设计

2.1 USB控制模块硬件的设计

该系统的USB模块主要采用了CYPRESS公司的EZ—USB FX2系列芯片CY7C68013,该芯片是USB2.0的完整解决方案,并向下完全兼容USB1.1协议。它通过在单片上集成USB2.0收发器、SIE(串行接口引擎)、增强的8051微控制器和可编程的外围接口,使其无需外加芯片即可完成高速USB传输,从而性价比高[2]。

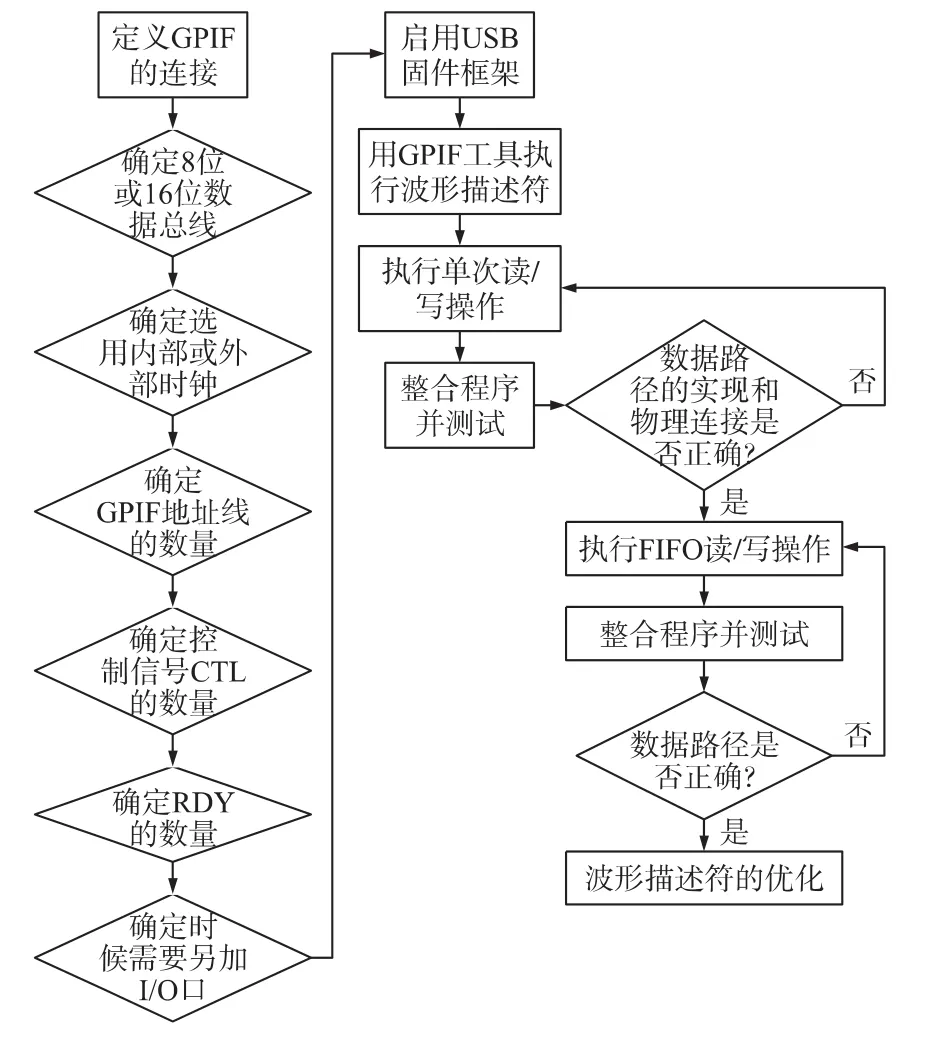

CY7C68013可工作在3种接口模式下:端口模式、GPIF主控模式和从FIFO模式。由于GPIF模式主要由波形描述符来控制CY7C68013工作,其功能的实现通过对波形描述符编程即可,可大大简化外外围硬件电路,因此本设计选用了GPIF模式[3-4]。GPIF的开发过程如图2所示,在这种模式下,FX2的FIFO由内部GPIF控制,CPU不直接参与数据的传输过程,可大大提高数据传输速率。端口B和D作为与FX2的4个端点FIFO连接的16 bit数据接口,由可编程的波形描述符来响应FIFO的状态标志,CTL信号可作为驱动时序的信号,通过采样RDY信号判断外部过程。

图2 GPIF模式开发流程图

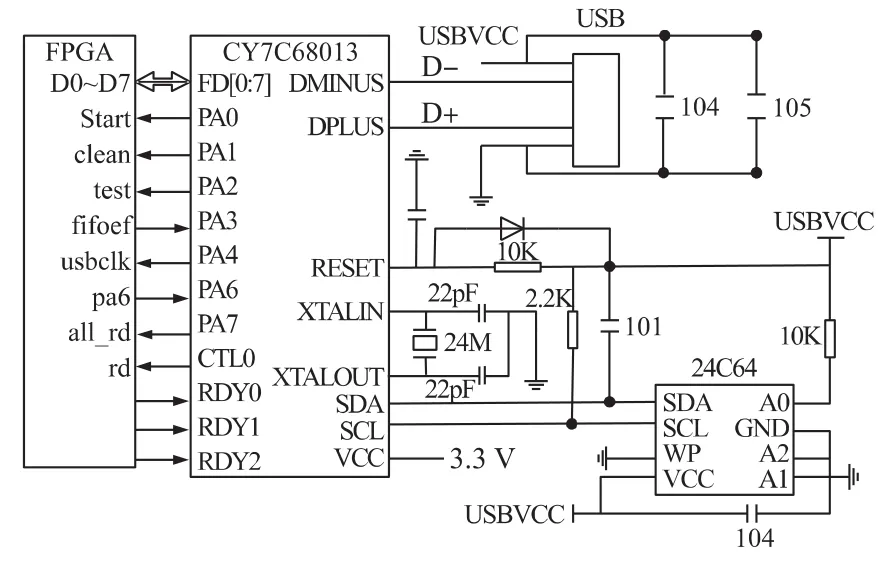

本设计中68013A单片机与FPGA相连的数据线为8 bit,即FD0~FD7;采用CTL0作为模块外部FIFO的读控制信号;FIFO非空信号作为单片机的读数状态判断信号,当FIFO非空信号有效时,系统进行读数操作;另外有3条指令信号线PA0、PA1和PA2,当上位机发出读数或擦除指令到单片机后,单片机再把该指令传给FPGA,FPGA将这些指令编辑成不同的代码下发给下行记录设备,再由弹载测试仪将接收到的这些代码解码出来以辨别是何种指令,进而控制弹载测试仪的读数或擦除操作。其中图3为本设计中USB芯片与外围电路的硬件连接示意图。

图3 USB与外围电路连接原理图

2.2 USB控制模块软件的设计

固件程序是USB传输的关键部分,其主要功能是处理整个系统的通信过程和事物处理。本设计为了减少外围电路的复杂程度而采用了GPIF模式,因此大多数功能都通过GPIF波形设计来实现[5-7]。下面以USB与备用接口读数为例来说明固件的设计与现实。

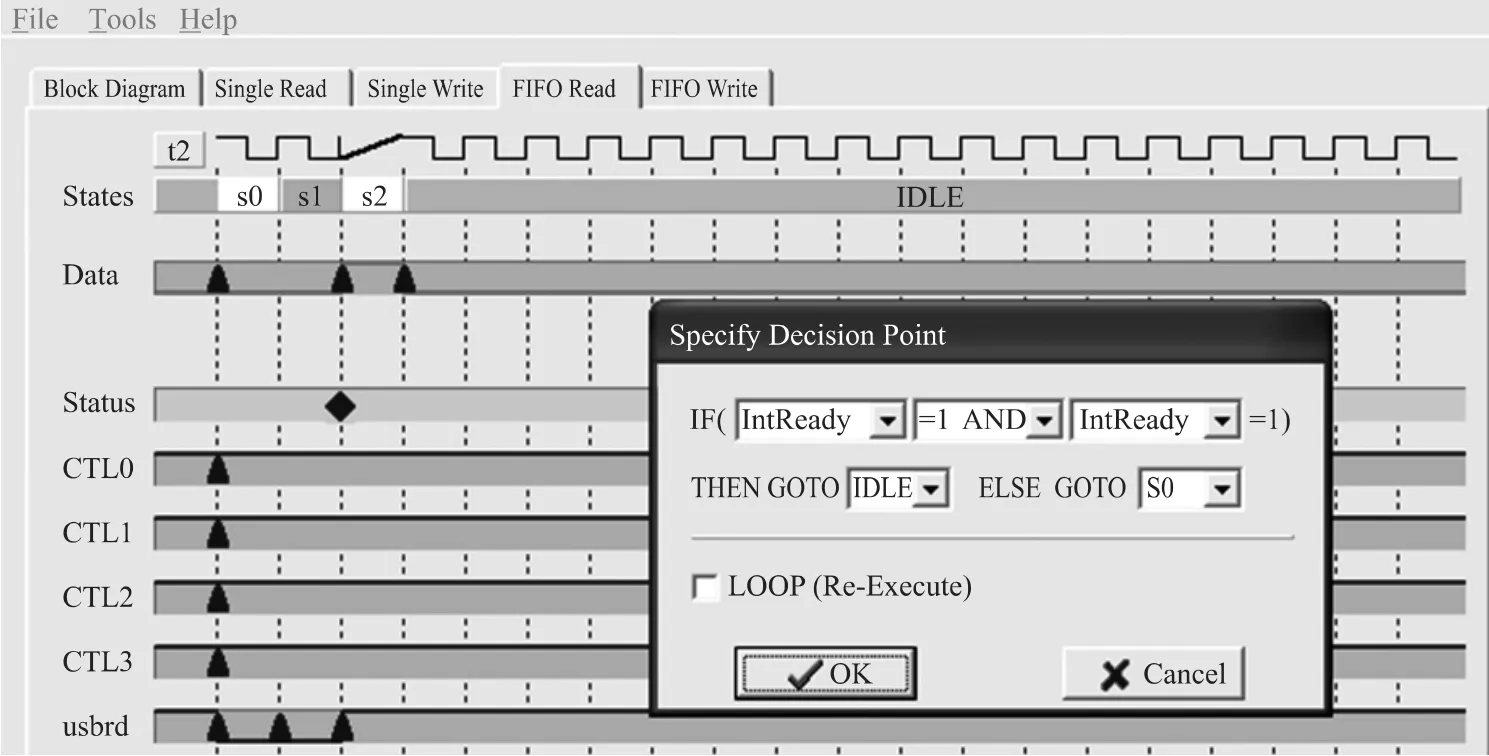

如图4所示:本设计中GPIF波形定义了S0~S2共三个状态和一个IDLE状态S7。S0状态为非判决点,在此停留1个IFCLK周期(即20.83ns),此时rd为低,将FPGA内部FIFO中的数据读出置于数据线上,S1继续这个过程;S2为判决点,此时usbrd输出为高,采样FIFO数据线并储存数据线上的数据以进行后续数据的打包,并且采样内部状态信号INTRDY(该信号是8051的“ready”信号),若该信号非真则跳到S0,若为真则跳到空闲态IDLE状态,结束GPIF传输。在这个过程中,rd充当了读外部数据的时钟信号。当GPIF波形设计好后,由GPIF设计工具将设计好的波形导出成gpif.c添加到固件程序中即可使用。

图4 GPIF波形设计

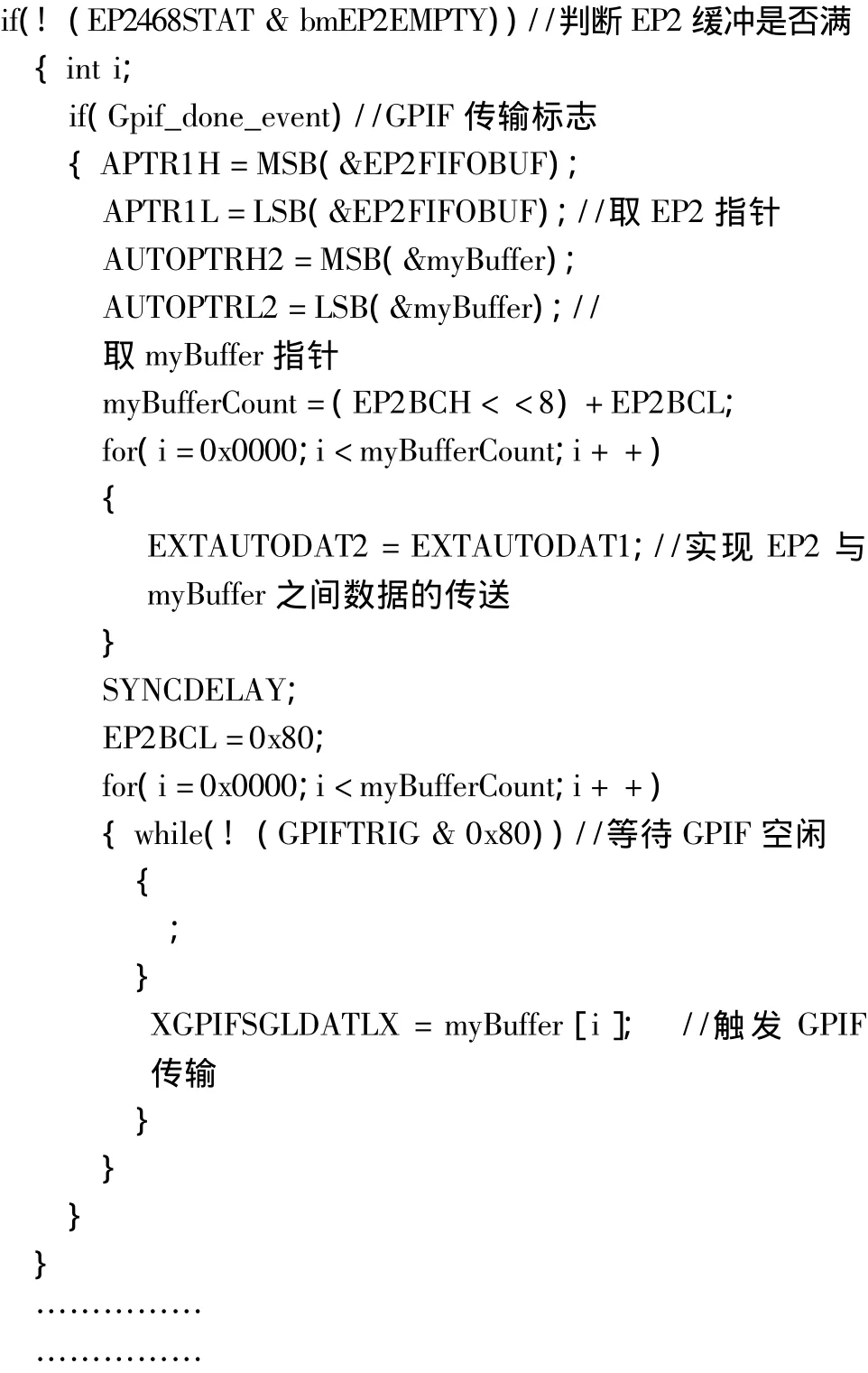

GPIF波形阶段只是将外部数据读入了68013的相应寄存器中,而往上位机的传送还需要联合固件中其他程序来实现[4]。当USB固件检测到上位机发出的读命令时,开始判断外部FIFO是否为非空,若非空则开始将外部数据读入FX2相应的寄存器中进而传给上位机以进行后续处理。整个过程在TD_Poll()函数的反复调度下反复执行,从而将外部数据读出。以下是实现外设功能的部分程序代码:

3 FPGA模块的设计

该模块主要包括PFGA芯片XC2S100E及其程序配置芯片XCFO1S、数据缓存IDT7206及与弹载测试仪的连接接口。X2S100E是XILINX公司Spartan-IIE系列芯片,该芯片具有1.8 V的内核电压,因此功耗更低,并且可以提供等多的I/O口和逻辑门,使其具有更优越的性能[8]。

整个系统由USB接口提供+5 V电压,并由电源转换芯片TPS70351将该电压转换为FPGA所需的3.3 V和1.8 V电压。系统中FPGA的主要功能是负责接收与执行通过USB传送过来的命令,并且按要求对弹载测试仪进行控制,将采集到的数据读出来暂存入FIFO中,之后再将数据传给USB模块,最后通过USB总线将数据传给上位机以供分析。其中图5为本设计中FPGA芯片与外围电路的硬件连接示意图。

图5 FPGA与外围电路连接原理图

图6是从备用接口读数的仿真图:可以看到,将读数命令控制字30H写入f_data后,等待rb_delay自减到0,此时判断rb信号是否为高,若为高则检测读数请求(send_request)是否有效(低有效),若有效则在读信号(rd)的上升沿将数据读出。

图6 读数仿真图

4 测试结果

为验证该系统的可行性及实用性,对该系统进行了多次的测试。图7为在实验室条件下,对该系统输入-3 V~+3 V的矩形波采集到的图形,可看出该系统可准确无误的还原采集到的波形。图8为在某次实际应用中利用该通讯接口采集到的某炮弹发射过程中膛内初始过载信号,从图中可以看出,过载值可达-5 876 gn,脉宽22 ms。膛内过载在1 196 ms~1 218 ms时达到峰值阶段,在1 202 ms附近达到最大值。验证了该接口可以有效测得实验数据,为摸清弹药飞行特性参数做出了突出的贡献。

图7 实验室条件下采集到的波形

图8 炮弹膛内初始过载信号

5 结束语

本系统利用EZ-USB FX2与FPGA实现了弹载测试仪的通讯接口的设计,利用USB芯片的可编程控制接口很好的解决了数据传输的瓶颈问题,经实际应用验证该装置具有很好的稳定,并且具有一定的弹性,易于根据需要灵活组建,具有一定的实际意义。

[1]基于USB和GPIF的大规模数据采集系统[J].微型机与应用,2003,11:16-18.

[2]Cypress Corp.EZ-USB FX2 Technical Reference Manual[S]. USA:Cypress Corp,2002

[3]张颖,林伟.通用存储装置设计[J].电子器件,2012,35(3): 304-308.

[4]薛圆圆.USB应用开发技术大全[M].北京:人民邮电出版社,2007.

[5]严石,杨定礼,张宇林.基于USB2.0的数据采集系统设计[J].电子器件,2008,31(6):1959-1962.

[6]王静红,刘教民,于富强,等.采用CY7C68013芯片的系统固件程序设计[J].河北师范大学学报/自然科学版,2008,32(2): 169-173.

[7]基于EZ-USB FX2的固件程序设计[J].电子元器件应用,2007,9(1):42-44.

[8]钱峰.EZ-USB FX2单片机原理、编程及应用[M].北京:北京航空航天大学出版社,2006.

基于EZ-USB FX2的弹载测试仪通讯接口的设计*

王春水,张斌珍*,龚 珊

The Design of Communication Interface of Projectile Load Instrument Based on EZ-USBFX2LP*

WANG Chunshui,ZHANG Binzhen*,GONG Shan

(Key Laboratory of Instrumentation Science and Dynamic Measurement(North University of China),Ministry of Education,Taiyuan030051,China)

A communication interface of projectile load instrument based on the technology of FPGA and USB is designed.It focused on the the characteristics of the EZ-USB FX2 series chip CY7C68013 and the design of the firmware and FPGAmodule.The data transmission rate and hardwarecircuit of the system are greatly improved by using the GPIF transfermode.Finally,the interface is verified by experimentwith high practicability.

interface;USB;FPGA;firmware;GPIF

10.3969/j.issn.1005-9490.2013.06.036

TP23 文献标识码:A 文章编号:1005-9490(2013)06-0915-04

项目来源:国家自然科学基金项目(51075374)

2013-03-18修改日期:2013-04-11

EEACC:7210

王春水(1988-),男,河北保定人,现于中北大学电子科学与技术系攻读硕士研究生,主要研究方向为光学MEMS、微流检测、射频MEMS器件;

龚 珊(1989-),女,湖北荆门人,硕士研究生,研究方向为微纳传感与执行器件,gongshan89@163.com。

张斌珍(1974-),男,山西岚县人,教授,主要研究方向为微纳机电系统和武器系统恶劣环境下的动态测试技术。在此领域内先后开展微纳器件和系统的设计制造,微弱信号检测与处理,以及恶劣环境下存储测试理论与技术的研究;