一种用于时钟数据恢复的宽带锁相环设计

2013-09-27华虹NEC电子有限公司上海201206东南大学软件学院南京210096

(1.华虹NEC电子有限公司,上海201206;2.东南大学软件学院,南京210096)

(1.华虹NEC电子有限公司,上海201206;2.东南大学软件学院,南京210096)

锁相环广泛应用于电信、光收发器、数据存储局域网以及无线产品中,提出了一种新颖的应用于时钟数据恢复的锁相环设计,包括鉴频鉴相器、电荷泵、环路滤波器、换挡电路、压控振荡器以及环路状态检测电路的设计,采取的方案是对环路滤波器的模拟电压进行实时监控动态调整锁相环系统的环路参数,该结构能够很好的应用于输入数据流变化范围极宽(20 Mbit/s~2.5 Gbit/s)的时钟数据恢复系统。设计采用了一种单供电电压的0.18μm CMOS工艺,并给出Cadence环境下仿真结果。

锁相环;时钟数据恢复;宽带;多相位

随着集成电路的发展,时钟与数据恢复电路(CDR)的应用越加广泛,无论是在长距离光纤通信还是在短距离并行I/O接口通信中CDR电路都是一个关键的电路模块[1],而基于锁相环的CDR设计又是很热门的方案,作为其核心部分的锁相环直接决定了CDR系统的性能。

电源和衬底噪声对锁相环有较大影响,由传递函数可看出环路对噪声来说是个低通滤波器,因此可知环路带宽越窄,抖动越小[2]。考虑到面积方面,由于单片集成的要求使得环路滤波器的电容无法做到很大。稳定性方面的要求则限制着带宽的拓展。环路滤波器的截止带宽与电荷泵充放电电流的大小及压控振荡器的增益对PLL带宽有着直接的影响。本设计采取的方案是对环路滤波器的模拟电压进行实时监控,以动态改变锁相环的电荷泵电流、环路滤波器的电阻值和压控振荡器的增益来调整锁相环系统的环路参数,从而使锁相环能够较稳定地跟踪速率变化极宽的数据流[3-8]。

目前有很多基于锁相环的CDR电路设计与讨论,但很少有专门应用于输入数据流变化极宽的CDR系统的锁相环设计。本设计的目的在于提供可以工作于输入数据流变化范围10 Mbit/s~2.5 Gbit/s的时钟数据恢复核心部分的锁相环前端电路设计。

1 电路模块设计

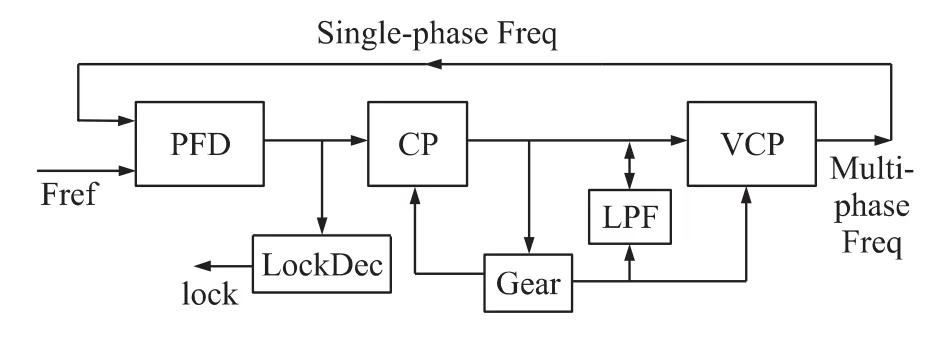

图1为应用于CDR系统的核心部分锁相环信号链路框图。其中包括鉴频鉴相器(PFD)模块、电荷泵(CP)模块、环路滤波器(LPF)模块、压控振荡器(VCO)模块、换挡电路(Gear)模块、锁定指示器(LockDec)模块。

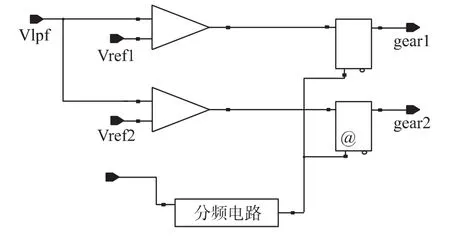

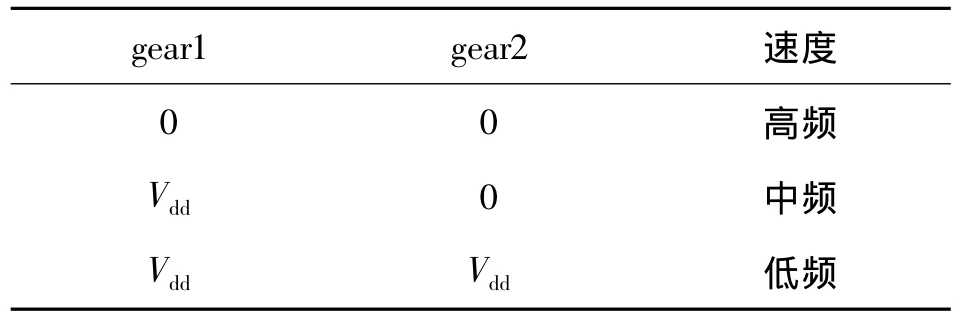

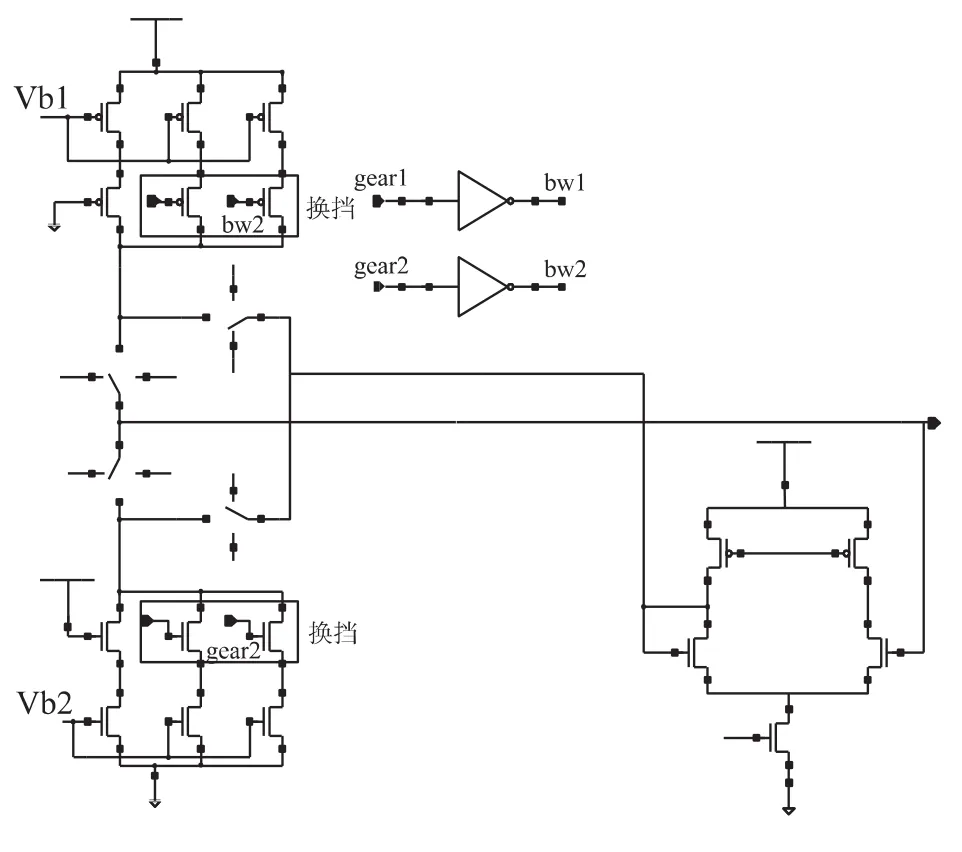

与经典锁相环结构相比此设计中的亮点就是增加了换挡电路模块与状态检测电路模块,结合环路特点可以将变化范围较大的输入参考频率Fref分为高、中、低三个区间,从而在每个区间优化环路参数,使锁相环性能达到最佳状态,换挡电路如图2所示,具体过程是由换挡电路模块监测LPF的模拟电压大小来调换档位gear1、gear2,也即同步调整CP充放电流、LPF电阻值、VCO振荡频率。锁定指示器模块主要是对up(上)、dn(下)信号的处理从而来判断环路是否锁住[9]。

图1 多相位锁相环电路框图

图2 换挡电路原理图

下面分模块介绍具体电路设计:

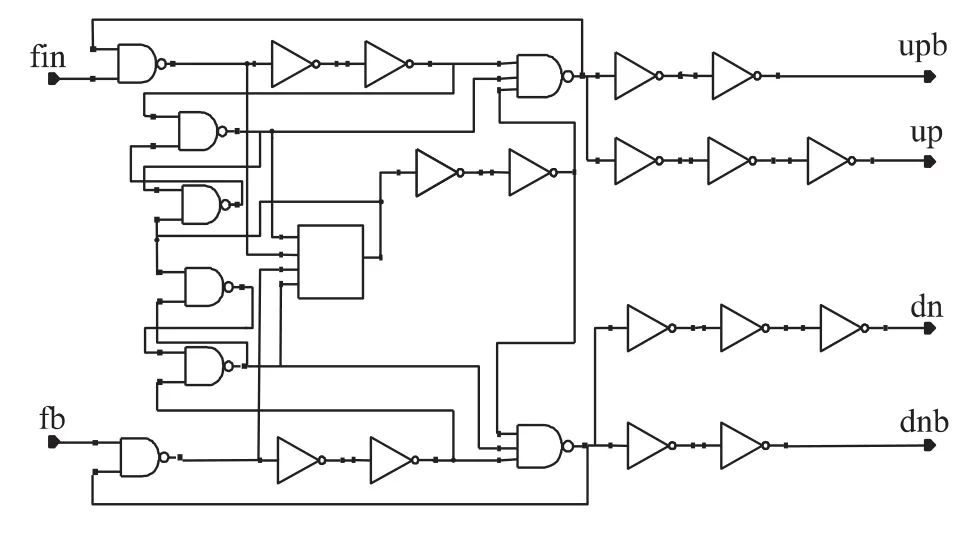

1.1 鉴频鉴相器(PFD)模块

传统的鉴频鉴相器存在“死区”与信号延迟时间不同等问题,都会造成VCO的不必要的抖动。因此我们对传统PFD做了如下改进:第1,在传统鉴频鉴相器中的四输人与非门后增加延迟电路,推迟复位信号,从而使输出的up、dn信号的脉冲宽度变宽解决“死区”问题[10],电路如图3所示。第2,四输入与非门采用如图4所示电路设计,此设计使得任意输入为低时都可以很快传递到输出端,解决信号延迟不同问题。

图3 改进型PFD原理图

1.2 电荷泵(CP)模块

传统电荷泵中主要存在的不理想特性主要包括: (1)电流失配;(2)电荷注入;(3)时钟馈通;(4)电荷分享。电流失配一般主要是由电荷泵中的电流镜不匹配引起,在设计时可以通过加强对版图规划与增加管子的宽度来削弱其影响。电荷注入、时钟馈通引入的误差一般可以通过将控制信号的输入管尽量远离电容来减小。同时为了调节环路的稳定性,本设计创新的引入了gear1、gear2两个辅助“换挡”控制信号,贯穿于电荷泵、环路滤波器、压控振荡器的调节。gear1、gear2提供了3个可选档位,如表1所示。图5为本设计所采用的可控电流型电荷泵原理图,通过自举的方式有效消除了电荷共享的影响。

图4 四输入与非门原理图

表1 档位表

图5 CP原理图

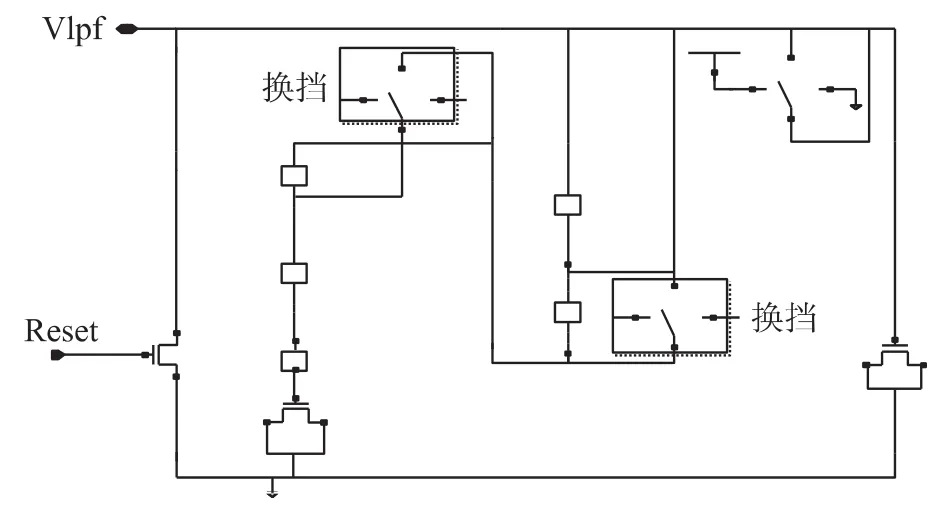

1.3 环路滤波器(LPF)模块

传统一阶环路滤波器存在稳定性问题,会对控制电压产生影响从而产生严重的相位噪声和杂散分量,为了使电压稳定,可以在一阶无源环路滤波器的基础上并连一个小电容,虽然使得锁相环变成三阶而产生稳定性困难,但是只要并联电容为原来电容的1/5到1/10,闭环的时间和响应就相对保持不变。同样的为配合环路参数的优化,环路滤波器采用分档制,如图6所示,控制信号gear1、gear2控制着滤波器中电阻的大小,由此来调节LPF的带宽,优化环路。

图6 LPF原理图

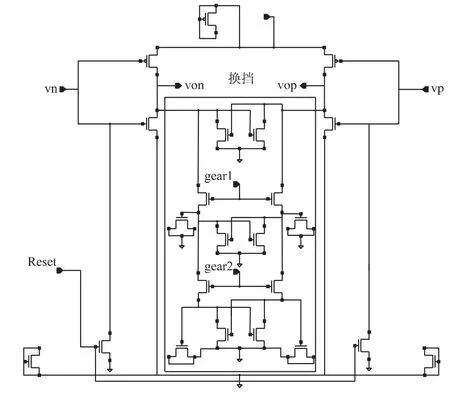

1.4 压控振荡器(VCO)模块

压控振荡器则是锁相环中最核心的部件,一方面它的工作频率范围决定了电荷泵锁相环的捕获范围,另一方面它的噪声抑制能力决定了锁相环的噪声性能。因此,它的性能好坏直接关系到整个锁相环的性能的优劣[11-12]。本设计由于采用十级Buffer的延迟,振荡器在较低频率上工作,而引入的两个控制信号gear1、gear2可以有效的调节VCO的振荡频率,使得频率在感兴趣的范围内具有良好的线性度。由噪声传递函数可以看出输出频率中的噪声正比于VCO的增益,所以要使噪声效应减到最小,其增益必须最小,这与调节的范围是直接矛盾的,所以本设计根据调节gear1、gear2控制信号较好的减小了这种矛盾。如图6所示,在输出端增加了饱和增益级电路从而保证了全摆幅的输出信号,图8为延时级单元电路,电路中gear1、gear2控制信号的产生由监测LPF滤波后的电压来调整。

图7 VCO原理图

图8 延时级原理图

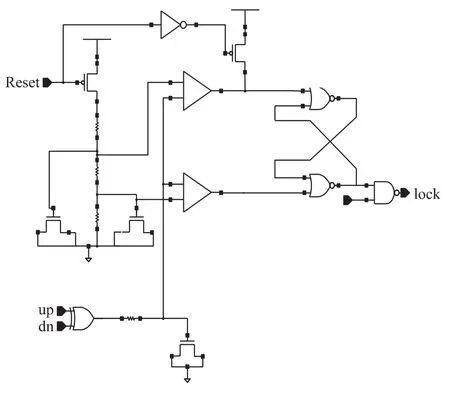

本设计还增加了一个特色功能:锁定指示器。如图9所示,当环路进入锁定状态后,输出端Lock信号将输出高电平做出指示,由此可以很直观的判断电路的工作状态。

图9 锁定指示器

2 仿真结果及分析

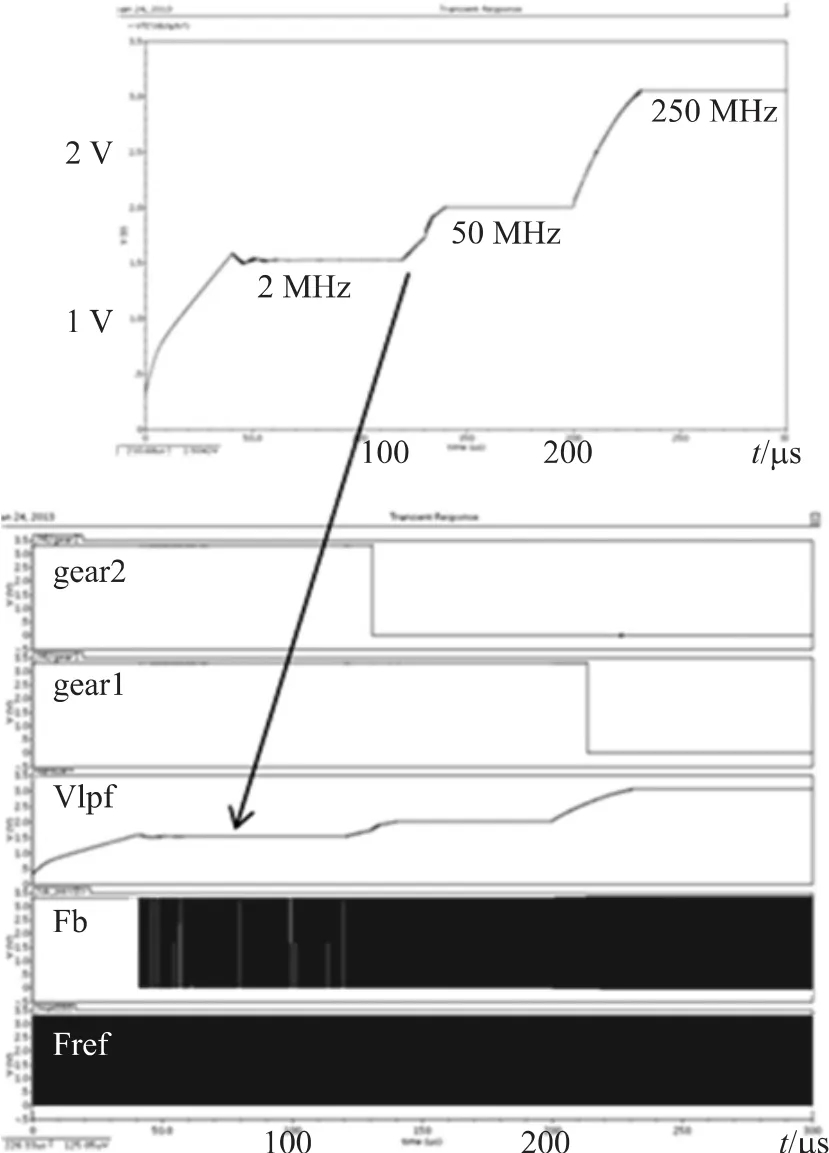

设计采用一种3.3 V的单供电电压0.18μm CMOS工艺进行仿真,输入参考频率分别采用2 MHz、50 MHz、250 MHz连续变化的方波,Cadence环境下锁相环仿真结果如图10所示,结果表明此锁相环可以工作于频率变化为2 MHz~250 MHz的情形下,换挡信号gear1、gear2有效地控制了环路参数的变化,由仿真结果图可以明显看出在换挡信号切换的时候环路滤波器的电压有着明显的变化趋势。

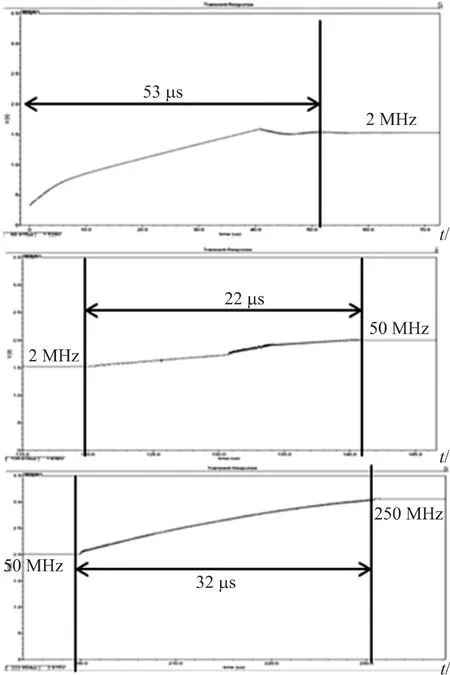

在不同状态转换所需时间上电路有着良好的相应性能,如图11所示,电路由初始态到稳定到低频段2 MHz用时53μs,在低频段转换到中频段即2 MHz~50 MHz切换用时为22μs,在中频段向高频段切换时即50 MHz~250 MHz也仅仅用了32μs,可以看出电路的响应性能是相当良好的。

图10 仿真结果

图11 稳定时间

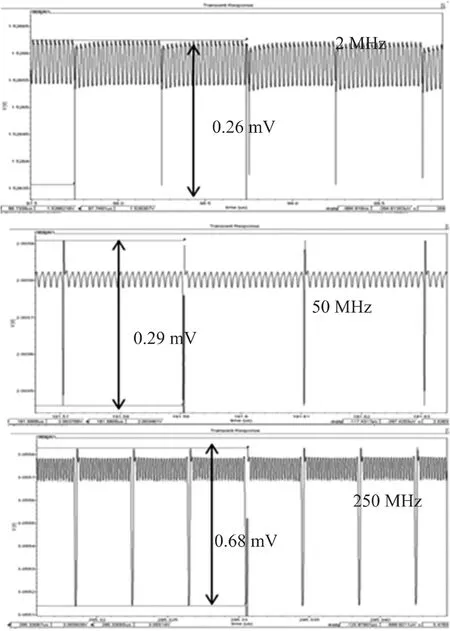

在电路稳定工作后其噪声所产生的抖动也是比较小的,如图12所示,在低频段2MHz时抖动幅值为0.26 mV,在中频段50 MHz时抖动幅值为0.29 mV,在高频段250 MHz时抖动幅值也仅为0.68 mV,所以电路在抑制噪声抖动方面也有着不错的表现。

图12 抖动幅值

3 结论

本文设计了一种应用于CDR系统的多相位锁相环电路,该电路采用3.3 V单供电电压0.18μm CMOS工艺设计,仿真结果表明该电路可以很好的工作于数据流变化极广的应用中,由于此设计是十相位输出,因此CDR可处理数据流变化范围为10 *Freq(20 Mbit/s~2.5 Gbit/s),与一般锁相环相比有着覆盖速率范围广、高稳定性、响应速度快等优点,该电路采用了新颖的设计思路,通过对滤波器模拟电压的监控从而动态改变环路参数使得锁相环性能达到最佳状态,相信该设计经过工艺的进一步优化和版图设计,其IP核将完美的服务于宽速率CDR系统。

[1]张长春,王志功,吴军,等.5 Gb/s 0.18μm CMOS半速率时钟与数据恢复电路设计[J].微电子学,2012,42(3):17-21.

[2]Behzad Razavi.模拟CMOS集成电路设计[M].陈贵灿,程军,张瑞智,等译.西安:西安交通大学出版社,2003.

[3]Savoj J,Razavi B.A 10-Gb/s CMOSClock and Data Recovery Circuitwith a Half-Rate Linear Phase Detector[J].IEEE Journal of Solid-State Circuits,2001,36(5):761-767.

[4]Jin Kyu Kwon,Tae Kwan Heo,Sang-Bock Cho,et al.A 5-Gbp/s 1/8-Rate Cmos Clock and Data Recovery Circuit[C]//Iscas 2004:IV-294-296.

[5]Seedher A,Sobelman G E.Fractional Rate Phase Detectors for Clock and Data Recovery[C]//IEEE 2003:313-316.

[6]Beshara M.Design Considerations for High Speed Clock and Data Recovery Circuits[C]//A Thesis for the Degree of Master of Applied Science,Ottawa-Carleton Institute for Electrical Engineering,Carleton University 2002:23-24

[7]李义慧,冯军,王远卓,等.10 Gb/s时钟恢复与数据判决单片集成电路的设计[C]//全国第十三次光纤通信即第十四届集成光学学术论文集.2012:6.

[8]白冰,郭玉彬,赵晓晖.多速率接收及时钟数据恢复光纤激光传输实验研究[J].半导体光电,2012,33(2):47-52.

[9]张长春,王志功.高速时钟与数据恢复电路技术研究[J].电路与系统学报,2012,17(3):67-71.

[10]陈一辉.高速低噪声锁相时钟发生器的设计[D].上海:复旦大学,2008.

[11]王勇.高速时钟恢复系统的研究[D].上海:复旦大学,2009.

[12]叶君青.用于1.25 Gb/s千兆以太网的时钟数据恢复电路的设计[D].上海交通大学,2008.

一种用于时钟数据恢复的宽带锁相环设计*

王 旭1,2,朱红卫1

A W ide-Band PLL Circuit Design Applied in CDR*

WANG Xu1,2,ZHU Hongwei1

(1.Huahong NEC Electronics Co.Ltd.,Shanghai201206,China;2.Software College,Southeast University,Nanjing210096,China)

PLL has been widely used in the area of communications.A new type of PLL applied in CDR was proposed which including six parts(phase frequency detector,charge pump,loop filter,voltage controlled oscillator,gear generation,lock detector),and adopting theway ofmonitoring the voltage of LPF to dynamically adjust system parameters.It can meetwell the demand that the input data vary from 10 Mbit/s to 2.5 Gbit/s in CDR.Detail simulation was given at the Cadence design environmentwith a 3.3 V single voltage 0.18μm CMOS process.

PLL;CDR;wide band;multi-phase

10.3969/j.issn.1005-9490.2013.06.017

TN761 文献标识码:A 文章编号:1005-9490(2013)06-0828-05

项目来源:国家集成电路项目(2009ZX02303)

2013-03-20修改日期:2013-04-09

EEACC:1250;1265E

王 旭(1987-),男,江苏省沛县,汉族,现于东南大学攻读硕士学位,主要研究方向为模拟集成电路设计。目前任于上海华虹NEC电子有限公司设计开发部实习工程师。参与国家集成电路项目《0.18微米/0.13微米锗硅BiCMOS成套工艺技术》,wangxu@hhnec.com,wangxu1988wo@163.com;

朱红卫(1968-),男,1997年毕业于上海交通大学微电子所,获博士学位,现任上海华虹NEC设计主管,同时被聘为上海交通大学微纳技术学院兼职教授,长期从事模拟和射频电路设计,在国内外发表论文三十余篇,获专利授权10项,申请20多项。