基于FPGA的时间间隔测量系统的设计

2013-09-27电子科技大学能源科学与工程学院成都611731

(电子科技大学能源科学与工程学院,成都611731)

(电子科技大学能源科学与工程学院,成都611731)

为了解决电容充放电放大电路测量时间间隔的不稳定,采用复杂可编程芯片FPGA设计实现精密时间间隔的测量。FPGA的锁相环(PLL)电路得到高频时钟,时钟管理器(DCM)实现高速时钟移相,产生的内插时钟得到高精度时间测量。通过在光电回波脉冲时间间隔测量系统中验证,该设计可以得到200ps的时间间隔测量精度。采用FPGA芯片设计的粗和细数字化测量系统,具有集成度高,性能稳定,抗干扰强,设计方便等优点,能广泛应用于科研和生产中。

时间间隔测量;FPGA;时钟管理器;内插时钟

精密时间间隔测量在科研实验和实际生活生产中都有广泛的用途。而且随着科技的高速发展,人们对高精度测量的时间频率也越来越高。传统的测量方法很多,比如根据电容充电时间与电容电压成线性关系而设计的电容放大电路[1],以及由此改进的时间延展回路[2-3]。这种模拟测量方法的优点是结构简单,测量精度高,但是由于电容测量有一个充放电过程,在高频下不稳定,影响测量结果。科研领域中所依赖的专用时间间隔测量芯片主要是采用内部延迟[4-9],比如门延迟来实现时间内插,然后经流片制成。这种芯片测量精度高,而且性能稳定,但是制作周期长,性能单一,价格非常昂贵。针对上述优缺点,本设计结合国内外发展现状,用可编程逻辑芯片FPGA实现时间间隔测量,不仅可以达到精密时间间隔测量目的,而且可编程实现与计算机串口通信,使用方便,成本也低廉。

1 系统总体结构及基本原理

1.1 系统结构

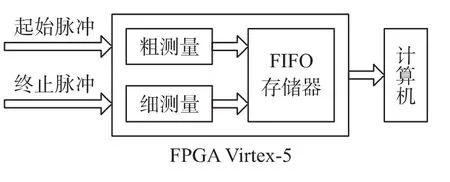

时间测量需要有大的测量范围和高的测量精度,本设计用FPGA用“粗”时间计数(获得大的测量范围)加上“细”时间测量(高的测量精度)的方法测量位置信息。起始和终止信号脉冲前端处理后转换成数字脉冲,经过FPGA芯片内部“粗”和“细”时间测量,“粗”和“细”时间测量结果存储在FIFO中,最后经整合经串口送到PC机(图1)。

图1 系统结构

1.2 测量原理

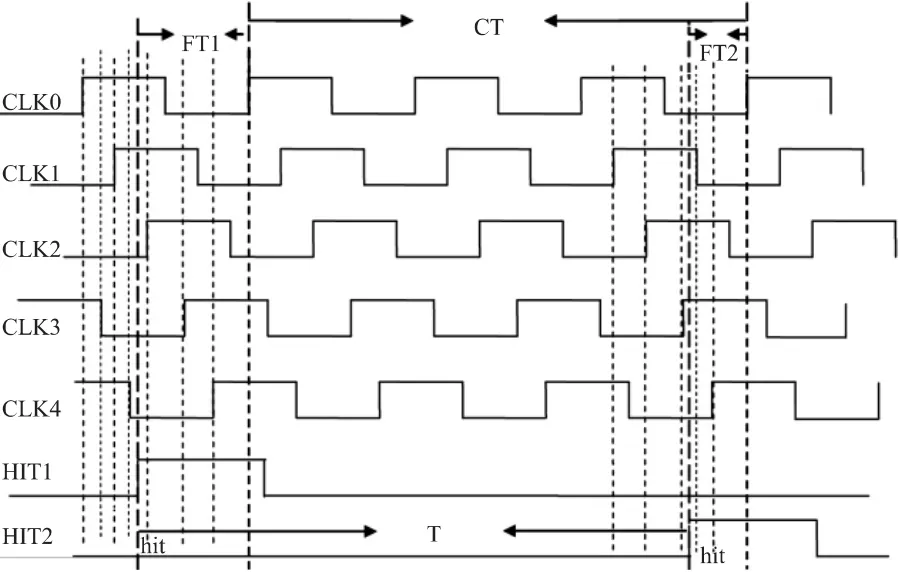

“粗”时间测量由高速时钟计数,如图2所示,CLK0为内部时钟,HIT1为计数开始信号,HIT2为计数停止信号。计数值为从HIT1信号有效后第一个上升沿开始计数,直到HIT2信号有效时的前一个CLK0的上升沿时停止计数。计数值乘以2 ns即为“粗”时间。根据计数器的原理,“粗”时间间隔测量的最小量化误差为一个计数周期,即2 ns。

图2 内插法原理图

“细”时间测量由内插法来测量。时间内插测量原理如图2所示,CLK0、CLK1、CLK2、CLK3、CLK4为内插时钟,相位相差2π/5.这样5个时钟组成的内插数据位CLK[4…0](这里只有11001、10001、10011、00011、00111、00110、01110、01100、11100、11000共10种情况)相当于把一个时钟周期等分为10分。当CLK频率500 MHz时,周期2 ns,那么每一等分的时间间隔为0.2 ns。

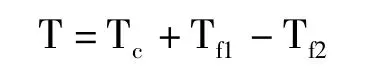

测量的时间间隔为T,则

其中Tc为“粗”时间,Tf为“细”时间。“细”时间的测量是在HIT有效(上升沿)的瞬间,把由CLK组成的内插数据CLK[4…0]锁存起来。通过分析CLK[4…0]的数值来确定Tf的大小。“细”时间测量是为了克服“粗”时间测量带来的误差。每个CLK0被等分成10分,经“细”时间测量后,最小量化误差为0.2 ns,即变为原来的1/10.从图中也可以看出“细”时间Tf与内插数据CLK[4…0]之间的关系。内插数据CLK[4…0]11001、10001、10011、00011、00111、00110、01110、01100、11100、11000分别对应的“细”时间Tf为1.9、1.7、1.5、1.3、1.1、0.9、0.7、0.5、0.3、0.1(单位ns)。

2 系统组成及设计

根据测量原理,测量系统主要包括以下几部分:

2.1 内插时钟信号的产生

采用FPGA内部的锁相环模块,每个锁相环模块可以提供多路频率可调,相位可调的时钟信号,因此我们可以用锁相环模块来产生所需要的内插时钟CLK。或者采用IODELAY,Xilinx的Virtex-5芯片均包含两个IOB、两个ILOGIC、两个OLOGIC和两个IODELAY,IODELAY1为可编程绝对延迟单元,具有32个Tap的环绕延迟单元,具有标定的Tap分辨率。IODELAYE1允许各输入信号有独立的延迟。在规定的范围内选择IDELAYCTRL参考时钟,可以改变Tap延迟分辨率。IODELAYE1资源可用作IDELAY、ODELAY或组合延迟。IDELAYE1允许各输入信号有独立的延迟。延迟单元可以被校验到一个绝对延时固定值(TIDELAYRESOLUTION),这个值不随工艺,电压和温度的变化而改变。IODELAYE1有4种操作模式:分别是零保持时间延迟模式(IDELAY_TYPE=DEFAULT)、固定延迟模式(IDELAY_TYPE=FIXED)、可变延迟模式(IDELAY _TYPE=VARIABLE)和可装载的可变延时模式(IDELAY_TYPE=VAR_LOADABLE)。从设计简便考虑,本次设计选用固定延迟模式,Xilinx的Virtex -5系列FPGA芯片有32条全局时钟线,它们可以对整个器件进行时钟控制或驱动逻辑信号。时钟管理技术(CMT)包含两个DCM和一个PLL。用FPGA内部的PLL(或DLL)倍频得到500 MHz频率,然后DCM移相[10],后面时钟每次相位延迟2π/5。经过PLL后相位锁定,PLL可以补偿网络延时和时钟去歪斜。Xilinx FPGA内部的Ip核有时钟管理模块,直接调用该模块可以方便设计。

2.2 “粗”时间测量

针对第1个参考时钟CLK0计数。考虑到在500 MHz频率下计数器由于亚稳态的干扰而产生误差,本设计采用格雷码计数器。格雷码计数值的前后变化只有相邻的1位发生变化,可以降低了多位bit同时变化带来的毛刺,也就降低了噪声[11]。

2.3 “细”时间测量

“细”时间测量在脉冲边缘读取5列时钟的值,VHDL设计上升沿触发的锁存器要实现。测量值保存进FIFO中。为了保证严格的时序,“细”时间测量与“粗”时间测量同时进行。高速信号中,由于时钟周期不是远远大于信号延迟时间,所以需要严格的分析芯片内部连线,使内部延时尽量一致,减少误差。

2.4 数据的运算存储。

为了读写方便,采用FIFO保存数据,FIFO可以采用FPGA内部存储模块IP核实现。FPGA使用RS232串口将数据上传至计算机。计算机完成时间间隔数据值运算和显示。

3 实验结果及仿真

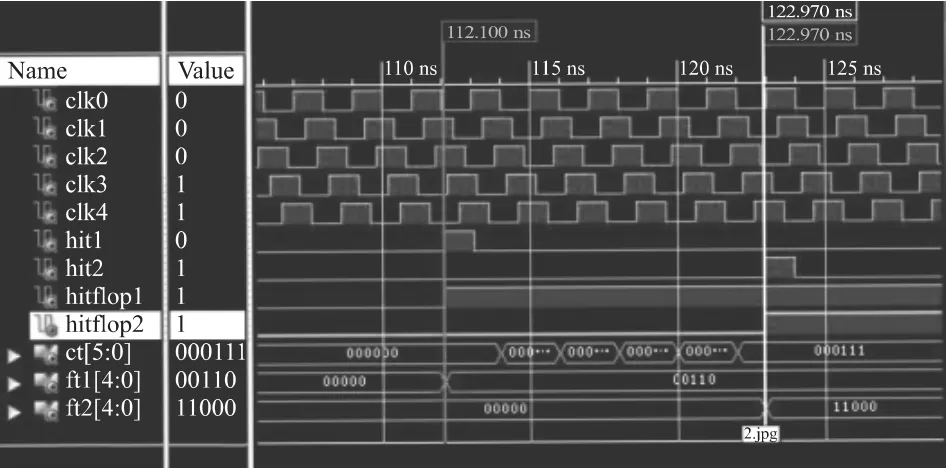

实验仿真芯片采用 Xilinx的 Virtex-5芯片XC5VLX50,该芯片内部集成DCM和DLL管理时钟,Speed Grade=-3,16bit计数器最高工作频率550 MHz,能满足设计要求。

实验测试中,Hit1的脉冲时间在112.1ns,Hit2的脉冲在122.97ns,脉冲宽度均为1ns,时间间隔为10.87ns。测量结果如图3所示。

图3 仿真结果

Hitflop1和Hitflop2是两个脉冲经触发器检测到上升沿之后的波形,Tc是粗时间间隔,格雷码表示的值为000111,十进制数是5,所以粗时间间隔是5×2 ns=10 ns。Tf1是Hit1的细时间间隔,Tf1是00110,所以Tf1=0.9 ns。Tf2是11000,Tf2=0.1 ns。测量的时间间隔T=Tc+tf1-tf2=10+0.9-0.1=10.8 ns。时间测量误差δ=0.07 ns。实验误差比较小,可以达到精密测量的目的。

4 结论

本设计结合国内精密时间间隔测量的发展现状,用数字方法,采用“粗”加“细”两种测量方法相结合的方法进行时间间隔测量,不仅提高了精度,而且可以获得大的测量范围,同时没有模拟内插法带来的时间抖动。利用FPGA内部的时钟管理器(DCM)和锁相环(PLL)可以获得比较稳定的内部时钟。高频稳定的时钟是进行该测试的前提,Xilinx新推出的很多芯片已经能工作到500 MHz以上,为高频测量和设计提供了方便。本设计是数字化测量,抗干扰能力强,稳定性实用性高,在科研生产中有一定的价值。

[1]安琪.精密时间间隔测量及其在大科学工程中的应用[J].中国科学技术大学学报,2008,38(7):758-764.

[2]范晓东,刘光斌.精密时间间隔测量系统方案设计[J].无线电工程,2010,40(9):55-57.

[3]于建国,陈明,唐渭.精密时间间隔测量方法的改进[J].宇航计测技术,2003,23(3):15-20.

[4]唐晓文,刘亚强,崔均健.基于FPGA进位链TDC延时模型的建立与性能测试[J].核电子学与探测技术,2011,31(3):267-273.

[5]朱寅非,吴云峰,唐斌.超高速数字分幅相机中快门控制电路设计[J].电子器件,2012,35(5):611-614.

[6]陈柄权.基于FPGA中专用进位连线的精密TDC设计[J].湘潭大学自然科学学报,2008,30(1):51-55.

[7]杨立涛.基于FPGA的精密时间间隔测量[D].兰州:兰州大学,2011:20-34.

[8]宋健.基于FPGA的精密时间-数字转换电路研究[D].中国科学技术大学,2006:53-64.

[9]Aloisio A,Branchini P,Giordano R,et al.High-Precision Time-to-Digital Converter in a FPGA Device[R].IEEE Nuclear Science Symposium Conference Record,2009:290-294.

[10]吴帅,刘凯,徐欣.Virtex-5中动态DCM的设计方法[J].单片机与嵌入式系统,2008(4):44-47.

[11]李莉.基于FPGA的多位格雷码计数器[J].科学技术与工程,2009,9(23):7158-7161.

基于FPGA的时间间隔测量系统的设计*

瞿 鑫,吴云峰*,江 桓,李华栋,郑天策

Design of Time Interval M easurement System Based on FPGA*

QU Xin,WU Yunfeng*,JIANG Huan,LIHuadong,ZHENG Tiance

(School of Energy Science and Engineering,University of electronic science and technology,Chengdu611731,China)

In order to solve the instability of the charge and discharge of capacitance in amplify circuitmeasurement time interval complex programmable FPGA chip is adopted to design and realize the precise measurement of the time interval.We use Phase-Locked Loop(PLL)and Digital Clock Manager(DCM)circuit of FPGA to realize interpolation of clock.Through verification in photoelectric echo pulse time intervalmeasurement system,we get a precision of 200ps time intervalmeasurement.The system of coarse and finemeasurement based on FPGA is characterized by a high level of integration,stable and reliable performance,strong anti-interference.It can be widely used in scientific research and production.

time intervalmeasurement;FPGA;digital clock manager;interpolation of clock

10.3969/j.issn.1005-9490.2013.06.016

TN702 文献标识码:A 文章编号:1005-9490(2013)06-0825-03

项目来源:中国工程物理研究院流体物理研究所资助项目

2013-04-02修改日期:2013-04-21

EEACC:7210

瞿 鑫(1989-)男,汉族,湖南衡阳人,电子科技大学硕士研究生,主要研究方向为光电测控与精密仪器(电路系统),quxinnh@126.com;

吴云峰(1972-)男,汉族,电子科技大学光电信息工程学院博士,能源科学与工程学院副教授,研究生导师,主要研究方向为光电检测仪器,功率变换器与智能控制系统。在电子科技大学工作期间,作为课题负责人,完成了总装新品项目和横向课题10余项,总经费超600万;独立或合作发表论文90余篇,一级学报发表论文20余篇,yfwu-72@163.com。