基于FPGA的数字通信实训平台的设计与实现

2013-09-26徐宏庆

王 俊 , 徐宏庆

(正德职业技术学院 江 苏 南 京 2 11106)

通信系统的全面数字化是通信发展的必然趋势。高职院校以《数字通信系统》替代《通信原理》符合行业的发展和企业对人才素质需求。作为电子信息类专业核心课程,由于课程内容抽象,理论较深,必须借助实验环节来帮助学生理解。而传统的通信原理实验仅仅是对系统中单元模块进行原理的验证,学生无法在实验中建立系统的概念,严重影响了后续专业课程的学习。

目前市场上的通信原理实验箱大多以本科《通信原理》课程为设计蓝本,主要开展单元电路的验证性实验。这显然不能满足高职层次的培养目标,难以推动学生的专业技能的提升。

本实训平台采用了模块化设计,只需更换相应模块,就可以完成不同的实验。同时充分考虑到构建系统概念的重要性,在设计系统实验时,学生需要掌握了最基本的通信系统组成要素,才能完成实验,这对于强化学生的系统概念,起到了很大的作用。

1 平台设计方案

本数字通信实训平台将各个单元实验模块与数字通信系统的模型有机的结合到一起,并充分考虑到实际通信电路与传统通信实验电路的差别,设计了如图1(a)所示的平台结构。实训平台分为两个部分:硬件实验区和软件实验区。

1.1 硬件实验区

根据数字通信系统模型,设计制作了FPGA核心开发板、信号源模块、信源编码模块、信道编码模块、数字调制模块、数字解调模块、同步模块、信源译码模块、信道译码模块。学生既可以通过完成各个单元电路的实验,了解通信中重要的性能指标,又可以通过各单元模块组成数字通信系统,熟悉构建通信系统的基本要素,强化系统概念。

1.2 软件实验区

基于FPGA核心开发板,首先为硬件区电路提供各种工作时钟信号,其次学生可以通过VHDL语言编程实现各个实验模块的功能。在软件实验区,还设计了功能测试区,学生将软件下载至核心开发板中,可以开展信号测试与软件调试等相关实验。最终,以FPGA开放模块为核心,利用软硬件平台把相关模块进行整合,将数字通信系统构建在一个芯片的内部。SOC(片上系统)是目前通信系统的最佳实现方案,让学生初步建立SOC的基本概念并了解通信系统设计流程,有助于他们的职业发展。

2 系统硬件设计

图1 实训平台与FPGA开发板结构图Fig.1 Structure diagram of platform and FPGA development board

实训平台的硬件设计充分考虑其实用性,易操作性以及与实际通信系统的结合度,并结合高职教育特点,采用了6+2的设计模式。其中“6”是实现数字通信的基本模块:FPGA核心开发板、模拟信号发生模块、信源编解码模块、信道编解码模块、数字调制与解调模块、信号输出模块。“2”是两个扩展模块:无线数字通信发射模块和无线数字通信接收模块。限于篇幅原因,本文主要介绍FPGA核心开发板。

2.1 核心开发板功能

1)为硬件实验区模块提供时钟信号、伪随机序列等各种工作信号;

2)为软件实验提供开放的硬件平台,使得实验结果更加直观;

3)开展电子设计开发和验证,提升学生的综合软硬件设计创新能力。

开发板电路包括:主芯片电路、晶振电路、电源电路、下载接口电路、扩展接口电路以及测试区电路。结构框图如图1(b)所示。

2.2 主芯片电路

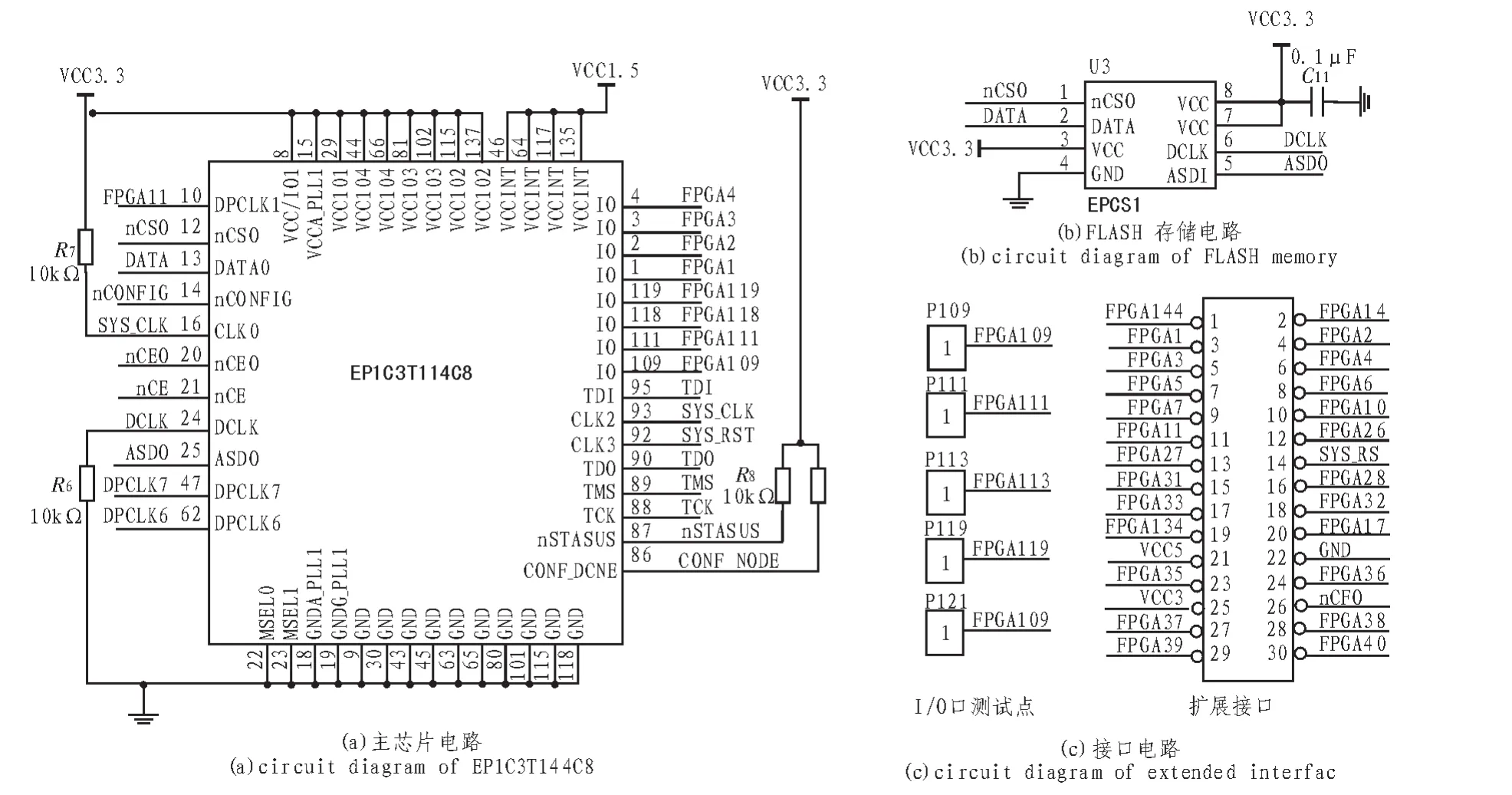

本设计选用Altera公司的Cyclone系列芯片,型号为EP1C3T144C8,该芯片是Altera公司推出的低价格、高容量的FPGA,在实际应用中被广泛的采用。电路图如图2(a)所示。

2.3 FLASH存储电路

由于FPGA芯片掉电后程序丢失,为保存程序数据,要在硬件上增添存储电路。本设计采用标准串行配置器件EPCS1,存储容量为1Mbit的FLASH存储芯片。电路图如图2(b)所示。

2.4 I/O接口电路

为了加深学生对通信系统硬件电路工作过程的理解,将部分I/O口通过独立测试孔的方式设计在开发板上。学生通过程序,将输出信号设定在预留的I/O口,然后以导线连接的方法,将信号送至相关模块的电路中。实物照片如图2(c)所示。

2.5 扩展接口电路

扩展接口有2组15×2的排针,除了引出其余的I/O口,还将VCC、GND以及CLOCK等也设计在扩展接口。这为后续扩展外围电路提供了极大的方便。其中VCC具有多种电压,可以满足不同器件的使用。电路图如2(c)所示。

3 系统软件设计

软件设计采用QuartusⅡ9.0进行开发,设计分为两个层次:一是主要实现时钟信号产生、信源编译码模块、信道编译码模块以及数字调制解调等数字通信系统中单元电路的软件功能;二是基于软件无线电设计思路,通过Quartus自带的SOPC Builder设计出贴合实际产品功能的可编程片上系统。

3.1 基本功能

以分频模块为核心,为基本实验模块提供必要的时钟信号,学生可以通过编程改变时钟信号频率,改变电路工作状态,从而加深对电路原理的理解以及实际电路调试步骤。

在设计软件模块时,还充分考虑相关模块在通信系统中逻辑关系,通过软件可将基本模块进行连接,实现最简化的数字通信系统。

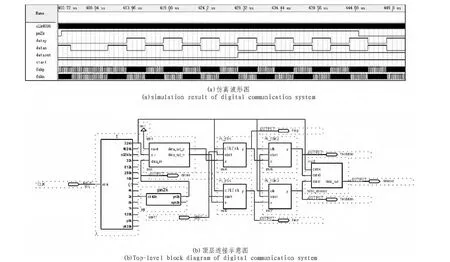

3.2 系统模型设计

顶层连接图如图3(b)所示。FPGA开发板上的20 MHz有源晶振作为总的时钟信号输入,经过分频模块t分频后可以产生多种频率的时钟信号,其中2 kHz作为输入时钟送入m序列模块(pn2k),产生2n-1位PN序列,该序列作为数字基带信号用于系统的信源输入。

信道编译码选用HDB3码编码方式,将PN序列送至hdb1模块中进行编码,由于HDB3码是一种双极性码,而QuartusⅡ软件它无法识别-1,在它的波形仿真中只有1和0,因此这里采用了双路输出,其中datap中的高电平代表的是HDB3码中的+1,datan的高电平代表HDB3码中的-1,将两路信号相减即可得到相应的HDB3码。编码模块的时钟信号为32 kHz,由分频模块提供。

两路信道编码信号datap和datan分别送入两个数字调制模块PL_FSK,本设计中采用了2FSK的调制方式,两个载波由分频模块提供的1.024 MHz信号,分别经过12分频和6分频得到。其两路已调信号输出端口为fskp和fskn。

图2 FPGA核心开发板电路图及实物图Fig.2 Circuit diagrams and picture of FPGA development board

上述为发送端模块的分析,下面简单介绍接收端模块的设计流程。

两路已调信号fskp和fskn分别送入数字解调模块PL_FSK2,设计思路是分别对已调信号和clk分频信号进行计数,然后对两个计数值进行判决,从而还原出两路基带信号 fskdatap和 fskdatan。

将fskdatap和fskdatan送入信道译码模块hdb3_decode,根据HDB3码的特点首先检测出极性破坏点,即找出4连零码中添加V码的位置(破坏点位置),其次去掉添加的V码,最后去掉4连零码中添加的B码以将其还原成NRZ码PN序列dataout。

以上就是通过软件实现基本数字通信系统的整个设计流程,仿真波形如图3(a)所示。

图3 数字通信系统FPGA软件实现Fig.3 Digital communication system with FPGA software design

其中,clk为系统输入总时钟,pn2k为数字基带信号 (伪随机码),start1为数字调制解调模块使能信号,datap代表HDB3码中+1的波形,datan代表HDB3码中-1的波形,fskp为datap的FSK已调信号,fskn为datan的FSK已调信号,dataout为译码后的数字基带信号(与pn2k一致,但有延迟)。

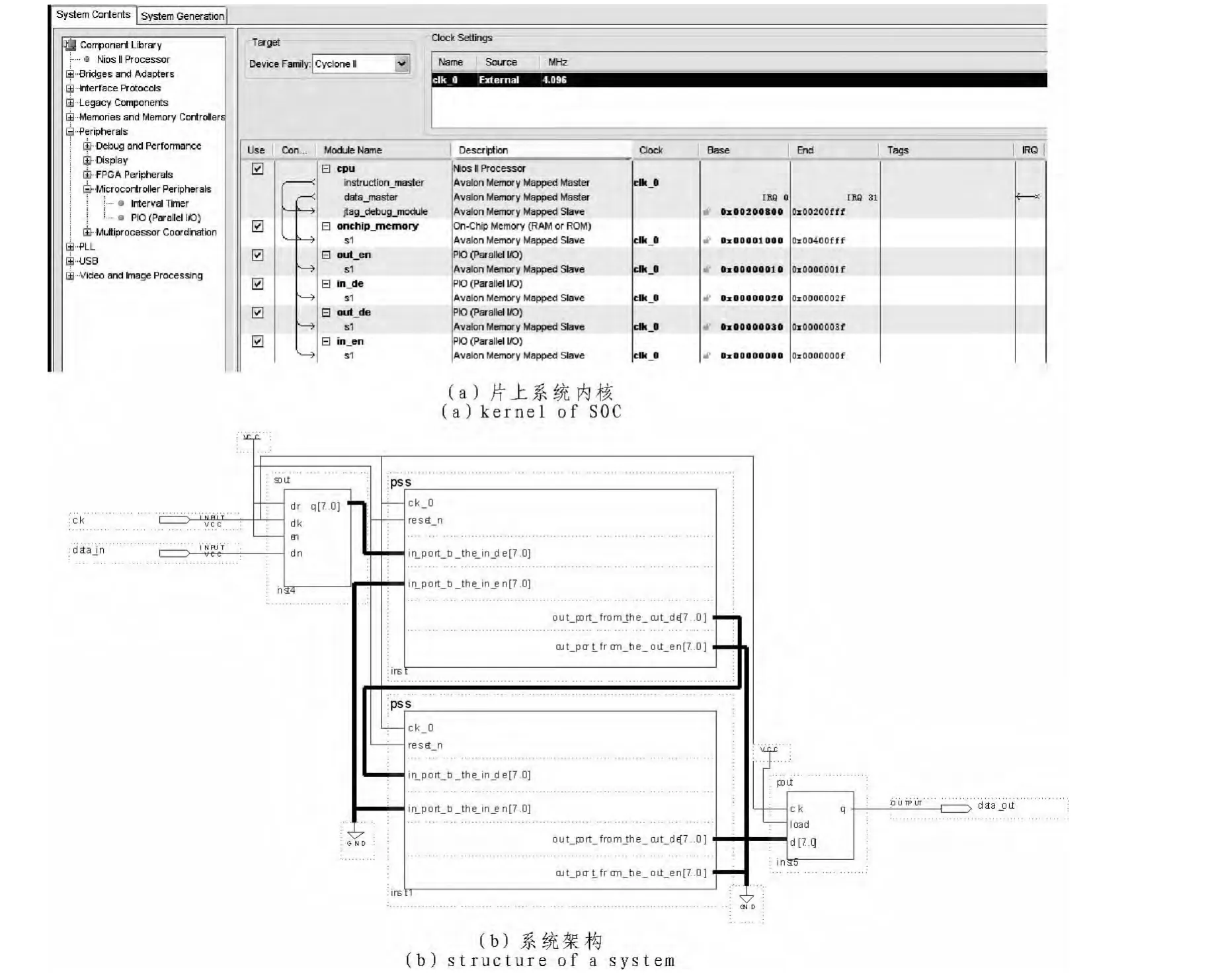

3.3 片上通信系统的设计

利用QuartusⅡ自带的SOPC Builder可以较为简单的设计出符合要求的可编程片上系统,以核心开发板上的晶振为基准时钟,通过片内PLL可以进行分频或倍频操作。将编译码模块与位同步模块以及调制与解调模块连通后,片上系统基本可以实现对高速数据准确、安全的发送和接收,片上系统 CPU内核如图4(a)所示,系统总体架构如图4(b)所示。

图4 片上数字通信系统Fig.4 Digital communication system on a chip

4 系统实测

为保证高职层次的学生能够更加直观的了解掌握数字通信系统的相关概念,为后续专业技能培养奠定坚实的基础。整个实训平台的实现围绕着FPGA核心开发板,采用了分层递进的实验模式,逐步培养学生的相关专业技能。

4.1 采用硬件模块搭接的方式构建系统

通过实训平台中各个单元模块,按照数字通信系统的基本模型,进行输入输出信号的连接。FPGA核心开发板主要为各个模块提供所需的时钟信号、伪随机码等工作信号。学生在构建最简化的数字通信系统过程中,一方面巩固了通信系统的基础知识,另一方面也锻炼了学生FPGA软件基本使用能力,为后续复杂程序编写提供技术保障。

4.2 通过FPGA软件实现通信系统模型

采用QuartusⅡ软件,运用VHDL语言及图形化编写方式,按照通信系统模型及总体程序的需求,进行分模块设计以及顶层连接。在设计软件模块时,对关键测试点进行芯片引脚设置,通过对核心开发板相关测试点进行实测,强化了学生对数字通信系统基本架构的认知,让学生掌握测试仪器的基本使用方法。同时,进一步提升学生对于FPGA软件编写的能力。 实测波形如图 5(a)(b)所示。

4.3 完成片上通信系统初步设计

随着技术发展,当前数字通信系统已全部采用了片上系统的设计方式,以可编程的硬件为平台,搭载特定的系统软件,从而实现可靠高效的通信。由于该部分实验具有一定的理论深度和技术难度,在具体教学实施中,选择部分基础扎实、动手能力强的学生进行SOPC片上系统设计实验,强化实践技能,提高他们的职业竞争力。

5 结束语

本实训平台从实际技能需求入手,贴合高职层次通信专业能力培养目标,把握数字通信系统中最核心的技术概念。采用硬件实测与软件仿真相结合的实验模式,既巩固学生对核心技术的理解,又强化学生对通信系统基本构成要素的认知,同时也让学生熟悉了现代通信系统典型的实现方法。

[1]赵菁,文时翔.FSK/PSK调制的FPGA实现[J].电子科技,2011,24(4):64-66.

ZHAO Jing,WEN Shi-xiang.FSK/PSK Modulation Base on FPGA[J].Electronic Sci.&Tech,2011,24(4):64-66.

[2]张富丽.基于FPGA通信原理实验系统的研究[D].北京:北京化工大学,2009.

[3]胡泽文.基于FPGA的FSK数字调制系统的设计 [D].成都:电子科技大学,2011.

[4]车嵘,刘波,曹剑中.基于FPGA的HDB3编解码电路的实现[J].电子器件,2007,30(6):2148-2151.

CHEN Rong,LIU Bo,CAO Jian-zhong.Encoder circuits implementation ofHDB3 basing on FPGA[J].Chinese Journal Of Electron Devices,2007,30(6):2148-2151.

[5]章丽萍,周凤星.基于EP1C3T144的最小系统开发板的设计[J].武汉科技大学学报:自然科学版,2007,30(3):293-295.

ZHANG Li-ping,ZHOU Feng-xing.Design of a minimum system development board based on the EP1C3T144[J].J.of Wuhan Uni.ofSci.& Tech:NaturalScience Edition,2007,30(3):293-295.

[6]路布新.基于FPGA的全数字QPSK通信系统的研究[D].南京:南京理工大学,2006.