双核超高压线路微机保护装置的研究

2013-09-19王惠中孙晨宇

王惠中 孙晨宇

(兰州理工大学电气工程与信息工程学院,甘肃 兰州 730050)

0 引言

当前,随着智能电网的建设,我国大规模超(特)高压输电线路已经投入运行。作为骨干网架,超(特)高压线路输送容量大、对稳定性要求极高,因此,当线路故障时,要求继电保护能在极短时间内发现并切除故障。

目前,超高压输电线路上广泛采用的是反映故障时工频电气量变化的微机保护装置。超(特)高压线路存在线路电压高、线路充电电容大、时间常数大、常规电流差动保护以及距离保护整定困难等问题。

小波分析是奇异性检测的有效工具。基于小波分析的行波差动可以利用故障行波波头信息快速检测到故障而不受充电电容、过渡电阻以及系统振荡的影响[1]。但是,小波分析运算较复杂,传统的DSP处理器仍然不能以极快的速度得到高精度的计算结果,难以发挥行波保护的速动性优势。现场可编程门阵列(field programmable gate array,FPGA)具有现场可编程、信号并行处理的优点。基于FPGA的离散小波变换具有耗时短、功耗低等特点[2]。

1 超高压输电线路故障特征

超高压输电线路采用并联电抗器来补偿分布电容的影响,以防止线路过电压,并且线路还包含串补电容,以缩短线路的电气距离。由于输电线路受参数分布特性、弧光故障、母线分布电容等的影响,超高压长距离输电线路故障时,除了包含工频信息外,还会包含相当宽频带的高频暂态分量和非周期分量。这些高频暂态分量包含了诸如故障方向、类型及持续时间等故障信息。受线路参数及故障工况的影响,故障电压初始角会显著影响各分量的幅值,但不会影响分量的频率和衰减时间常数[3]。因此,可以利用故障产生的高频行波来构成保护,用以判别线路故障位置以及类型。超高压输电线路发生故障后产生的暂态行波信号频谱范围为1~1 000 kHz。

目前,我国超高压线路全线速动主保护的动作时间大约为25 ms,而采用基于小波分析技术的超高压输电线路行波保护理论动作时间小于10 ms,这将大大缩短保护的动作时间。因此,行波保护越来越受到研究人员的青睐[4]。

2 行波保护原理

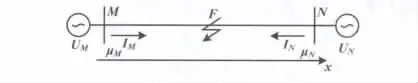

当输电线路发生故障时,由于输电线路的分布参数特性,会在线路两端产生以接近光速传播的暂态电压行波和电流行波,其示意图如图1所示。

图1 故障行波示意图Fig.1 Schematic diagram of fault traveling wave

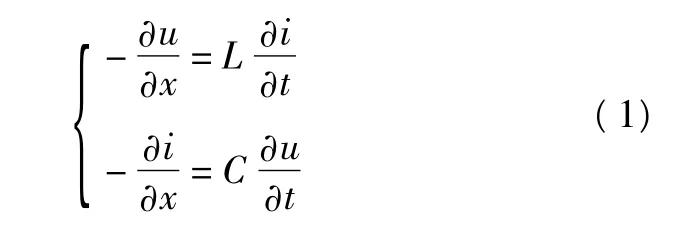

忽略导线能量损耗,则分布参数存在如下关系:

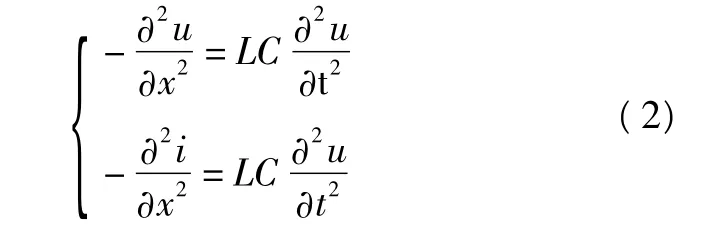

式中:L为线路的单位长度电感,H;C为线路的单位长度对地电容,F;u为线路上的电压,V;i为线路流过的电流,A;x为线路上距离起始点的位置,m;t为传播时间,s。将式(1)变换后得到如下波动方程:

式(2)的达朗贝尔解为:

输电线路故障行波的重要特征就是波德折射与反射。当行波沿导线运动时,如果线路的波阻抗在某一点突然发生改变,那么在该点将发生波的反射与折射。行波保护就是利用波动方程及波的反射、折射实现的超高速保护,它利用故障初期产生的行波电压、电流信息,检测出故障,可以实现线路超高速保护[5]。

3 故障信号的小波分析

高压输电线路发生故障后的行波初始波头、故障点反射波、母线端反射波在到达保护装置检测点时表现为明显的奇异性。奇异性包含故障的发生地点、方向、极性和幅值等信息,这些信息能否准确提取直接关系到微机保护装置的动作性能。

线路故障产生的行波是一种非平稳变化的高频信号,小波变换最大的特点就是具有良好的时频局部化能力,能够从时域和频域描述奇异信号的每一个细节,非常适合非平稳变化的信号分析,因此,小波变换成为分析行波较为有效的数学工具。小波变换可以实现信号的无重叠分解,非常适合暂态行波信号的奇异性检测[6-7]。

4 装置的硬件设计

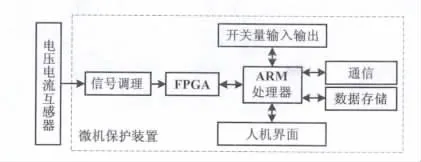

微机保护装置的硬件结构如图2所示。信号经互感器采集后送入微机保护装置内部,硬件结构包含信号调理模块、FPGA信号处理模块以及ARM核心处理器模块3大模块。

图2 装置硬件结构图Fig.2 Hardware structure of device

4.1 信号调理

行波信号的有效提取是实现行波保护的前提,而行波信号能否获取依赖于互感器能否正确地传递高频暂态量。实践表明,电容式电压互感器可以有效传递700 kHz高频信号的幅值信息,电磁式电流互感器可以有效传递500 kHz以下的高频信号的幅值信息。本系统提取1~500 kHz的高频信号,因此可以使用传统互感器对高频信号进行有效提取。

信号调理电路[7]完成信号的电平匹配、信号放大、初级滤波、采样保持以及A/D转换。高频行波分量较工频量小,容易被湮没,初级滤波将信号中的工频信号滤除。

根据采样定理,如果随时间变化的模拟信号最高频率为fmax,采样频率满足fs≥fmax即可恢复原始信号,则A/D采样频率不低于1 MHz,实际中使用的频率约为3~5倍。本次设计共采集6路模拟信号,分别为三相电压、电流。为了简化电路设计,采用两片具有最高6 MHz采样率的高速A/D转换器THS1206。该芯片具有4个模拟通道的12位A/D转换器,可以通过编程对模拟通道进行选择采样或循环采样,并对提取的高频信号进行精确转换。

4.2 FPGA 模块

FPGA具有现场可编程、低功耗、设计灵活、可以实现并行运算等优点,被逐步应用于实时信号处理中。本系统采用ALTERA公司的高性能、低成本Cyclone II系列EP2C20F484C8的FPGA芯片。该芯片内部包含大量的可编程逻辑单元以及独立的硬件乘法器,其丰富的片上资源可完全满足设计要求。

在FPGA处理器内部搭建NIOS II/f软核处理器,控制A/D采样以及各个外设模块,内部设置FIFO缓存,存放运算结果。由于在处理过程中产生大量的中间数据,为实现快速存取,片外扩展SRAM存储器。采用DSP Builder/Simulink开发环境设计db3小波算法模块作为NIOS II处理器自定义外设,采用定制指令模式,即采用一条指令可以实现一次小波运算。采用DSP Builder设计算法模块,可以充分利用Matlab中Simulink系统建模的优势,大大简化了FPGA的设计难度[8-10]。算法模块采用流水线方式设计,并且通过逻辑复制实现多通道并行计算。该模块优于传统DSP处理器,可大大提高小波分析的速度。

4.3 ARM 模块

ARM处理器为系统的控制中心,装置选用S3C2440A(ARM920T系列)芯片作为主处理器。S3C2440最高频率达400 MHz,是低成本、低功耗、高性能处理器,被广泛应用于工业控制领域[9]。

ARM控制器模块包括片外容量为8 MB SDRAM动态存储器,用来存放运行程序、数据,2 MB Flash存储器,用来存放原始程序,磁盘存储器,用来存放历史运行数据。此外,ARM模块还包括JTAG调试模块、复位模块、通信接口模块、人机交互模块以及开关量输入输出模块。

人机交互模块是管理员与微机保护装置进行对话的界面,主要部件为液晶屏、键盘、USB接口。液晶屏显示保护运行状况、系统实时运行状态参量,键盘用来完成对装置的设定。USB接口可以连接打印机或外接通用的USB存储设备,完成对故障信息的打印、拷贝。

通信模块应严格按照变电站自动化通信规约IEC 61850设计,通信接口为RS-232/485接口、以太网接口以及无线通信接口。装置通过以太网与站控中心互联,将保护装置的运行状态以及线路故障信息向控制中心发送,并且接受站控中心与调度中心的指令,实现全站的数据共享以及站控中心或调度中心对装置的遥测、遥信、遥控、遥调(远动功能)。RS-232接口用于对装置的调试,RS-485接口用于对装置进行GPS对时以及远程通信。无线通信模块采用冗余模块设计,防止常规通信线路因自然灾害等损坏而造成保护装置无法远程通信,方便装置的升级。

开关量输入输出模块包括输入与输出两个部分,输入部分负责采集断路器、隔离刀闸的状态信息以及装置特定功能开关的开闭信息;输出部分负责报警信号输出、控制出口继电器,完成保护执行。

4.4 FPGA与ARM模块通信

FPGA与ARM的通信包括实时信号的传输与ARM对FPGA的在线配置两部分。

4.4.1 ARM与FPGA实时数据的通信

FPGA内部时钟与ARM不同步,在本次设计中,ARM与FPGA的接口采用总线存储方式,将FPGA直接连接在ARM芯片的外围总线(advanced peripheral bus,APB)存储总线上,即将FPGA映射成为ARM外设存储器的一部分。ARM处理器通过存储器指令访问FPGA,进行数据、控制信号的传输,并且接受FPGA的中断请求信号。试验表明,这种连接方式方式稳定性较好[10]。

4.4.2 ARM 在线配置 FPGA

ALTERA公司Cyclone II系列FPGA是基于SRAM LUT的配置结构,掉电易失,因此在系统上电时必须重新配置。为了节约成本、简化硬件设计并且方便远程升级,设计中采用ARM处理器在线配置FPGA芯片。

基于ARM在线配置FPGA共有PS(被动串行)、PPS(被动并行同步)、PPA(被动并行异步)、PSA(被动串行异步)和JTAG等5种方式。JTAG接口被广泛应用于芯片测试和配置等过程中。

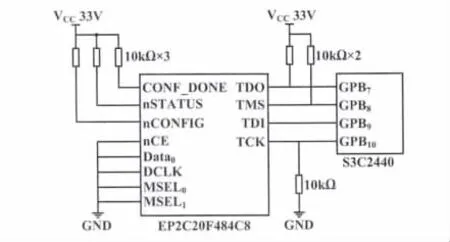

ARM在线配置FPGA电路如图3所示。

图3 ARM在线配置FPGA电路Fig.3 Online configuration circuit from ARM to FPGA

图3中,与 AS、PS配置方式相关的 nCONFIG、MSEL0和MSEL1引脚全部接地,而将nCONFIG引脚置为高电平。Data0和DCLK引脚可以任意配置,现将其全部接地。使用S3C2440A处理器的通用引脚GPB7、GPB8、GPB9、GPB10引脚分别作为 JTAG 接口的TDO、TMS、TDI和 TCK。

5 系统软件设计

本装置软件系统包括FPGA和ARM两大部分。其中,FPGA负责采样控制与信号处理,ARM完成故障判别、保护执行、后台通信、人机交互、事件记录等。

5.1 实时操作系统的引入

保护装置运行时处理任务十分繁杂,包括数据处理、后台通信、人机交互、保护执行、事件记录等,而且都要求实时处理,因此,装置的软件设计是一件十分复杂的工作。

嵌入式实时操作系统(ROTS)的出现,为多任务的实时处理提供了解决方法,使软件开发变得便捷高效。在微机保护中引入实时操作系统,还可以将保护算法的编写与底层的驱动开发分离,大大加快了保护装置的开发速度。本次设计在ARM处理器中嵌入裁剪后的Linux操作系统,不仅可以提高ARM多任务处理的能力,而且简化开发难度,可有效提高ARM处理器多任务执行的效率。

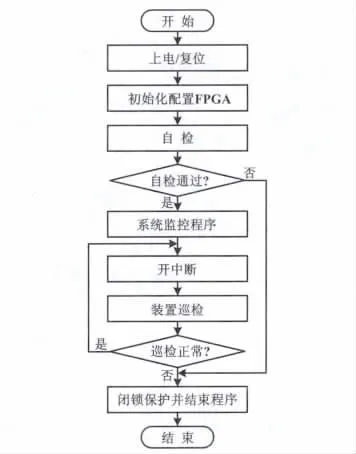

5.2 ARM主程序设计

ARM模块采用标准C语言编程,整个软件分成系统监控、保护子程序、通信管理、人机交互等几个大模块,每个大模块又分成若干个功能子模块。ARM主程序流程如图4所示。

图4 ARM主程序流程图Fig.4 Flowchart of main program in ARM

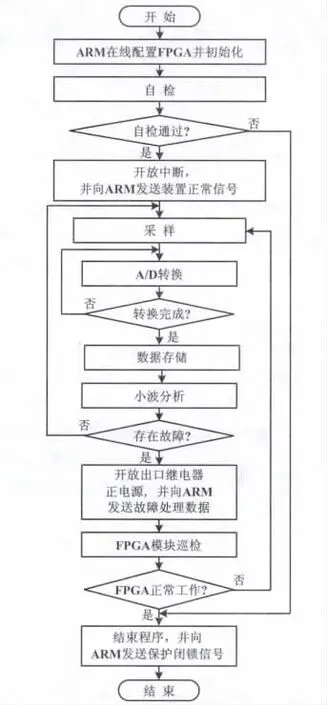

5.3 FPGA模块程序设计

FPGA模块前端连接数据采集部分,后端与ARM处理器相连接,主要完成采样控制、数据预处理功能,其中的NIOS II处理器作为芯片控制核心。FPGA程序流程如图5所示。

图5 FPGA模块流程图Fig.5 Flowchart of FPGA module

6 结束语

本文设计了新型的基于FPGA+ARM双处理器平台的行波保护装置。该装置在FPGA内部采用逻辑电路搭建多通道并行计算的小波分析模块,并且采用NIOS II处理器自定义指令的功能加速数据处理;ARM模块作为控制核心,引入嵌入式实时操作系统实现多任务调度。双核处理器分工明确、各取所长,解决了长久以来行波保护难以实现的问题。FPGA具备现场可编程功能,这不但为以后的升级提供了方便,而且还为目前大量超高压特高压线路实现保护的超高速动作提供了理想的解决方案。

[1]苏斌,董新洲,孙元章.基于小波变换的行波差动保护[J].电力系统自动化,2004,28(18):25 -29.

[2]文智波.FPGA与DSP在小波变换应用中的对比研究[J].仪表技术,2011(5):62 -65.

[3]符玲,何正友,钱清泉.超高压输电线路的故障暂态特征提取及故障类型判断[J].中国电机工程学报,2010,30(22):100 -106.

[4]张保会,郝志国.智能电网继电保护研究的进展(一)——故障甄别新原理[J].电力自动化设备,2010,30(1):1 -6.

[5]邹贵彬,高厚磊.输电线路行波保护原理与研究现状[J].继电器,2007,35(20):1 -6.

[6]葛耀中.新型继电保护和故障测距的原理与技术[M].2版.西安:西安交通大学出版社,2007:190 -197.

[7]张胜祥,张保会,段建东.暂态量保护开发平台的研究[J].继电器,2004,32(15):34 -38.

[8]李杰,王爱民,董利科.基于DSP Builder的电压闪变测量的数字化设计[J].电力系统保护与控制,2010,38(19):190 -194.

[9]舒双宝,罗家融,王勤湧,孙滨璇.基于DSP和ARM便携式电能质量监测系统的设计与实现[J].电力系统保护与控制,2010,38(24):185 -189.

[10]朱晓鹏,肖铁军,赵蕙.ARM+FPGA的实时数据采集系统设计[J].计算机工程与设计,2009,30(13):3088-3090.