基于FPGA的帧同步器的设计与仿真

2013-08-20代延村

李 亚,代延村

(中国空空导弹研究院 河南 洛阳 471009)

在遥测系统中,为了使接收端与发送端保持同步,并实现正确的分路,一般都要在被传送的信息数据流中按一定的周期插入特定的码字作为帧同步信息。在接收端,在码同步建立之后还必须进行帧同步,以确定一帧数据的起始和字同步,实现数据的正确分路。在发送瑞,遥测数据被在采编器中按一定的周期插入特定的码组作为各帧数据段的同步信息,帧同步器就是根据这种特定码组和帧排列结构完成帧定位信息的提取。

帧同步也称为群同步,是在数字通信系统接收端用于正确分路过程。实现帧同步的方法主要有两种[1]:一种方法是在数据信息流中插入一些特殊码组作为每帧的头尾标志,接收端找出这些特殊码组的位置就可实现帧同步,另一种方法是不需要在数据流中插入特殊码组,它类似于载波同步和位同步中的直接法[2],利用数据流统计或者调制特性来实现自同步。目前,插入特殊码组方法的应用范围较广泛。特殊码组也称为帧同步组,它要具有尖锐单峰特性的自相关函数、长度适中和便于与信息流区分等特性[3]。

1 帧同步器原理

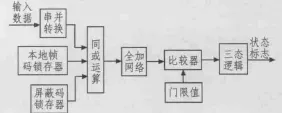

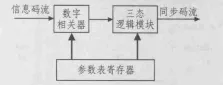

帧同步器是利用帧同步码组的自相关特性和周期性,经过相关运算器从接收到的遥测数据流中识别出来。为了正确可靠地建立帧同步,帧同步器工作在三态逻辑(搜索、校核和锁定),以降低接收信号噪声、误码和伪码的影响。帧同步器的原理框图如图1所示。

由图1可以看出,帧同步器首先对接收数据进行串并转换,与本地同步码组进行同或运算,屏蔽掉无用的相关位,再经过全加网络,实现对相关值相加运算,与判决门限值进行比较,得到同步帧标志,再通过三态逻辑模块来降低噪声和干扰对帧同步器的影响,最终得到帧同步的状态标志。

图1 帧同步器原理框图Fig.1 Schematic diagram of the frame synchronizer

1.1 数字相关器

数字相关器与模拟相关器相比,具有电路简单、调试方便和利于集成等优点,尤其易于微机相结合,便于满足不同同步码组长度的遥测系统的需求,因此应用最为广泛。

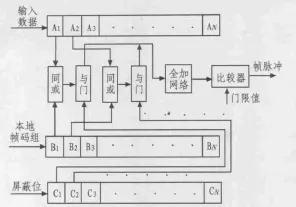

图2 数字相关器原理框图Fig.2 Schematic diagram of digital correlator

图2给出了数字相关器原理框图[4]。数字相关器由串并转换器、本地同步码锁存器、屏蔽位锁存器、同或逻辑、与逻辑、全加网络、门限值锁存器和比较器组成。这里门限值通常与信干噪比(SINR)有关。门限值如果太大,会增加帧同步的可靠性,但是会增大漏同步概率。

1.2 三态逻辑

在遥测系统的帧同步设计时,要尽可能减小虚警和漏检的情况。这就需要进行状态逻辑与帧同步保护控制单元设计,即三态逻辑模块。三态主要是搜索(S)态、校核(C)态和锁定(L)态。S态就是数据流通过数字相关器的过程。在搜索状态时,有两种搜索方法[5]:自寻最大值搜索法和固定门槛搜索法。C态可以提高帧同步正确捕获概率,降低噪声和干扰的影响,同时会降低假同步概率。由于帧结构呈周期性,因而真同步在预定的周期会在固定位置重复出现,而假同步不具有此特性。同样,L态是在锁定状态下降低噪声和干扰的影响以提高帧同步器的强健性。

图3 三态逻辑流程图Fig.3 Flow chart of the tri-state logic

三态逻辑流程如图3所示。其中,α和β分别是校核态和锁定态所能容忍的连续错误帧数。α、β选择直接关系到帧同步的捕获时间与保持时间。校核参数α大真同步概率大,捕获时间长;β小捕获时间短,假同步概率大。保护参数β越大,帧同步维持时间越长,重新返回帧同步捕捉时间也越长:β值小帧同步维持时间短,重新返回帧同步捕捉时间少。因此应合理选择这两个参数。在图3中,FS=0和FS=1分别表示输入数据经过数字相关器后全加网络的输出值小于和不小于门限值。

2 帧同步码组

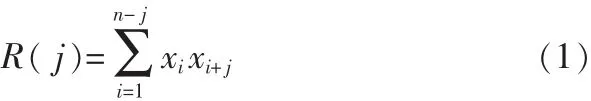

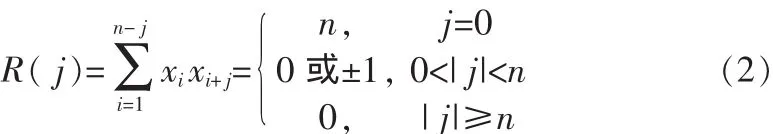

帧同步码组是一种特殊码组,要满足以下特点[1]:具有尖锐的单峰特性的局部自相关函数;便于信息码区别;码长适中。对于一个 n 位长的码组{x1,x2,…,xn},其中 xi∈{+1,-1},局部自相关函数定义为

其中,可用于做帧同步码的码字主要有[5]:Barker码,Reed-Maller码,Legender码,伪随机码和最佳同步码。前4种只有奇数码位长,最后一种奇偶都存在。前4种码中,除了Barker码外,错位数不为零时,都存在不同程度的旁瓣。

Barker码是一种有限长的非周期序列,它的局部自相关函数满足

Barker码的补码、镜像码和镜像补码与正码一样都具有良好的自相关特性。当n=11时,Barker码的正码、补码、镜像码和镜像补码分别为 (+1,+1,+1,-1,-1,-1,+1,-1,-1,+1,-1)、(-1,-1,-1,+1,+1,+1,-1,+1,+1,-1,+1)、(-1,+1,-1,-1,+1,-1,-1,-1,+1,+1,+1)和(+1,-1,+1,+1,-1,+1,+1,+1,-1,-1,-1)。它们的局部自相关函数如图4所示。

图4 位Baker码局部自相关函数Fig.4 Local autocorrelation function of Baker code with a length of 11 bits

Reed-Maller码,Legender码和伪随机码都是由数学理论推导出来的。伪随机序列主要具有以下3点性质:

1)伪随机序列每一周期中的0和1的个数接近相等;

2)把伪随机序列每一周期中连续出现0或1的子序列称为游程。每一周期中连续的0或1的个数称为游程长度。伪随机序列每一周期中长度为1的游程约占游程总数的1/2,长度为2的游程约占游程总数的1/22,以此类推。即每一周期内,长度为n的游程出现的次数约是长度为n+1的游程出现的次数的两倍。且在同样长度的游程中,0游程数和1游程数大致相等。

3)伪随机序列的自相关函数类似于白噪声自相关函数的性质。

伪随机序列具有类似随机序列的性质,它的结构或形式是可以预先确定的,并且可以重复地产生和复制。二元m序列是一种伪随机序列,它具有优良的自相关函数,且易于产生和复制,在扩展频谱技术中得到广泛的应用。在实际工程应用中,m序列既可以用硬件产生,也可以用软件产生,然后存在存储器中通过相应的时钟输出。图5给出了用线性码序列发生器产生m序列原理框图[3]。

图5 线性反馈移位寄存器Fig.5 Linear feedback shift register

图5中共有n个移位寄存器,每一级寄存器的状态用ai表示,ai=0或1。反馈线的连接状态ci用表示,ci=1表示此线接通(参加反馈运算),ci=0表示此线断开,此级移位寄存器状态不参加反馈运算。n级移位寄存器除去全0输出状态外,能产生的序列的最大可能周期为p=2n-1。由于m序列是同样级数的线性移位寄存器所产生的最大长度序列,因此,它的效率是最高的。

最佳同步码是采用计算机优选出来的,美国国家航空航天局(NASA)优选出的常用几种最佳同步码如表1所示。

对于一个遥测系统,系统的有效性和可靠性是相互矛盾的。帧同步码位数的选取也是需要折中考虑的。帧同步码位数越短,在帧同步码组位置上检出假同步的概率就越大。反之,假同步的概率就越小。但是,由于信道中总是存在噪声和干扰,帧同步码位数越长产生误码的可能性就越大,同步码的捕获时间也会越长,同时信道利用率越低。通常,对一般长度的数据帧,帧同步码长度占帧总长的5%~10%是较理想的选择。对于遥测数据帧很长,帧同步码最长不超过64位。

表1 常用最佳同步码表Tab.1 Table of commonly optimal synchronization code

3 FPGA实现

为了提高帧同步器的通用性,这里将帧同步器设计成参数可变的,它的输入参数如下:

①输入码速率:100 bps~30 Mbps;

②字长:4~16 bits;

③帧长:4~8 192 字/帧;

④帧同步码长:4~32 bits;

⑤帧同步码组:选取合适的码组;

⑥帧同步码字位置:帧头(1)或帧尾(0);

⑦S态帧同步码容错数:0~15 bits(与数字比较器的门限值对应关系);

⑧C态帧同步码容错数(α):0~7 bits

⑨L态帧同步码容错数(β):0~7 bits

帧同步器的Verilog[6]程序实现原理框图如图6所示。

图6 帧同步器FPGA实现原理框图Fig.6 Realization block diagram of frame synchronizer using FPGA

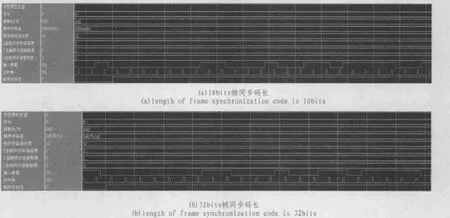

4 仿真结果

图7 10 Mbps码率帧同步器仿真结果图Fig.7 Simulation figure of frame synchronizer with 10 Mbps bit rate

图7给出帧同步器的仿真结果。PCM遥测系统仿真条件是:NRZ-L 码;码率:10 Mb/s;字长:8 bits;帧长:160 字/帧;帧同步码长:16 bits,32 bits;帧同步码组:EB90(十六进制)[5],0D67FC1D(十六进制);帧同步码字位置:帧头(1);S态帧同步码容错数:1 bit,3 bits;C 态帧同步容错帧数(α):2帧;L态帧同步容错帧数 (β):3帧。仿真软件是:modelsim SE6.5版本。

由图7可以看出,帧同步器具有可实现性。同时,这种帧同步器可以根据不同的输入来满足不同遥测系统的需求,具有较高的灵活性。

5 结束语

基于FPGA所设计的帧同步器具有一定的抗噪声和干扰能力,其可靠性比传统的未采用三态逻辑模块的帧同步器高。另外,它可以适应不同用户的需求,具有较强的灵活性。这将大大降低开发成本。

[1]樊昌信,张甫翊,徐炳祥,等.通信原理[M].5版.北京:国防大学出版社,2006.

[2]季仲梅,杨洪生,王大鸣,等.通信中的同步技术及应用[M].北京:清华大学出版社,2008.

[3]曾一凡,李晖.扩频通信原理[M].北京:机械工业出版社,2005.

[4]张军,姚远,张其善.高速可编程PCM遥测帧同步器[J].北京航空航天大学学报,1994,20(1):25-30.

ZHANG Jun,YAO Yuan,ZHANG Qi-shan.A high-rate programmable pcm telemtry frame synchronizer[J].Journal of Beijing University of Aeronautics and Astronautics,1994,20(1):25-30.

[5]姜昌,范晓玲.航天通信跟踪技术导论[M].北京:北京工业大学出版社,2003.

[6]周润景,苏良碧.基于Quartus II的数字系统Verilog HDL设计实例详解[M].北京:电子工业出版社,2010.