一种高电源抑制比的CMOS带隙基准电压源设计

2013-08-20白忠臣秦水介

程 刚,白忠臣,王 超,秦水介

(贵州大学 贵州省光电子技术与应用重点实验室,贵州 贵阳 550025)

基准电压源的设计是模拟集成电路设计中的核心内容,基准电压源有很多的实现方式,比如:齐纳基准电压源、E/D NMOS基准电压源、XFET基准源和带隙基准源。随着集成电路的发展,带隙基准的电压源是用得最广泛且非常成功的一种电路结构,带隙基准电压源由于其输出电压与电源电压,工艺参数和温度的关系很小,且结构简单,在A/D,D/A等集成电路设计中,高性能的带隙基准电压源的设计十分关键。目前,工程上常采用高阶补偿和运用共源共栅技术,来提升电路的温度系数和PSRR[1-2]。

文中设计了一种采用共源共栅电流镜和负反馈技术的低温度系数,高电源抑制比的带隙基准电压源。其在-40~100℃的温度变化范围内,有很好的温度系数。在低频,PSRR达到了100 dB。

1 电路设计

1.1 带隙基准原理

为了得到与温度无关的电压源,其基本思路是将具有负温度系数的电压与具有正温度系数的电压相加,他们的结果就能够去除温度的影响,实现接近零温度系数的工作电压。

如图1,2个双极性晶体管工作在不同的工作电流时,基极—发射极电压差ΔVBE正比于绝对温度。取:

图1 基准电压源核心电路Fig.1 Core circuit of the bandgap reference source

式中,热电压VT有正的温度系数大约为0.086 mV/K,有负的温度系数为-2 mV/K,N为Q2、Q1发射极面积之比[3]。Vref=VBE+kVT,可见,可以通过调节电阻值的比例可以得到一个合适的k,来获得一个理论上与温度无 关的基准电压。基准电压的近似值是半导体硅的带隙电压,所以称之为带隙基准[4]。

1.2 具体实现电路

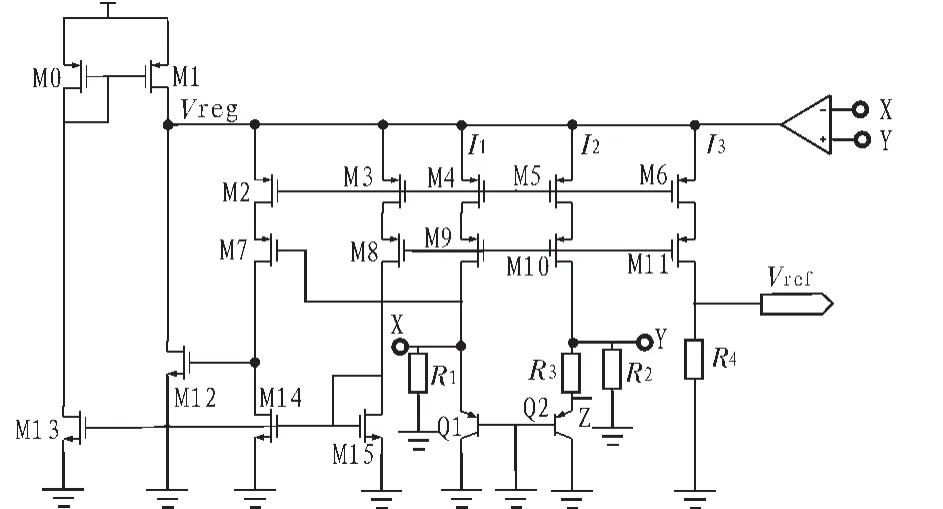

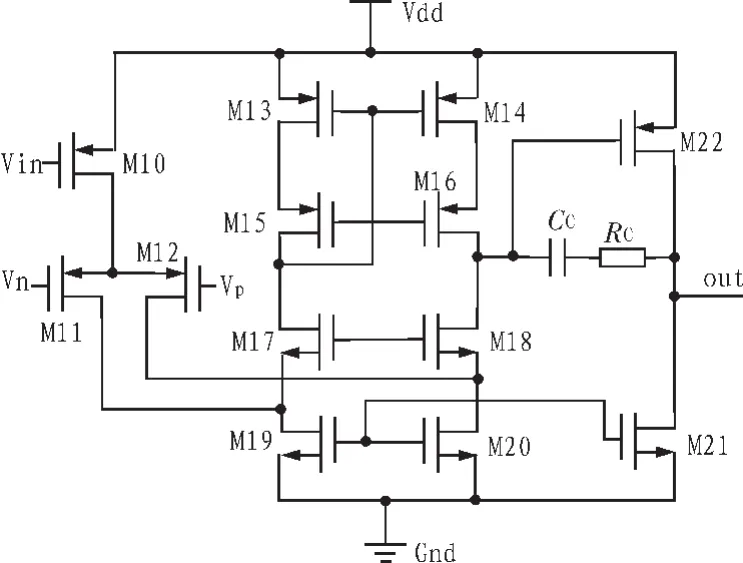

基于上述原理,本文利用CMOS工艺设计的带隙基准整体电路如图2所示,包括带隙基准核心电路,PSRR增强电路,误差放大器等等。

1.3 基准源核心电路

为了得到较低的基准电压,本设计采用banba结构的带隙基准核心电路,输出的基准电压大约为650 mV。带隙基准核心电路主要由PTAT产生电路和基准电压输出部分组成,由图 2:PTAT电流经由 M4,M5,M9,M10组成的共源共栅电流镜复制到基准电压输出端,再由R4分压可得一个输出电压,通过调节R4与R3的比例关系,来调节输出电压大小,通过调节R3与R2的比例系数来调节基准电压的温度系数。具体分析如图2。

图2 高PSRR带隙基准主体电路Fig.2 High PSRR bandgap reference main circuit

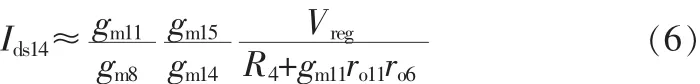

当 PMOS 共源共栅管 M9~M4,M10~M5,M11~M6 有相同的尺寸时,分别通过它们的电流I1=I2=I3=I,同时有

由于放大器的作用:

1.4 PSRR增强电路

本文采用电压预调制技术负反馈降低等效小信号电阻的方法来提高整个带隙基准源的PSRR,通过小信号分析,本设计中带隙基准的PSRR可以看作是电源电压在基准源输出端的小信号分压,为了获得较高的PSRR应该提高输出节点到输入电压节点的小信号电阻,降低输出节点到地的小信号电阻,降低输出节点到地的小信号电阻有两种方法,一种是增加并联支路数,另一种是增加单支路的电流,即先对电压采样,然后放大并转化为电流,再注入采样电压,这样电压线上就叠加了许多小信号电流,从而可以大大减小小信号电阻。本文采用第二种方法,具体分析,如图所示。

其中,M0,M1,M13.M12,M2,M7,M14,M3,M8,M15 构成电压预调制模块,其中:

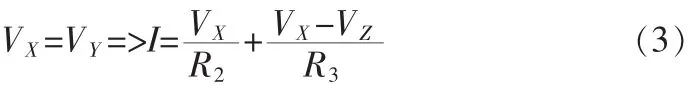

其中Zo1为F点输出阻抗,Ids14可表示为:

ro3为 M6 输出阻抗, 一般有 Ids7>>Ids11,Vreg>>VA则 M12 将VF转化为小信号电流。

从而,我们可以得到Vreg点的等效输出阻抗。

可见,通过引入负反馈的预调制技术,大大降低了运放输出端到地的小信号输出阻抗。同时通过对带隙核心电路使用共源共栅电流镜增加到Vreg输出端的小信号电阻,使得整体电路的PSRR进一步增加。

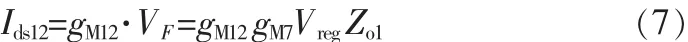

1.5 高增益运算放大器设计

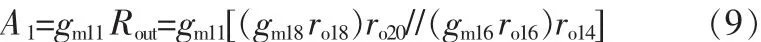

为了使基准源X,Y两点尽可能被钳位在同一个电压值,要求放大器工作在深度负反馈,并且需要放大器有尽可能大的开环增益,同时由于高增益的放大器有助于提升整体电路的电源抑制比,本设计采用折叠—共源共栅放大器如图3 所示[5-6]。

图3 折叠共源共栅放大器Fig.3 The folded cascade operational amplifier circuit

第一级为折叠共源共栅跨导放大器,第二级为共源级放大器,由于PMOS输入的折叠运放的规模输入范围可以轻松摆到地,而PNP管VBE值大约为650 mV,除此之外PMOS输入可以很好地降低噪声输入。整个电路的增益为:

其中第一级增益为:

第二级增益为:

米勒电容Cc和调零电阻Rc可以很好的保证电路工作在稳定状态。除此之外,版图设计中应该尽量考虑运放的输入对管的匹配,从而尽可能减小失配带来的失调电压对电路性能的影响。

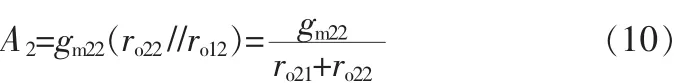

2 电路仿真与讨论

基于CSMC0.5 μm工艺参数,用Spectre软件对电路进行模拟,图4所示分别是带隙基准的电源抑制比曲线和温度特性曲线,可见在低频段电路有很高的电源抑制比,在1 kHz的频率,电路的电源抑制比达到了100 dB,较传统结构的带隙基准电路高出30 dB。温度特性曲线可知,在环境温度从-40~100℃变化时,输出电压变化仅为1.7 mV,经计算,基准的温度系数为℃。图5自上而下所示分别为基准电压Vref在30℃,60℃,90℃条件下随VDD变化的波动,在3~5 V电压变化的范围内,ΔVref在不同的温度条件下,变化值均小于2 mV可见,本设计有很好的电压线性度和温度特性。

图4 带隙基准的电源抑制比与温度特性Fig.4 PSRR characteristics and temperature curve of the proposed circuit

图5 电压变化特性曲线Fig.5 Characteristic curve of voltage variations

3 结 论

本文通过对带隙基准基本原理的分析,基于CSMC0.5 μm工艺设计的高电源抑制比带隙基准电路,在工作电压2.5~5 V的范围内,有很好的线性度,利用负反馈环路技术,在1.25×10-5℃的温度系数下,得到了高于100 dB的电源抑制比。本文带隙基准电路可以应用于高电源抑制比的LDO电路中,输出电压低,也十分适合为低压电路供电。

[1]Brokaw P A.A simple three terminal IC bandgap reference[J].IEEE J Sol Sta Circ,1974,9(6):388-393.

[2]Hoon S K,Chen J,MALOBERTIF.An improved bandgap reference with high power supply rejection [C]//ISCAS.A rizona ,USA,2002:833-836.

[3]毕查德,拉扎维.模拟CMOS集成电路设计[M].西安:西安电子科技大学出版社,2002.

[4]Gray P R,Meyer R G.Analysis and design of analog intergrated circuits[M].New York:Jone Wily&Sons,2001.

[5]Hironori B.A CMOS bandgap reference circuit with sub-1-V operation[J].IEEE J.Soild-Circuits,1999,34(5):670-673.

[6]张彬,冯全源.一种高电源抑制比带隙基准源[J].微电子学,2010,40(1):58-61.

ZHANG Bin,FENG Quan-yuan.A high PSRR bandgap reference source[J].Microelectronics,2010,40(1):58-61.