新型高线性度双平衡CMOS混频器芯片的设计*

2013-08-19赵明剑李斌吴朝晖

赵明剑 李斌 吴朝晖

(华南理工大学 电子与信息学院,广东 广州 510640)

混频器或乘法器是无线通信系统中必不可少的组成部分,依赖它得以实现系统中信号基带、中频与射频之间的相互转换,或完成某种调制与解调、相乘与平方功能[1].对于高性能的无线通信电子线路而言,除了需要混频器提供信号频谱线性搬移或信号相乘等基本功能外,其线性度是最受关注的性能,体现为电路的1 dB 压缩(IP1dB)与三阶交调(IIP3)指标.

目前,混频器结构可以分为无源混频和有源混频两大类.虽然无源混频在线性度性能上存在一定优势[2],但由于混频器处于射频系统的前两级,因此不提供信号增益的无源混频器[3],容易造成无线通信系统信噪比(SNR)的劣化[4].在有源混频器中,双平衡混频器比单平衡混频器在线性度上存在明显优势[5].传统的双平衡混频器的核心单元为基于吉尔伯特相乘跨导环[5-11],但这类吉尔伯特相乘环输出的电流信号中会包含一个与输入电压信号相关的2 次非理想项,只有当输入信号强度足够弱时,该非理想项才可近似忽略,从而完成信号与本振的相乘与混频.虽然此2 次项也可以通过在吉尔伯特相乘环基础上加入若干电流源来抵消[12],或者在输入端加入衰减器[13],但这些措施增加了电路实现的复杂度,因此,此类混频器电路的线性度性能不容易提高.

文中设计了一个用于无线通信射频系统的新型高线性度双平衡混频器.该混频器基于新型全差分乘法器结构,混频器的核心部分为两个工作在线性区的对称金属氧化物半导体(MOS)晶体管,射频信号由该晶体对管的源、漏两极输入,本振信号由晶体对管的栅极输入.该混频器结构简单,且输出信号中不存在与射频信号相关的2 次非理想项,从而以低复杂度和高线性度的方式实现了射频信号与本振信号的混频.另外,由于该混频器基于乘法器结构及原理,因此该电路也可实现对两种差分射频信号的相乘.为改善芯片与片外电路之间的隔离度,提高输出中频(IF)信号的功率强度与输出匹配性能,设计了由差分推挽放大器及源级跟随器构成的芯片输出缓冲接口电路.

1 理论设计

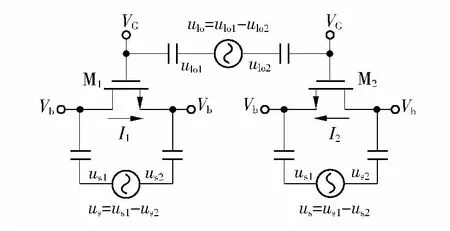

通常利用器件本身的非线性特性或时变特性可以完成对信号的混频或相乘操作.图1 是利用一对工作在线性区的N 沟道金属氧化物半导体(NMOS)晶体管来完成双平衡混频或相乘的原理示意图,其中us(us=us1-us2)是加在晶体管M1和M2源、漏两极的差分射频信号,ulo(ulo=ulo1-ulo2)是加在M1和M2栅极的差分本振信号,I1和I2是M1和M2的输出电流,Vb是加在M1和M2的源、漏两极的偏置电压,VG是加在M1和M2栅极的偏置电压.

图1 基于工作在线性区的金属氧化物半导体对管的双平衡混频原理Fig.1 Double-balanced mixing principle based on a pair of metal-oxide semiconductor transistors in linear region

工作于线性区的MOS 晶体管的漏源电流IDS可以由下式表达:

式中:Vgs为晶体管栅、源极电压差;VT为晶体管的阈值电压;Vds为晶体管漏源电压;βn为晶体管的跨导参数W/L 为晶体管的宽长比;μn为沟道表面载流子迁移率;Cox为栅氧化物单位面积电容.

图1 中MOS 晶体管M1的Vgs和Vds可分别由式(2)和(3)表示:

将式(2)、(3)代入式(1),可得晶体管M1输出电流I1的表达式:

根据上述原理推导,同样也可以得到晶体管M2输出电流I2的表达式:

由式(4)、(5)的第2 项可知,工作于线性区的晶体管M1、M2的输出电流信号中,均已经各自实现了射频差分信号us与单端本振信号ulo1、ulo2的单平衡相乘,但在其输出的电流信号中还各自保留了一个与射频输入信号相关的1 次线性量βnus(VG-Vb-VT).

为此只要在具体电路实现上,将M1、M2的输出电流作差,如式(6)所示,即可最终实现射频信号与本振信号的理想双平衡混频或相乘.

2 电路实现

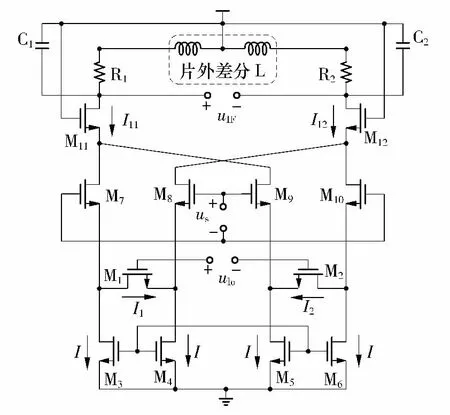

根据上述理论,设计了新型双平衡混频器的核心电路,如图2、3 所示.该混频器基于新型乘法器结构,其中晶体管M1和M2工作于线性区(对应于图1 中所示晶体管M1和M2),晶体管M3至M18均工作于饱和区.整个电路分为两级,第1 级为混频级,第2 级为输出级,从而实现对混频级输出的中频信号的缓冲放大及阻抗匹配.射频、本振输入端均采用T 型电感电容(LC)网络实现输入匹配.下面分别对这两级电路进行介绍.

图2 双平衡混频器的混频级核心电路Fig.2 Mixing-stage core circuit of double-balanced mixer

图3 双平衡混频器的输出级核心电路Fig.3 Output-stage core circuit of double-balanced mixer

2.1 新型双平衡混频器的混频级

如图2 所示,晶体管M1至M12,电阻R1、R2,电容C1、C2,芯片外差分电感L 构成了混频器的混频级核心电路.M1至M10为该级电路的核心混频单元,其中M7至M10主要呈现源随特性,进一步提高了电路中不同频率信号之间的隔离度.此外通过专门设计M7至M10的宽长比,使最终加载到工作于线性区的晶体管M1、M2各自的源、漏两级的射频信号为kus(k 为信号us的电压传递衰减系数);M3至M6为该级电路的尾电流源管,为其各自所在的电流通路提供一个恒定的静态电流I;M11、M12为高阻负载对管,可进一步提高电路的隔离度与电压增益性能,再结合R1、R2、C1、C2及片外差分电感L 构成的RCL 选频滤波负载网络,将核心混频单元混频后输出的中频差分电流(I11、I12)转化为中频(IF)差分电压信号uIF,并完成对该中频信号uIF的选频与滤波,这样整个新型双平衡混频操作完成.

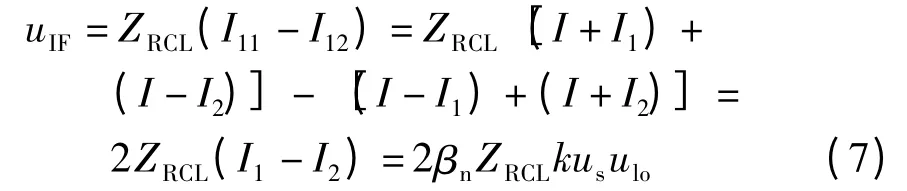

结合式(6),最终该双平衡混频电路输出的中频信号uIF可近似由式(7)表达,

其中ZRCL是由晶体管M11、M12漏端节点看进去的输出等效阻抗.由此可见,该电路完成了对输入的差分射频信号us与差分本振信号ulo的相乘,实现了双平衡混频.且混频输出的中频信号uIF中不包含与us、ulo相关的多次非理想项.此外,通过调节衰减系数k,可进一步改善该电路的输入线性度.

2.2 新型双平衡混频器的输出级

输出级的核心电路如图3 所示.其中晶体管M13-M17,电容C3、C4构成了一个差分推挽放大器,M13为该差分推挽放大器提供恒定的静态电流,通过合理设计M13的宽长比及其栅极偏置电压,可以保证该放大器在提供足够增益的同时产生尽可能小的功率损耗;C3、C4为隔直电容,保证M14-M17获得稳定的栅极偏置电压,同时保证图2 所示混频级电路输出的中频信号uIF可以无损地耦合到M14-M17的栅极;M14、M15与M16、M17构成的互补推挽对的特点是具有很宽的带宽(-3 dB),并且有很高的输出摆幅.因此,这类放大器很适合用于对线性度及速度有高要求的混频或乘法电路的输出缓冲与放大.

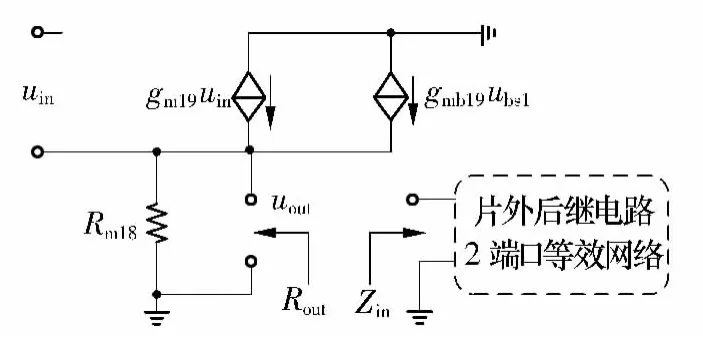

晶体管M18至M21构成了对称的两对源极跟随器,C1、C2是对该电路输出差分信号uout的进一步低通滤波.图4 是图3 中M18、M19构成的源随器的小信号等效图.Rm18是M18的等效阻抗,M19可以等效为两个受控电流源并联,gm19、gmb19分别是晶体管M19的栅跨导和衬源之间的等效跨导,uin是该电路输入小信号,ubs1是M19的衬源偏压.可见,该源随器的输入阻抗近似为无穷大,通过源随器可以实现与前级电路的良好级连;该源随器输出阻抗很低,通过调节M18、M19的宽长比,使等式(8)成立:

电路的输出阻抗Rout与片外后继电路2 端口等效网络的输入阻抗Zin近似相等,即可方便地实现与片外后继电路之间的阻抗匹配.虽然源随器的电压增益近似为1,但源随器可以通过增大输出电流,提高信号功率,增强电路输出驱动能力.

图4 源随器小信号等效图Fig.4 Simplified small signal model in source follower

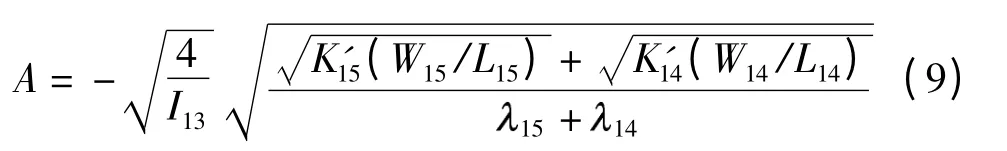

另外,通过电容C5、C6可以完成对既定频率的源随器输出信号进行一阶低通滤波,进一步提高了电路的信噪比质量.该输出级电路提供的总电压增益A 为:

式中,I13为尾电流管M13的输出电流,W15/L15与W14/L14为M14、M15的宽长比,K'15、15与K'14、14分别为M14、M15的跨导参数与沟道调制系数.

3 实验及测试

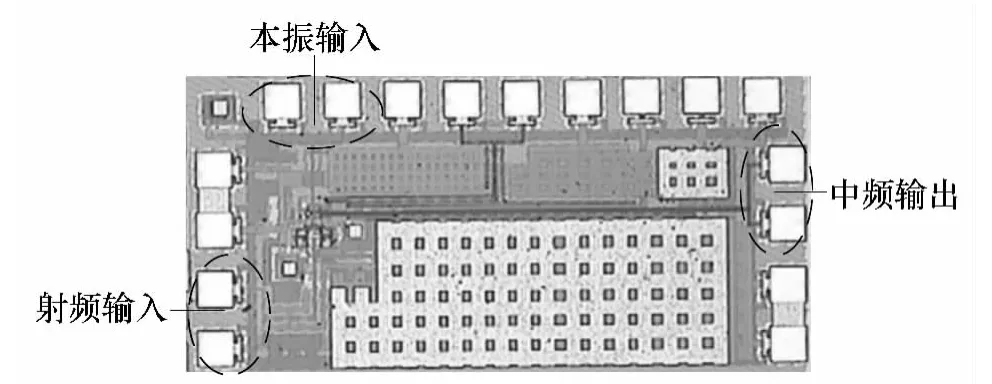

文中基于0.18 μm RF CMOS 标准工艺,实现了新型高线性度双平衡混频器芯片的流片验证,图5是芯片的实物显微照片,片内没有集成电感.芯片总面积为0.5 mm2,芯片满足超宽频带范围内的信号混频与相乘.

图5 设计的双平衡混频器芯片实物显微照片Fig.5 Microscope photograph of the designed doublebalanced mixer chip

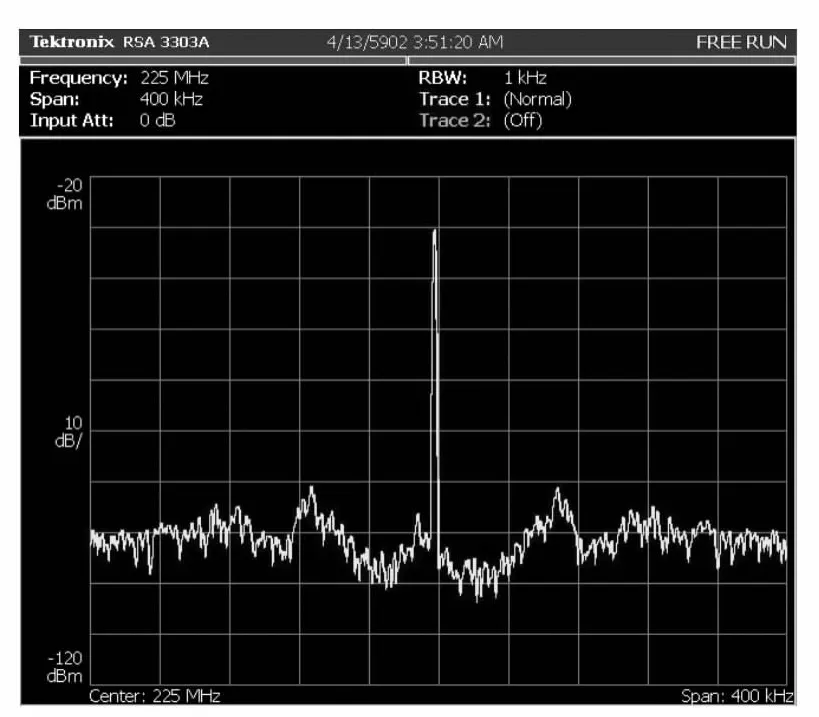

参照DCS-1800 移动电话—混频通信标准,该芯片测试选用的输入射频频率、本振频率以及输出中频频率的测试值,分别设计为1.825 GHz、1.6 GHz 和225 MHz.

图6 为采用泰克RSA3303A 频谱仪监测到的芯片混频输出的中频信号的频谱.此时混频器芯片射频输入信号为频率1.825 GHz、功率-40 dBm 的正弦信号,本振输入信号为频率1.6 GHz、功率-10 dBm的正弦信号;为了对频谱仪进行功率保护,在频谱仪与混频器芯片之间连接了一个衰减器.测试频谱图反映出混频器芯片输出了频率为225 MHz 的稳定纯净中频信号.

图6 双平衡混频器芯片输出的中频信号频谱Fig.6 Output intermediate frequency signal spectrum of the designed mixer chip

在固定射频频率的前提下,测试不同输入功率的射频信号所对应的芯片输出中频信号的功率强度,基于实测结果采用描点法统计并结合Matlab 软件绘制出了所设计的混频器芯片的1dB 压缩点和三阶交调测试曲线,如图7 所示.结果表明,混频器芯片1 dB 压缩点为2.9 dBm,三阶交调点为16 dBm.

图7 1 dB 压缩点及三阶交调曲线Fig.7 Curves of 1 dB compression point and third-order intermodulation

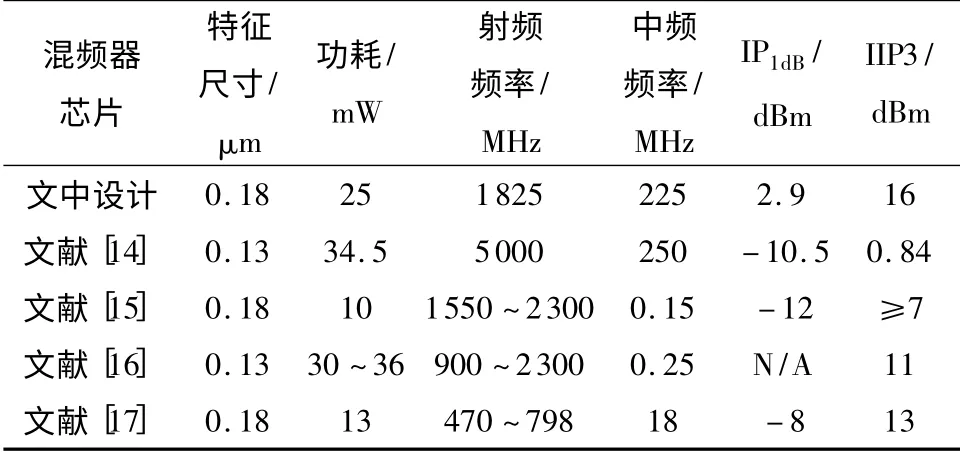

表1 示出了对所设计的混频器芯片和参考文献中列举的混频器芯片性能的对比情况.可以看出,文中所设计的混频器芯片在反映线性度的1dB 压缩点、三阶交调指标上有较大的提高.

表1 文中所设计的混频器芯片与参考文献列举的对比Table 1 Comparisons between the designed mixer chip and the reported ones

4 结语

文中采用0.18 μm RF CMOS 工艺,完成了一款用于无线通信射频系统的高线性度双平衡混频器芯片的设计与流片.该设计采用一种新型的全差分相乘结构,实现了高线性度、低复杂度的双平衡混频或相乘的功能.该设计输出级的高速全差分推挽放大器与源随器,可为混频提供功率增益补偿,并实现与片外电路之间高隔离度的阻抗匹配性能.该混频器还可用于对超高频信号的相乘.芯片功耗25 mV,具有2.9 dBm 的1 dB 压缩点、16 dBm 的三阶交调性能,满足了高速的宽带无线通信射频系统对高线性度指标的苛刻要求.

[1]王光义,丘水生,马在光.相干DCSK 混沌通信系统的多用户噪声性能[J].华南理工大学学报:自然科学版,2003,31(12):1-4.Wang Guang-yi,Qiu Shui-sheng,Ma Zai-guang.Noisy multiuser performance of coherent DCSK chaos communication systems[J].Journal of South China University of Technology:Natural Science Edition,2003,31(12):1-4.

[2]Mirzaei A,Darabi H,Leete J C,et al.Analysis and optimization of current-driven passive mixers in narrowband direct-conversion receivers [J].IEEE Journal of Solid-State Circuits,2009,44(10):2678-2688.

[3]Lont M,Milosevic D,Baltus P G M,et al.Analytical passive mixer power gain models[C]∥IEEE International Symposium on Circuits and Systems (ISCAS 2010).Paris:IEEE Circuits and Systems Society,2010:2386-2389.

[4]Theodore S Rappaport.Wireless communications:principles and practice[M].2nd ed.Upper Saddle River:Prentice Hall,2002:565-568.

[5]Lee T H.The design of CMOS radio-frequency integrated circuits[M].2nd ed.Cambridge:Cambridge University Press,2004:404-437.

[6]Lu Tai You,Chen Wei Zen.A 3 10 GHz,14 bands CMOS frequency synthesizer with spurs reduction for MB-OFDM UWB system [C]∥IEEE International Solid-State Circuits Conference (ISSCC 2008).Digest of Technical Papers.San Francisco:IEEE Solid-state Circuits Society/University of Pennsylvania,2008:126-601.

[7]Seo Jeong Bae,Kim Jong Ha,Sun Hyuk,et al.A low-power and high-gain mixer for UWB systems[J].IEEE Microwave and Wireless Components Letters,2008,18(12):803-805.

[8]Sulivan P J,Xavier B A,Ku W H.Low voltage performance of a microwave CMOS Gilbert cell mixer[J].IEEE Journal of Solid-State Circuits,1997,32(7):1151-1155.

[9]Tang C C,Lu W S,Van L D,et al.A 2.4-GHz CMOS down-conversion doubly balanced mixer with low supply voltage[C]∥IEEE International Symposium on Circuits and Systems (ISCAS 2001).Sydney:IEEE Circuits and Systems Society,2001:794-797.

[10]武振宇,马成炎,叶甜春,等.一种适用于低中频和零中频GPS 接收机的CMOS 混频器[J].微电子学,2010,40(4):481-484,490.Wu Zhen-yu,Ma Cheng-yan,Ye Tian-chun,et al.A CMOS mixer for low IF and zero IF GPS receiver[J].Microelectronics,2010,40(4):481-484,490.

[11]庄海孝,马成炎,叶甜春,等.一种应用于GPS 射频前端的低噪声混频器[J].微电子学,2009,39(2):146-149,154.Zhuang Hai-xiao,Ma Cheng-yan,Ye Tian-chun,et al.A low-noise mixer for GPS receiver[J].Microelectronics,2009,39(2):146-149,154.

[12]邵牟舟,秦世才,贾香鸾.MOS 模拟平方器的应用研究[J].半导体杂志,1994,19(4):18-22,27.Shao Mou-zhou,Qin Shi-cai,Jia Xiang-luan.Research on MOS analog squarer [J].Semiconductor Magazine,1994,19(4):18-22,27.

[13]戴瀚斌,张玉明,张义门,等.一种宽输入范围CMOS模拟乘法器的优化设计[J].现代电子技术,2008,31(1):140-143.Dai Han-bin,Zhang Yu-ming,Zhang Yi-men,et al.Optimized design of a CMOS analog multiplier with wide input range[J].Modern Electric Technique,2008,31(1):140-143.

[14]Ho S S K,Saavedra C E.A CMOS broadband low-noise mixer with noise cancellation[J].IEEE Transactions on Microwave Theory and Techniques,2010,58(5):1126-1132.

[15]Kim N,Aparin V,Larson L E.A resistively degenerated wideband passive mixer with low noise figure and high IIP2[J].IEEE Transactions on Microwave Theory and Techniques,2010,58(4):820-830.

[16]Poobuapheun N,Chen W-H,Boos Z,et al.A 1.5 V 0.7–2.5-GHz CMOS quadrature demodulator for multiband direct-conversion receivers [J].IEEE Journal of Solid-State Circuits,2007,42(8):1669-1677.

[17]Pan Z L,Jiang P C,Zhang L,et al.Low flicker noise and high linearity passive mixer in 0.18μm CMOS for direct conversion receiver[C]∥IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics & Electronics.Shanghai:IEEE Circuits and Systems Society,2009:21-24.