采用MonoDFT测频的单比特接收机性能分析

2013-08-13段国文

段国文

(海军装备部装备采购中心,北京100071)

随着电磁环境的日益复杂,电子战装备对电子战接收机提出了更高的要求,理想的电子战接收机包括瞬时覆盖宽的频域、高灵敏度、大动态范围、高截获概率、同时多信号探测能力强、频率测量准确且处理全实时,但是满足这些要求的理想接收机并不存在,现实过程往往是采用多种接收机类型结合的方式来兼顾各种技术指标。

单比特接收机最早由美国空军实验室AFRL[1]提出,随后一些公司开发了各种类型的单比特接收机。作为一种数字接收机类型,单比特接收机可以实现大的瞬时频率覆盖,处理实时,且体积小,灵敏度高,但是不具备同时多信号能力。这些特点都与模拟IFM接收机相似,可以作为一种新的宽带频率测量方法应用于电子战领域[2-3]。

本文首先介绍了单比特接收机的组成和单比特采样的特点,然后通过Matlab仿真的方法分析了采用MonoDFT方法测频的单比特接收机在灵敏度、相位测量等指标上与标准DFT的差异,最后通过FPGA工具分析了采用MonoDFT处理的单比特处理算法的资源消耗和处理延迟时间。

1 单比特接收机的组成

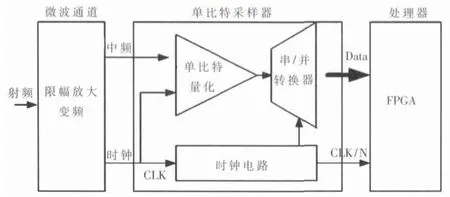

单比特接收机基本组成如图1所示。

从图1可以看到,单比特接收机主要由微波通道、单比特采样器和FPGA处理器组成。微波通道完成射频信号的放大变频,单比特采样器完成中频信号的1 bit量化,得到结果送到FPGA中进行数字处理,完成参数测量。

图1 单比特采样和接收的基本组成结构

单比特采样器是实现单比特接收机的物理基础,决定了整个单比特接收机的基本性能。其数学表达式为:

单比特采样具有以下几个方面的特点:

(1)单比特采样过程中存在大压小的现象;

(2)信号的幅度信息基本消失;

(3)只有1和0,较易实现实时处理;

(4)量化位数只有1 bit,较易实现高带宽、高速率采样。

单比特采样的速率和射频带宽基本决定了单比特接收机的瞬时带宽[4]。总的来说,单比特接收机具有采样率高(数十亿赫兹)、带宽大的特点,这对后续在FPGA中完成参数测量带来了较大的处理压力。

2 MonoDFT测频方法的性能分析

在单比特接收机中,对高速1 bit数据的处理算法主要包括相关法测频、计数法测频、频域DFT测频等方法,采用频域DFT处理方法与其他处理方法相比具有灵敏度高等优势,因此单比特接收机一般都采用DFT处理的方法完成频率测量。

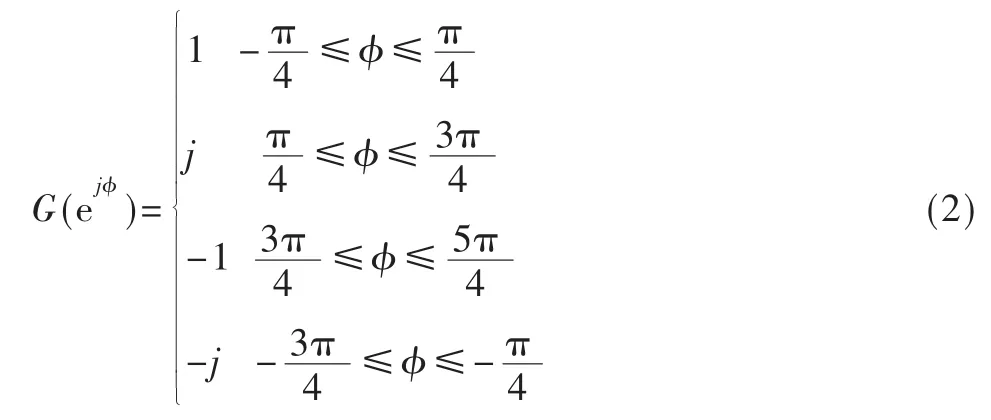

DFT处理与其他处理方法相比,具有计算密度高、处理消耗资源大等特点,对高达数十亿赫兹的高速单比特采样来说,处理压力较大。由于是单比特,其动态范围有限,因此可以在DFT运算中对傅里叶变换的旋转因子 G(ejφ)=e-j2πkn/N进行简化[2,5-6],简化原则如式(2)所示。

从式(2)可以看到,经过简化后,在进行DFT计算过程中只有加法和减法运算,对DFT算法的FPGA实现具有重要意义,这种简化旋转因子的处理思想称之为MonoDFT处理算法。

由于采用了简化运算,与标准DFT相比,必然会存在一定的差异,针对灵敏度、频率、相位测量等问题利用Matlab进行了仿真分析。

图2是在假设10 GS/s单比特采样,不同输入频率条件下,采用标准DFT和MonoDFT各自得到的峰值幅度,其中虚线表示MonoDFT的峰值,从图中可以看到MonoDFT的峰值幅度比标准DFT低0.5~1 dB左右。

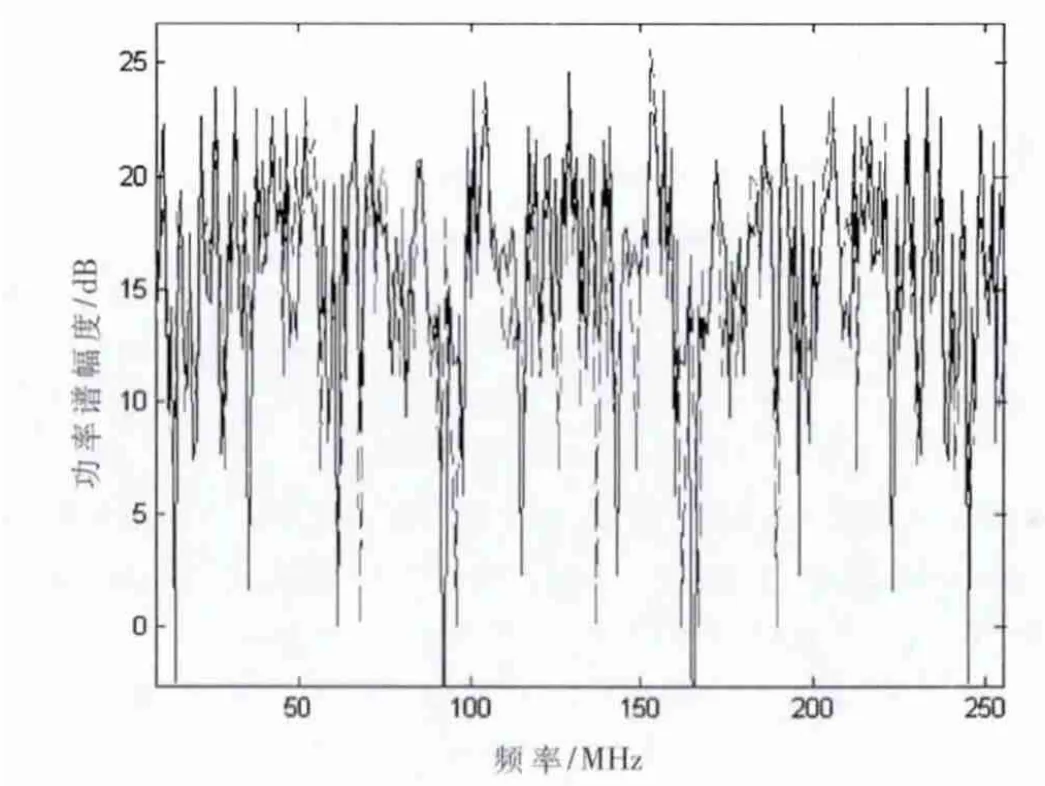

假设如果没有信号输入,只有噪声,可以得到256点DFT和MonoDFT的功率谱,如图3所示,其中虚线部分是MonoDFT的计算结果。从图中可见,噪声情况下MonoDFT和DFT结果相比功率谱幅度基本保持一致。

从上面分析可见,采用了MonoDFT测频方法的单比特接收机,在进行信号检测过程中,与采用标准DFT相比会损失约1 dB。

图2 标准256点DFT和MonoDFT(虚线)在不同频率点幅度响应比较图

图3 标准256点DFT和MonoDFT(虚线)在输入白噪声情况下最大幅度比较图

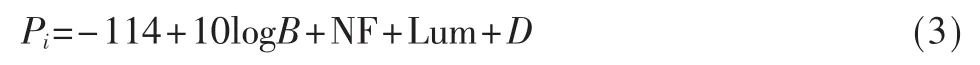

按照数字接收机灵敏度常用计算公式[1]:

其中:Lum是失配损耗,从图2中可以看到,其值为 3 dB;D为检测系数,一般按14 dB计算;NF为通道噪声系数,取6 dB;B为处理带宽,单位MHz,D为数字处理积累时间t的倒数;假设按照单比特采样率为10 GS/s计算,对256点MonoDFT运算的处理每帧的积累时间为25 ns。

另外考虑到MonoDFT会损失1 dB,微波通道的幅频不平坦度±2 dB,通过式(3)计算后可以得到,在 10 GS/s采样情况下,256点MonoDFT测频方法的灵敏度约为-70 dBm。

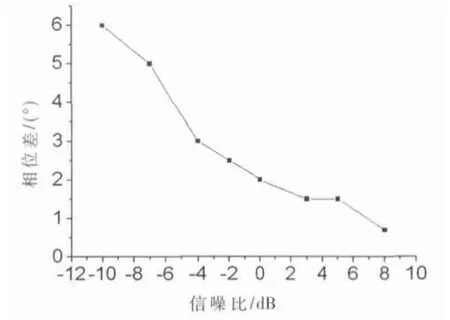

一般利用DFT测频过程中,希望可以获得相位信息,可用于精测频、比相等。采用标准DFT和MonoDFT方法测量的相位值之差,在不同信噪比条件下的结果如图4所示。从图中可以看到,采用MonoDFT方法,随着信噪比的降低,二者之间的测量误差会增大,但总的来说误差值较小。

图4 标准DFT和MonoDFT测量相位差值

从上面的分析可以看到,采用MonoDFT方法可以有效地测量信号的频率和相位信息,其具体性能与标准DFT相当。

3 FPGA实现

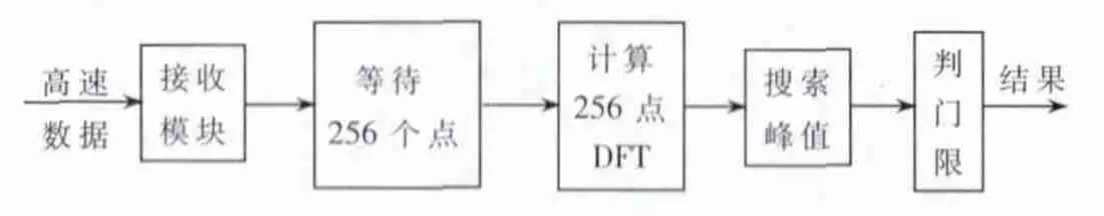

利用FPGA如何实现MonoDFT是单比特数字接收机的关键,假设对于10 GS/s采样的高速单比特数据,其FPGA处理采用如图5所示的处理框图[3]。

图5 FPGA处理算法框图

图中接收模块主要是和外部串并转换器配合,将10 GS/s高速单比特数据流转换为156 MHz速率,64 bit宽的数据,便于后续FPGA进行进一步的处理;

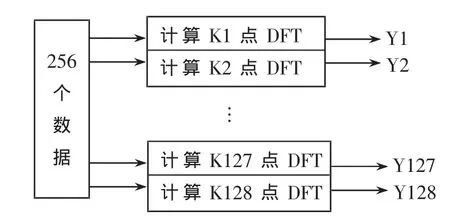

在计算256点MonoDFT过程中,采用分帧处理的方式实现,每帧时间 25 ns,在每计算一个 256点 DFT之前首先收集满256个数据,然后再按照图6所示的MonoDFT实现方法计算k=1~128的DFT结果。

图6 MonoDFT实现框图

利用VHDL语言实现了图4中的处理算法,并在ISE工具中进行了布局布线,利用一片XC5VSX95T芯片实现单比特处理算法所需要的资源如表1所示。

从表1中可以看到,利用256点MonoDFT完成测频的单比特处理算法,需要消耗一片SC5VSX95T大约31%的逻辑资源,其他方面的资源则消耗较少。

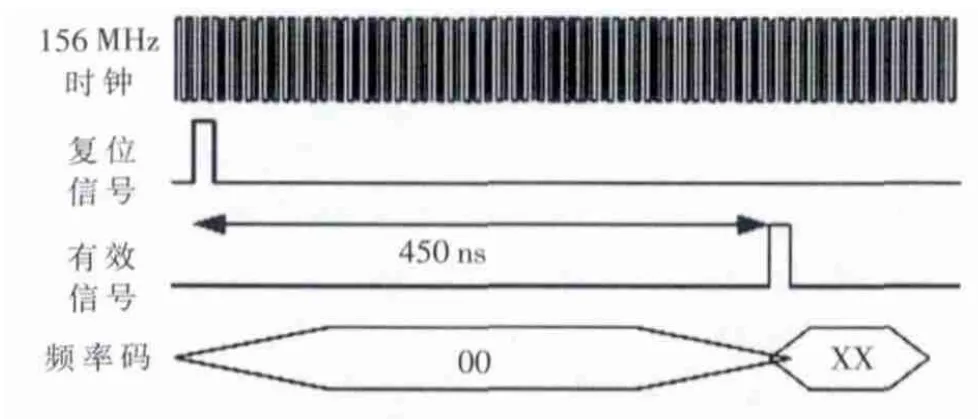

在完成算法同时利用ModelSim仿真工具对图4中的处理延迟进行分析,得到结果如图7所示。从图7中可以看到,采用256点MonoDFT方法实现频率测量,延迟时间约为450 ns。

表1 完成单比特处理算法的FPGA资源消耗表

图7 利用ModelSim得到的仿真结果

4 总结与展望

从上面的分析可以看到,采用MonoDFT方法实现单比特的频率测量,可以获得与标准DFT测频方法相近的性能,而在FPGA实现过程中则主要消耗逻辑资源,与标准DFT相比消耗资源大大降低。

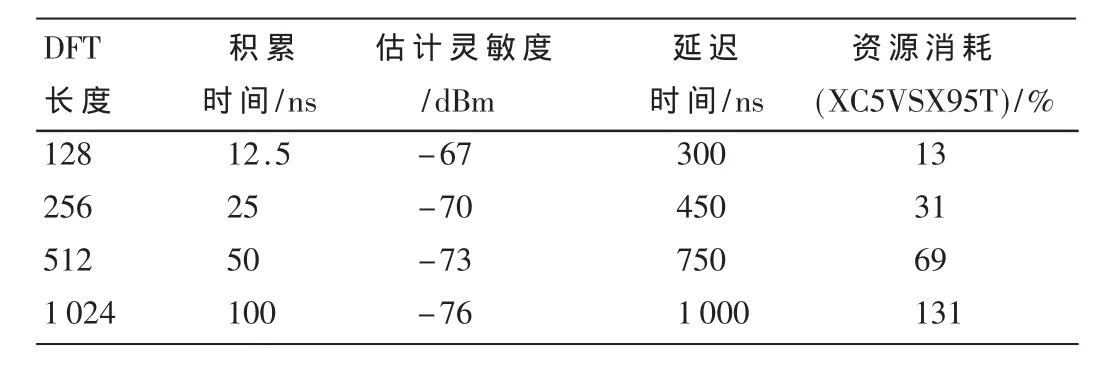

如果采用不同长度的积累时间,则在灵敏度、处理延迟时间、资源消耗等方面得到不同的结果,采用本文中同样的分析方式,在不同长度MonoDFT具体性能如表2所示。

表2 采样率10GS/s下不同MonoDFT点数的性能

从表2可以看到,灵敏度、处理延迟时间是相互制约的,频率分辨率是积累时间的倒数;如果要求处理延迟时间小,则会降低灵敏度,减小积累时间,降低频率分辨率。在实际具体应用过程中,需要根据不同的应用场合要求,综合各方面因素选择合适长度的MonoDFT算法。

单比特数字接收机采用单比特MonoDFT的处理方法,以较小的体积和处理资源,可以获得较大的瞬时覆盖带宽、较高的灵敏度和较快的处理延迟时间,且具备数字处理的灵活性,能够在一个单片FPGA中就可以实现全部的数字处理功能。作为一种宽带接收机,同模拟IFM相比具有灵敏度高的优势,同时多信号环境下不会测量错误等多方面优势,目前世界上一些电子战公司都将单比特接收机作为未来宽带接收机的一种解决方案,相信在不久的将来,随着国内高速单比特采样、处理架构等方面技术的成熟,单比特接收机将应用到电子战的各个领域中去。

[1]JAMES T.宽带数字化接收机[M].杨小牛,陆安南,等译.北京:电子工业出版社,2002.

[2]丁锋,董晖,姜秋喜.基于单比特接收机的低截获概率信号检测技术[J].现代防御技术,2007,35(5):110-114.

[3]GRAJAL J,BLAZQUEZ J,LPPEZ R,et al.Analysis and characterization of a monobit receiver for electronic warfare[J].IEEE Trans on Aerospace and Electronic Systems,2003,39(1):244-258.

[4]周涛.量化精度对数字化接收机性能的影响[J].电子信息对抗技术,2006,21(6):20-23.

[5]吕远,唐斌,祝俊.一种基于高阶近似核DFT的快速实现算法[J].电子信息对抗技术,2009,24(2):19-22.

[6]张硕,梁士龙.单比特测频接收机中DFT算法的优化[J].制导与引信,2006,27(2):51-55.