DDR2信号完整性分析与应用

2013-08-12吴业舟李晓春

吴业舟 李晓春

(1.飞利浦中国投资有限公司,上海 200233;2.上海交通大学 电子工程系,上海 200240)

DDR2 高速内存已经成为嵌入式系统中的主流应用,信号完整性设计也是在应用DDR2 内存必须要考虑的问题。文献[1]对155MHz DDR 总线进行了信号完整性仿真,重点分析了几种串联电阻位置对数据传输信号的影响。文献[2]利用Ansoft SIWave 对DSP 的DDR2 进行了仿真,对线间串扰进行了研究,对数据信号进行了仿真分析。本文借助Mentor Graphics 公司的HyperLynx 仿真工具,对DDR2 时钟进行仿真,对产品实测结果进行对比分析,对将来设计给出思路。

1 信号完整性概述

信号完整性主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,对可靠性的影响。对大多数电子系统而言,当时钟频率超过100MHz 或者上升下降边沿速率小于1ns 时,高频信号在线上传输时,由于电磁效应,会引起信号传输的畸变,这时就需要关注信号完整性问题[3]。

1.1 传输线特性

传输线的两个重要参数是传播延时和特性阻抗。传输线上电场和磁场建立的快慢决定了信号的速度。电磁波的相速度[5]:

其中,表示自由空间的介电常数,其值为F/m,表示材料的相对介电常数。表示自由空间的磁导率,其值为H/m。表示材料的相对磁导率,一般都为1。在空气中,相对介电常数为1。在大部分材料中,相对介电常数总是大于1,例如FR4 基材的相对介电常数大约为4.3。时延Time delay 与传输线长度关系:

Len 表示传输线长度,V 表示信号的速度。由此公式计算,在FR4 材料中,传输线的时延约为6.692ns/m。传输线的另一个特性参数即为特征阻抗,在工程计算中,常用近似算式来快速计算传输线的特性阻抗。对于微带线,通用近似式为:

对于带状线,通用近似式为:

其中,为特性阻抗,表示介电常数,h 表示信号线与平面间的介质厚度,w 表示线宽,b 表示平面间距离,t 表示金属厚度。在工程中,一般将PCB 上的传输线的阻抗设定在50Ω。由经验值可得,FR4 基材的PCB 板上50Ω 微带线的线宽等于介质厚度的两倍。50Ω 的带状线,其2 个参考平面间的总介质厚度等于线宽的两倍。

1.2 反射

反射是指信号在传输线上的回波,只要信号遇到瞬态阻抗发生突变,反射就会产生。信号沿传输线传播时,无论什么原因使瞬态阻抗发生了变化,部分信号都将沿着与源传播方向相反的方向反射,而另一部分将继续传播,但幅度有所改变[4]。通常使用端接来抑制反射,通用的端接方式有四种,源端串联端接,远端并联端接,远端戴维南端接和远端RC 端接。

2 系统叠层设计

如图1 所示,本项目PCB 层数为12 层。12 层包括4 个信号层,2 个电源层,4 个地层和2 个元件层。其中,顶层和底层是元件层,第2、5、8、11 层是地层。第2、11 层的地层与第3、10层的电源层相组合,2 个地层作为屏蔽层包裹在PCB 的外层,减少EMC 问题,并且,电源层和地层相互贴近,层间距为0.0762mm,通过层间电磁耦合,为电源提供嵌入式电容,为抑制电源的高频噪声提供一些帮助。4 个信号层围绕中间2 个地层成对出现,这样既可以避免信号在跃层的时候切换参考平面,也可以尽量减少信号电流的回流面积,对一些信号完整性问题,例如串扰,反射,以及EMC 问题有改善作用。PCB 的信号层目标阻抗为50Ω10%,板厚为1.5mm。

图1 叠层示意图

利用公式(3)和(4)对每一层的传输线特性阻抗进行计算,其中,第1 和12 层为微带线,其余层都为带状线。按PCB制造商提供的资料,所使用的玻璃纤维基材的介电常数为4.3,依照PCB 制造商的工艺能力,线宽加工的最小单位是0.0254mm,具体计算结果见表1:

表1 叠层阻抗计算

3 DDR2 差分仿真

3.1 前仿真

前仿真是指在布线前进行仿真,仿真过程不包括PCB 的物理信息。可以对布线的拓扑结构、端接方式、线长间距等进行一定的约束。DDR2 总线的时钟信号是差分信号对,符合SSTL_18 规范,由内存控制器对DDR2 内存进行驱动。所有的地址信号和控制信号都是在CLK 上升沿和CLKN 下降沿的交叉点进行采样的。所以,时钟信号的信号完整性决定了DDR系统的稳定性。

本系统由两片16bit 数据位宽的DDR2 内存组合构成32bit 位宽,所以时钟信号需要同时驱动两片内存,这样就存在两个接收端,不再是单点网络。多个接收端的布线,一般有两种形式,一种是菊花链结构,一种是星型结构。菊花链结构是指信号按顺序结构走向每一个接收端。星型结构是指信号由驱动器出发后,在多个接收器之间取一个中心位置,在中心位置分开多路,走向每一个接收器。菊花链结构一般会带来两种问题。其一,由于一个接收端处于传输线的中间位置,末端产生的反射信号会对中间位置的接收端产生作用,会造成信号震荡。其二,由于两个接收端到驱动端的距离并不相等,较远的接收端收到的信号会被引入更多的时延。两片内存接收到的时钟时间并不一致,在速率较高的同步接收系统中,这会造成时序问题。所以,一般在同步系统中,采用星型结构。

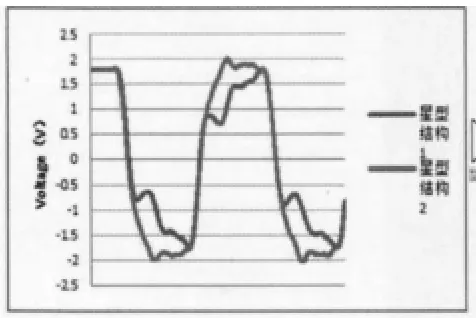

图2 为两种星型结构拓扑图,从驱动端到两个接收端的传输线长度相等,约为50.8mm。由于到两个接收端的长度都相等,所以两个接收器接收到的时钟信号之间不会有时延。左侧图表示了分叉点接近接收端的结构,右侧表示了分叉点接近驱动端的结构。由图3 可见,星型结构1 的接收端波形在边沿上有反射引起的波形畸变,波形畸变的幅度较大,可能会引起时钟的误触发,这是由于两条特性阻抗50Ω 的传输线并联引起了阻抗失配而造成了反射。星型结构2 的接收端波形上也有反射,但是反射较小,幅度为250mV,信号也没有发生明显的畸变。一个大致的经验法则:如果桩线(分叉后的传输线)长度小于信号上升边的空间延伸的20%,其影响可以忽略。相反,如果其长度大于信号上升边的空间延伸的20%,则对信号质量就会有很大的影响[3]。

图2 星型结构拓扑结构

图3 星型结构接收端波形仿真结果

DDR2 时钟的上升沿时间为500ps,而传输线的时延为6.692ns/m,通过计算得,分叉线的最大长度应尽量控制在14.93mm 以内:

其中:Lstub 表示分叉线长度。星型结构2 的分叉线长度为12.7mm,小于14.93mm,所以,它的仿真结果中反射幅度很小。

星型结构2 中,反射信号可以通过源端串联端接来进行抑制。源端串联端接功率消耗较其他三种并联端接方式要小,且高速电路的PCB 面积一般都很有限,串联端接PCB 占用面积很少,适合作为星型拓扑结构的端接。反射系数的公式[3]为:

其中,为反射系数,Z1和Z2分别为阻抗变换点前端和后端的传输线阻抗。当Z1=Z2时,反射系数为0。通过IBIS 模型数据可知内存控制器的输出阻抗为36Ω,所以,使用14Ω 的串接电阻,可以使输出阻抗达到50Ω,与后端50Ω 的传输线特性阻抗相匹配。

由仿真结果图4 可知,加入14Ω 串接匹配电阻后,时钟信号上的上冲和下冲得到了有效的抑制。

图4 DDR2 差分时钟串联端接仿真结果

3.2 后仿真

后仿真是指在布线完成后进行仿真,可以提取PCB 上各种参数模型,对电路进行精确分析。依照前仿真的结果,DDR2 时钟布线采用了星型结构,分叉点位置原理驱动端,并且在靠近驱动端的位置加入了串联匹配电阻。

图5 为DDR2 差分时钟布线图,差分时钟信号从右侧驱动端出发,经过了一对串联端接电阻后,在第四层按100Ω 差分线形式进行布线,至两片内存中间位置,通过1 对过孔,跃层至第六层,依然按100Ω 差分线形式走向两个接收端。从源端出发到两个接收端的长度都相等,约为55.88mm。

Hyperlynx 可以将PCB 传输线模型,驱动器和过孔模型提取出来单独进行仿真,模型包含了传输线的叠层信息和过孔模型。如图6 所示,将前后仿真的结果进行对比,后仿真所得的波形边沿变化速率慢于前仿真,主要原因是由于在布线过程中引入了过孔,过孔的等效模型十分复杂,由对地电容和串联电感组成,会导致信号边沿减缓。并且,过孔也会引入信号传播的时延,所以在图6 中,后仿真波形时延大于前仿真波形。

图5 DDR2 差分时钟布线

图6 前仿真与后仿真对比

4 DDR2 时钟信号实测

为了验证信号完整性仿真结果,必须以实际的测量结果为依据。由测量结果图7 可见,时钟信号上升沿和下降沿光滑,无反射引起的震荡干扰,在边沿结束的位置,也无高频振铃信号产生,避免了EMI 辐射。实测的波形与仿真结果相比,边沿略有不同,说明仿真的模形,包括器件,传输线和过孔,相比于实际情况还有误差。在表2 中,将仿真数据与实测数据以及JEDEC8-15A 规范进行了对比,仿真数据与实测数据接近,并且,测量结果完全满足JEDEC8-15A 规范要求。

图7 DDR2 时钟信号测量结果

5 结论

本文利用Hyperlynx 仿真软件和IBIS 模型对DDR2 时钟信号进行了仿真,依据优化结果进行PCB 布线。经过PCB 加工,使用示波器对信号实测验证,以及EMC 测试等其他验证,DDR2 系统都能够稳定,可靠地工作。

[1]邬利芳,侯永刚.基于仿真的信号完整性设计与分析[J].信息通信.2012(05):49-50

[2]曹亚良,张福洪.TMS32OC6455 的DDR2 电路的信号完整性设计[J].杭州电子科技大学学报.2012.05-043

[3]Eric.Bogatin 著,李玉山,李丽平等译.信号完整性分析.北京:电子工业出版社,2010

[4]杨洪军.信号完整性分析及其在高速PCB 设计中的应用.学位论文.电子科技大学.2006