新型8管一位全加器电路设计

2013-08-02董艳燕

董艳燕,韦 一,陈 君

(中国计量学院 光学与电子科技学院,浙江 杭州 310018)

全加器是实现算术逻辑运算集成电路的重要基础,也常常是限制系统面积、速度和功耗的主要单元之一,所以全加器的优化对整个系统性能的提高有着非常重要的作用.纵观全加器研究发现,与行为级、版图级设计相比,基于晶体管电路级的优化对全加器性能的提高有着非常大的影响.由于全加器晶体管数目对降低硅面积、提高速度和降低功耗方面起着重要作用,因而如何减少晶体管数目是全加器电路非常重要的研究内容[1].从已发表的文献可看出,早期的全加器晶体管数目较多,如40管互补全加器[1]、28管资源复用全加器[2]和24管镜像复用全加器[3],近年来由于新型同或门/异或门的出现以及传输门的采用,简化了全加器的电路结构,大大减少了晶体管数目,典型的如20管CMOS传输门全加器(TGA)[4]、16管传输函数全加器(TFA)[5]、14管全加器电路[6],以及10管全加器[7-8]和8管全加器[9-10].

我们通过对已有一位全加器电路的研究与分析,提出了一种新型的全加器单元,电路仅需要8个晶体管,由2个3管同或门模块和一个2管选择器模块组成.在TSMC 0.18μm CMOS工艺器件参数下经HSPICE模拟表明,与现有典型的全加器相比,新设计具有更低的功耗和更小的功耗延迟积.

1 已有的全加器电路

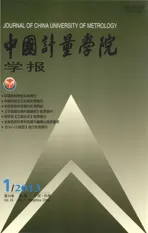

图1是5种典型全加器电路结构,其中图1(a)是28管资源复用CMOS全加器[2],图1(b)是10管SERF全加器[7],图1(c)是10管9A 全加器[8],图1(d)是10管13A全加器[8],图1(e)是8管 CLRCR 全加器[9].

静态CMOS全加器典型代表是图1(a)的28管资源复用CMOS全加器[2],该电路利用全加器的逻辑对称性和资源复用技术大大降低了文献[1]中的40管互补全加器的晶体管数目,并降低了功耗.文献[4]提出了基于CMOS传输门和CMOS反相器结构的全加器(TGA),该电路将晶体管数目降低到了20个,但由于引入了多个反相器,电路的功耗和延迟较大.文献[5]提出的传输函数全加器(TFA),由于减少了TGA电路的反相器个数,将晶体管数目进一步减少到了16个,且保持了输出电平质量高的优点同时也降低了功耗.文献[6]提出的14管全加器电路进一步降低了晶体管数目且优化了全加器的功耗性能.文献[7]提出的SERF电路如图(b)将晶体管个数降低到了10个.文献[8]中提出了基于不同组合XOR/XNOR门电路的41种10管全加器,但大部分电路都有阈值损耗,其中9A全加器如图1(c)和13A全加器如图1(d)具有较好的性能.为了解决传输门全加器的阈值损失的问题,文献[9]通过变换全加器布尔函数提出了8管CLRCR全加器,如图1(e),电路采用反相器输出来恢复阈值损失,输出电平质量较好,但电路还需要额外增加一个用于生成互补进位输入信号的反相器,因而晶体管数目增加了2个,同时也增加了功耗.

图1 典型全加器电路结构Figure 1 Typical full adder circuits

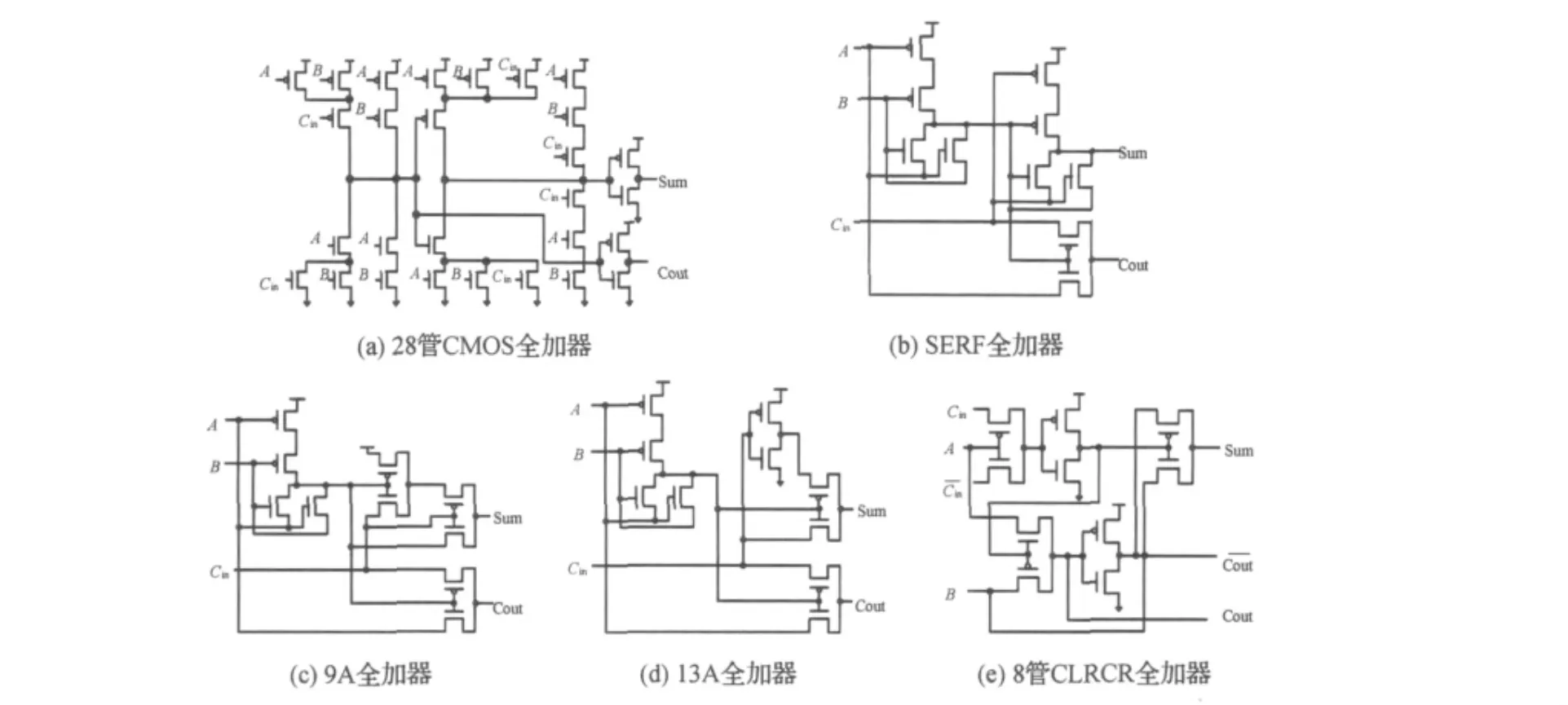

为了解决CLRCL电路存在需要互补进位信号的问题,CHOWDHURY在文献[10]提出了基于新型3管异或门结构的8管全加器,如图2,但是通过研究发现,在某些输入组合逻辑状态下,全加器输出端的值是不确定的.如在输入AB信号都为低电平时,传输门 M7和 M8都截止,此时Cout的值是不确定的.

图2 基于3管XOR结构的8管全加器结构Figure 2 Previous 8Tfull adder design based on 3TXOR gate

2 新型8管全加器电路

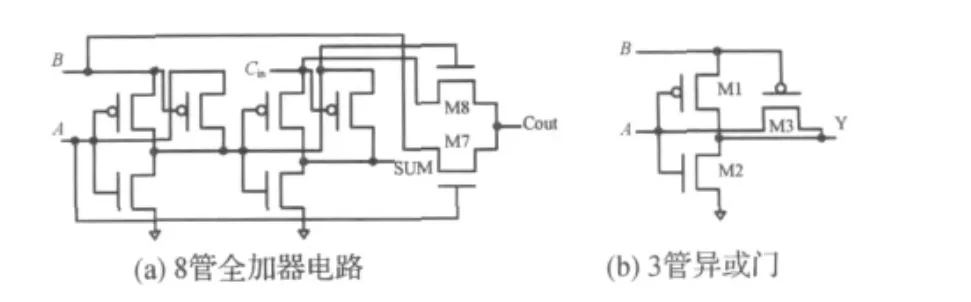

全加器的布尔函数关系可如式(1)(2)表示:

式(1)和(2)中,A 和B 是一位输入信号,Cin是相邻低位来的进位,SUM是求和信号,Cout是进位信号,“⊕”是异或符号.

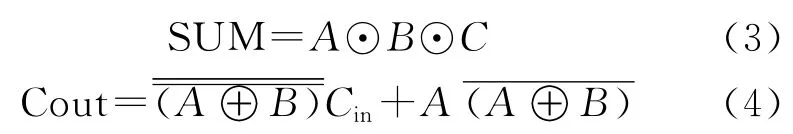

文中,将上面两个式子变换为

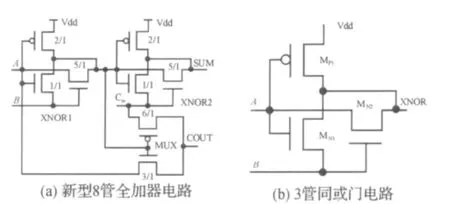

式(3)和(4)中的“⊙”是同或符号.根据式(3)和(4)我们提出新设计如图3.其中图3(a)是新型8管全加器电路,图3(b)是3管同或门电路,从图中看出新全加器电路结构分成三部分.

图3 新电路

1)A ⊕B(或A⊙B)是求和信号SUM的中间信号,也是进位信号Cout的控制信号.A⊕B信号是图3(b)同或门模块生成的.该模块由PMOS管 MP1、NMOS管 MN1和 MN2组成.其中MP1管和 MN1管构成改进型反相器,MN2管是NMOS传输门,当信号B为低电平时输出端实现AB,当B为高电平时,反相器截止,传输门导通,同或门输出逻辑值AB.这两者输出信号直接并联在一起实现A⊕B信号.

2)求和信号SUM是由两级同或门即XNOR1和XNOR2生成的.第一级同或门的输出是第二级同或门的输入信号.

3)2选1数据选择电路MUX是用来生成进位信号Cout,A⊕B信号控制的PMOS传输门和NMOS传输门可以直接并联在一起实现“或”的功能.

新提出的全加器包括两个3管同或门模块和一个选择器模块,需要8个晶体管,适当增加同或门晶体管MN2宽度可以降低同或门输出端的阈值损失并降低亚阈值功耗[10],从而提高全加器的性能.在TSMC 180nm CMOS工艺下经优化后各晶体管的宽/长已经在图3中标出.

3 性能比较

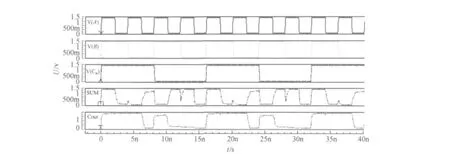

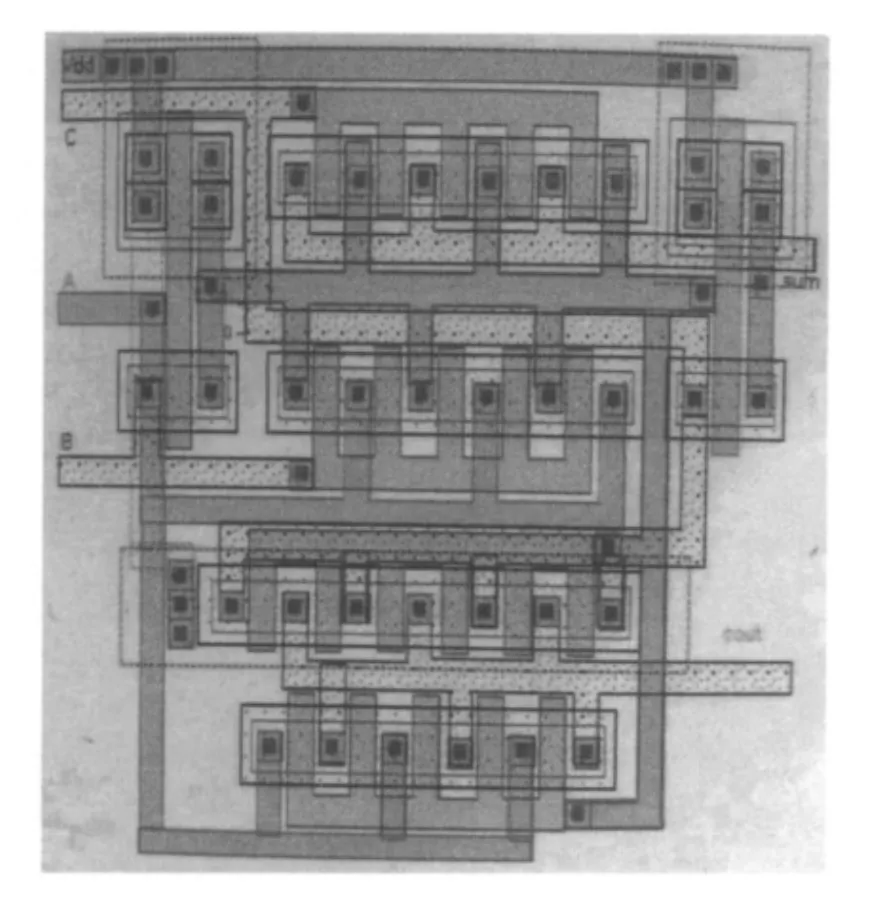

对新设计和图1中提到的5种全加器单元在输入信号频率100~500MHz下进行了HSPICE模拟,各个电路均在TSMC的180nm CMOS工艺下优化,并在1.8V电压下进行功能模拟和性能测试.图4是频率为250MHz时新电路的模拟波形,其中,横坐标表示时间,纵坐标表示电压,从波形可看出,逻辑功能正确.图5是在TSMC 180nm CMOS工艺下的版图照片.

图4 频率为250MHz时新电路的模拟波形Figure 4 Waveforms of the novel circuit under a frequency of 250MHz

图5 新电路的版图照片Figure 5 Layout photo of new circuit

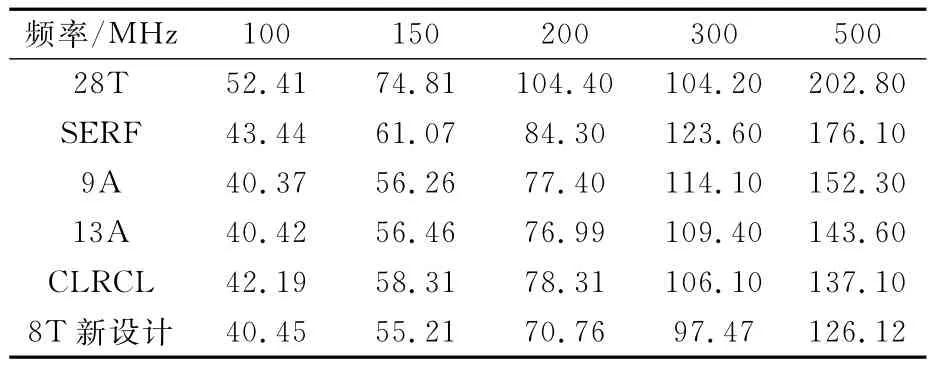

测试的内容包括平均功耗和不同负载下的延迟时间.其中功耗指的是随机产生的大量输入信号组合模式下电路的平均功耗[8],表1是负载电容为100fF时不同频率下各个全加器的平均功耗(μW).从测试结果可看出,本文提出的8管全加器在100~500MHz下随着频率的增加低功耗的优势逐渐明显.在500MHz下,与图1中5种全加器相比功耗改进8.0%~37.8%.

表1 负载电容为100fF时不同频率下各种全加器平均功耗(μW)的比较Table 1 Comparison of power consumption(μW)at different frequencies with a load of 100fF

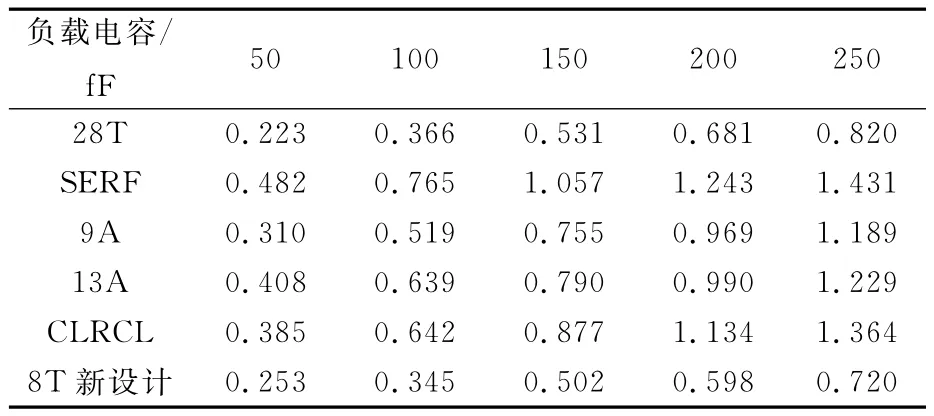

传播延迟时间是指输入信号变化到50%电源电压到输出信号变化到50%电源电压时之间的时间间隔[9],延迟时间取不同输入组合模式下电路翻转时的最大传播延迟时间.表2是频率为200MHz时不同负载电容下各种全加器延迟时间(ns).从表中可看出,与图1中提到的典型全加器相比,本文提出的8管全加器在50~250fF负载电容下随着负载的增加时间延迟上的优势逐渐明显.在200fF下,与图1中5种全加器相比延迟改进12.1%~51.9%.

表2 是频率为200MHz不同负载电容时各种全加器延迟时间(ns)的比较Table 2 Comparison of delay(ns)at different output loads with a frequency of 200MHz

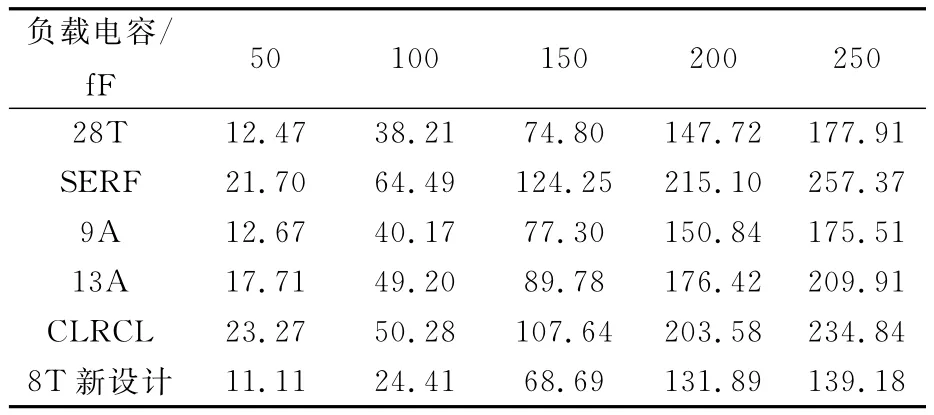

功耗延时积(PDP)是衡量电路性能的较全面指标之一[10].表3是频率为200MHz时不同负载电容下各种全加器功耗延迟积的比较,可看出,在不同负载下,新全加器电路有较好的功耗延迟积,在负载是200fF下功耗延迟积比图1中提到的典型全加器改进10.7%~38.7%.表明新设计有较好的性能.

表3 是频率为200MHz不同负载电容时各种全加器功耗延迟积(fJ)的比较Table 3 Comparison of delay(ns)at different output loads with a frequency of 200MHz

4 结 语

通过对典型全加器电路的研究分析,提出了新型8管全加器电路,新电路包括2个3管同或门模块和1个选择器模块,与已有的典型全加器电路相比,新设计不仅减少了晶体管数目,而且在功耗、速度和功耗延迟积上有较大的优势,可应用于进位加法器和乘法电路中.

[1]Chandrakasan A P,Brodersen R W.Low Power Digital CMOS Design[R].MA:Kluwer,1995.

[2]Zimmermann R,Fichtner W.Low-power logic styles:CMOS versus pass-transistor logic[J].IEEE J Solid State Circuits,1997,32(7):1079-1090.

[3]Rabaey J M,Chandrakasan A,Nikolic B.Digital Integrated Circuits A Design Perspective[R].New Delhi:Prentice-Hall of India Pvt Ltd,2004.

[4]Weste N,Eshraghian K.Principles of CMOS VLSI Design,a system perspective[R].MA:Assison-wesley,1993.

[5]Zhuang,Wu H M.A new design of the CMOS full adder[J].IEEE J Solid-State Circuits,1992,27(5):840-844.

[6]Abu Shama E,Bayoumi M.A new cell for low power ad-ders[C]//Proc Int Midwest Symp Circand Syst.USA:[S.I.],1996:49-52.

[7]Shalem R,John E,John L K.A novel low power energy recovery full adder cell[C]//Ninth Great Lakes Symposium on VLSI.USA:IEEE Computer Society,1999:380-383.

[8]Bui H T,Al Sheraidah A K,Wang Y.Design and analysis of 10-transistor full adders using novel XOR-XNOR gates[J].IEEE Transactions on Circuits and System,2002,1(49):25-30.

[9]Lin J F,Hwang Y T,Sheu M H,et al.A novel high speed and energy efficient 10-transistor full adder design[J].IEEE Trnas,2007,54(5):1050-1059.

[10]Chowdhury S R,Banerjee A,Roy A,et al.A high speed 8transistor full adder design using novel 3transistor XOR gates[J].International Journal of Electronics Circuits and Systems,2008,2(4):217-223.