“Verilog数字系统设计”课程教学改革

2013-07-05蒋华,徐晨,宋超

蒋 华,徐 晨,宋 超

(南通大学1.电子信息学院,江苏 南通226019; 2.南通大学 杏林学院,江苏 南通226007)

“Verilog 数字系统设计”是我校电子信息工程类专业的一门核心课程。该课程难教和难学的原因有以下四点:①教学内容太多而其课堂授课时间有限;②学生听课后很难及时完全理解实践性很强的教学内容,也很难将教学内容与实践紧密地联系起来;③教师和学生的交流互动不够;④课程实验难度大,而实验学时安排有限。

针对以上问题,从我校电子信息工程类2006 级学生开始,我们逐步对该课程进行教学改革。我们基于因材施教的思想,对课程教学内容进行了修订,建立了一套新的实验教学模式,同时建立了一个采用ASP 语言开发的辅助教学网站来帮助学生学习该课程,学生可以在课后充分利用我校EDA 实验教学中心开放式的实验条件,并利用辅助教学网站与教师互动,共同改进该课程的学习效果[1]。

1 教学改革总体目标与措施

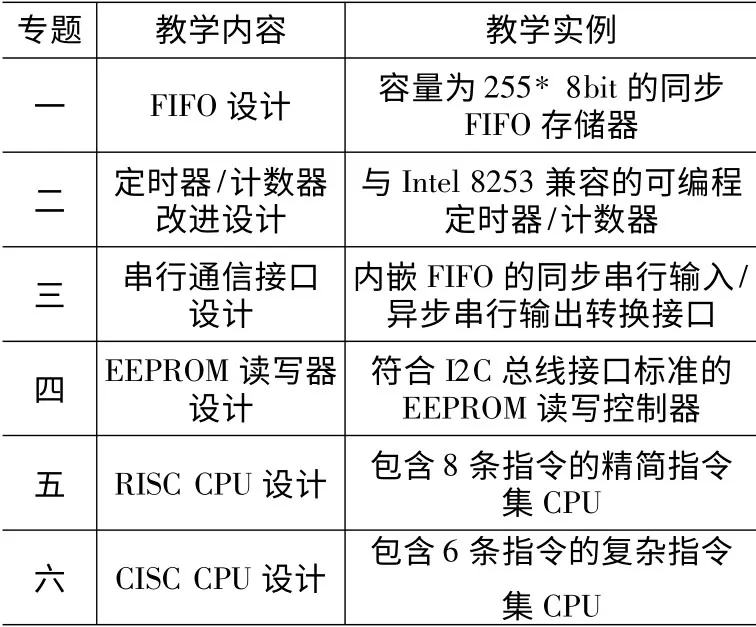

针对“Verilog 数字系统设计”课程的学习要求,我们修订了课程教学大纲和改造了教学方法,合理地减少理论教学内容[2],将其划分成六个专题,如表1所示。

同时,我们还改革了实验教学模式,延长了学生课后的自主学习和自主实践的时间,逐步完善课程的网络辅助教学。为了配合课程教学改革,建立更加有利于学生完成实践训练的环境,我校EDA 实验教学中心建立了完全开放式的实验室预约和使用管理制度,确保每位学生均能够得到在实验室完成课程实验的充足机会[3,4]。

表1 课程教学内容

2 实验教学改革

我们将传统的实验题目要求进一步分解和细化,划分为基本要求和提高要求两项,且所有实验题目的类型都是设计型。其中的提高要求则不是每个学生都必须完成的,仅供学有余力的学生自主选做。此外,我们还为每一次的实验设计了多种难易程度不同的功能供学生选择,学生可以在实验课开始之前自主选择一组功能,以达到基本要求。

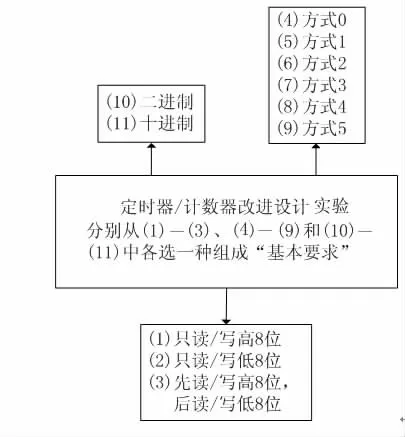

我们以“定时器/计数器改进设计实验”为例介绍具体做法。一个功能可配置的三通道六种工作方式定时器/计数器(参照Intel8253 芯片)的逻辑功能主要包括:①减法计数器可以按照二进制或十进制两种方式计数;②定时器/计数器的工作方式可以是方式0 到方式5 六种中的任何一种;③16 位的减法计数器可以设置为锁存器、只利用其高8 位计数、只利用其低8 位计数或先利用其低8 位后利用其高8位计数四种功能中的任何一种。

由于三个计数器通道是完全相同的,我们以其中任意一个通道为例,将单个通道的逻辑功能细分为11 项基本功能,即如图1中的(1)~(11)所示。

我们的基本要求是:每位学生从(1)~(3)、(4)~(9)和(10)~(11)三组中各选一种功能组合成一个实验题目,然后独立完成设计和实现。这三组不同要求的功能,其侧重点都不同。对学生来说,基本要求不是一成不变的,而是可以进行自主选择。对教师来说,这样既简化了题目的总体难度,又可以使每个学生完成的题目尽可能各不相同,既考虑到了学生之间的个体差异,又避免了设计结果的抄袭。对于学有余力的学生,可以在完成基本要求的前提下选做其它功能,实现提高要求。

图1 功能可配置的实验教学模式实例

这种实验教学模式可以总结为:①学生在实验课之前,可与教师商量选题,选择期望实现的基本功能,并确定设计方案;②学生画出完整的状态转换图,标注出各个状态之间相互转换必须满足的条件;③学生完成Verilog 程序编码,利用Quartus II 完成编译、仿真和下载验证;④教师对实验结果进行检查验收;⑤学生完成实验报告;⑥教师根据学生的综合表现,确定其实验课的成绩等级。

3 课程辅助教学网站

针对我校学生的特点,我们设计的“Verilog 数字系统设计”课程辅助教学网站紧密结合课程教学内容的六个专题,采用浏览器/服务器(B/S)模式,用ASP 语言开发,以满足不同基础的学生需要。该课程辅助教学网站是密切联系课堂教学内容的第二课堂,其内容的深浅程度、专业程度和准确程度都经过精心挑选。其具体实现主要包括后台数据库和各个专题的页面设计。辅助教学网站的结构,主要包括教学信息动态发布子系统、资料上传下载子系统、提问子系统、公告栏子系统、调查子系统、在线测试子系统和实验课件子系统等七个子系统。

4 课程评价方式

“Verilog 数字系统设计”课程的评价方式,由平时成绩和期末考试成绩综合确定。其中,平时成绩占30%,考试成绩占70%。平时成绩主要是由实验成绩决定,这符合本课程侧重于实践的要求。由于考试成绩占总评成绩的比例较高,因此考试环节非常重要。

本课程的考试题目,在学期末从试卷库中由系主任随机抽取获得。试卷库由四份难易程度接近的试卷组成。主要有单项选择题、判断题、填空题和程序设计题等题型。基本涵盖了本课程教学大纲中的重点和难点。

通过这几年的教学实践,我们的“Verilog 数字系统设计”教学改革已经取得了良好的成效。学习过该课程的学生,运用Verilog HDL 设计数字系统设计的能力普通增强。

[1] 杨全胜,吴强. 基于网络辅助教学的研究性学习教学模式[J]. 南京:电气电子教学学报,2011,23(3):91-93

[2] 蒋华,袁红林. C8051 微控制器IP 软核的参数化设计[J]. 北京:微计算机信息,2007,23(10-2),104-106

[3] 周晖,蒋华.“硬件描述语言”课程的教学改革探索[J]. 南宁:高教论坛,2008,(6):184-186

[4] 蔡惟铮,胡晓光,王立欣等. 电子技术基础课程体系的改革与教材编写的实践[J]. 南京:电气电子教学学报,2001,23(3):17-20