磁感应成像系统激励源的教学实践设计

2013-07-05杨丹,徐彬,王骄

杨 丹,徐 彬,王 骄

(东北大学1 信息科学与工程学院,2 计算中心,辽宁 沈阳110819)

0 引言

磁感应成象MIT (Magnetic Induction Tomography)系统是典型的主动式数据采集系统,其激励源设计不仅决定了激励磁场的强度和形式,还很大程度影响着检测线圈对扰动磁场的检测精度和灵敏度[1]。为了得到高质量的检测信号,要求MIT 激励源的输出具有较高的频率稳定度和相位测量精度,波形失真小,频带适合,无相位漂移等。为了有效地区分被测生物的不同组织成分,或是同种组织所处的不同状态,往往需要在多频和多相位的模式下测量,实现对组织进行多频成像或参数成像[2]。同时生物组织的电导率信号在10kHz ~10MHz 医学应用范围内较为明显。因此,MIT 激励源要求是多频移相激励源,且频率带宽在10kHz ~10MHz 范围[3]。

对于MIT 激励源,工程设计中多采用直接数字频率合成DDS(Direct Digital Syntheaizer)方法。常用的实现方案有两种:一是采用单片机结合高性能DDS 芯片,二是基于可编程逻辑器件实现。采用FPGA 设计的DDS 激励源既具有速度和成本的优势[4],还可将DDS 激励源模块嵌入到一片FPGA 芯片上实现激励源的信号产生和控制,并通过改变ROM 数据灵活输出多种自定义波形,同时输出信号的频率稳定性提高。因此,EDA 课程设计中,采用了FPGA 实现DDS 来构造磁感应成像系统激励源。

1 DDS 的FPGA 实现方案

1.1 基本原理

DDS 的FPGA 实现方案如图1所示,其中地址加法器有两个数据输入端:一个输入端B 与数据锁存器的输出相连;另一个输入端为相位增量DATA,它决定了DDS 输出频率,称为频率控制字FCW(Frequency Control Word)。地址加法器的输出结果为DATA+B,在时钟CLK 的作用下,数据锁存器的输出数据D0 ~D10 每次将增加一个DATA。在时钟CLK 不变的情况下,DATA 的大小控制着D0 ~D10从最小值变到最大值所用的时间。DATA 越大,数据存储器的地址增长越快,地址循环一周所需时间越短,对数据存储器寻址的单元数越多,输出的数据点越多,经过D/A 转换后输出信号的频率越高。

图1 DDS 的FPGA 实现方案

1.2 参数选择

根据DDS 的实现方案可知,数据存储器输出信号频率f 与控制字DATA 之间的关系为

式中f0为系统时钟信号CLK 的频率;m 为地址加法器的数据宽度。

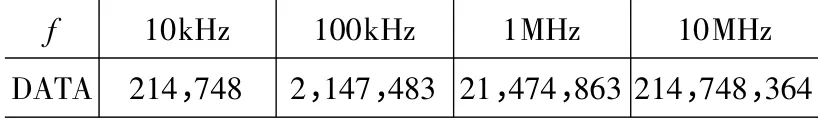

(1)控制字设置:本设计中,地址加法器数据宽度m=32,ROM 的存储量为1024* 10bit,系统时钟频率50MHz,经过锁相环PLL 倍频到200MHz,所有根据式(1)实现不同频率输出信号,所设DATA 如表1所示。

表1 控制字设置

(2)移相处理:本设计中ROM 地址线数10,若要移相1°,则1024/360 =2.844,步进可定为3。其它步进值如表2所示。

表2 移相对应的步进值

2 DSP Builder 模型设计

利用DSP Builder 实现激励源可采用如下设计过程:①打开Matlab/Simulink,新建一个模型命名为sim_dds.mdl;②打开Simulink 库管理器,调用Altera DSP Builder Blockset 中的模块构成DDS 核心电路,设计成DDS 模型子系统SubDDS;③添加其他辅助模块。

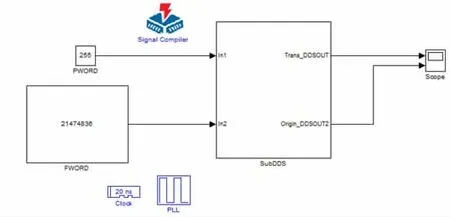

实现的DDS 顶层电路模型,如图2所示。

图2 DDS 正弦移相的顶层设计

顶层设计中的模块采用如下的参数设置。

(1)Signal Compiler

库:Altera DSP Builder Blockset 中AltLab

(2)系统时钟Clock 模块

库:Altera DSP Builder Blockset 中Rate Change

参数:“Real World Clock Period”设为20

参数:“Period Unit”设为ns

(3)嵌入式锁相环PLL 模块

库:Altera DSP Builder Blockset 中Rate Change

参数:“Period Divider”设为4

Parameters 显示Output periods:5 ns

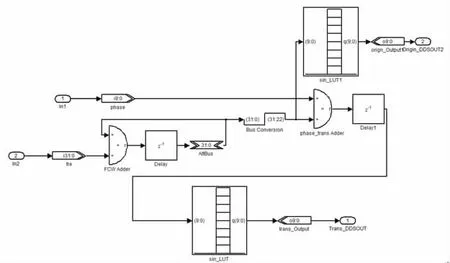

子系统SubDDS 共有2 个输入:in1 是PWORD(10 位相位字输入,控制输出信号的相移量);in2 是FWORD(32 位频率字输入,控制输出信号的频率)、2 个输出:输出1 是加入移相控制字后的输出信号Trans_DDSOUT 输出,输出2 是未经过移相的DDS输出信号10 位Origin_DDSOUT。所有元件的类型都选择成为无符号类型,设计的子系统SubDDS 的结构,如图3所示。

图3 子系统SubDDS 的结构图

子系统SubDDS 输入输出模块采用如下的参数设置。

(1)输入部分

①fre 模块(Altbus)

库:Altera DSP Builder Blockset 中IO & Bus

参数“Bus Type”设为“Unsigned Integer”

参数“number Of bits”设为“32”

②Phase 模块(Altbus)

库:Altera DSP Builder Blockset 中IO&Bus

参数“Bus Type”设为“Unsigned Integer”

参数“number of bits”设为“10”

所有总线模块,设置无符号整数,32 位。

(2)输出部分

Origin_DDSOUT 和Trans_DDSOUT 模块(Altbus):

库:Altera DSP Builder Blockset 中IO&Bus

参数“Bus Type”设为“Unsigned Integer”

参数“number of bits”设为“10”

(3)相位累加器

由Delay,FCW Adder,AltBus,phase_trans Adder和Bus Conversion 模块构成,采用如下参数。

①Delay 模块

库:Altera DSP Builder Blockset 中Storage

参数“Depth”设为“1”

参数“Clock Phase Selection”设为“1”

②FCW Adder 模块

库:Altera DSP Builder Blockset 中Arithmetic

参数“Number of Inputs”设为“2”

“Add(+)Sub(-)”设为“+”

所有加法器模块均设置成2 输入。

③AltBus 模块

库:Altera DSP Builder Blockset 中IO & Bus

参数“Bus Type”设为“Unsigned Integer”

参数“number Of bits”设为“32”

④phase_trans Adder 模块

库:Altera DSP Builder Blockset 中Arithmetic

参数“Number of Inputs”设为“2”

“Add(+)Sub(-)”设为“+ +”

⑤Bus Conversion 模块

厍:Altera DSP Builder Blockset 中IO & Bus

参数“Bus Type”设为“Unsigned Integer”

参数“Input[number of bits].[]”设为32

参数“Output[number of bits].[]”设为“10”

参数“Input Bit Connected to Output LSB”设为“22”

(4)波形存储器

由sin_LUT 和sin_LUT1 模块构成的存储器,采用如下参数。

库:Altera DSP Builder Blockset 中Storage

参数“Address Width”设为“10”

参数“Data Type”设为“Unsigned Integer”

参数“[].number of bits”设为10

参数“Matlab Array”设为511* sin([0:2* pi/(2^10):2* pi])+512

所有LUT_ROM 模块,参数设置如图4所示。

图4 设置LUT_ROM 模块

3 DSP Builder 模型仿真

用DSP Builder 模块设计好一个模型后,可以在Simulink 环境中进行算法、系统级仿真验证。具体采用如下的步骤。

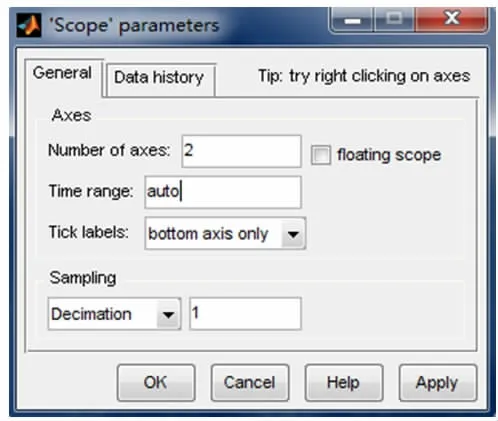

(1)添加波形观察Scope 模块

库:Simulink 中Sinks

双击打开该模块,如图5所示,点击第二个图标“Parameter”在General 标签下的“Number of Axes”中选择2,这是因为在仿真时需要观察两路波形。第二个标签“Data history”中勾选“Limit data points to last”选项,输入点数50000。

图5 示波器的设置

(2)设置仿真激励

在顶层模型图中,需要给DDS 模块添加输入频率控制字FWORD 和相位控制字PWORD 激励。在模拟仿真时,调整这两个值观察波形。

库:Simulink 库Sources 中Constant

(3)启动仿真

设置仿真时间Stop Time 为1e-3。

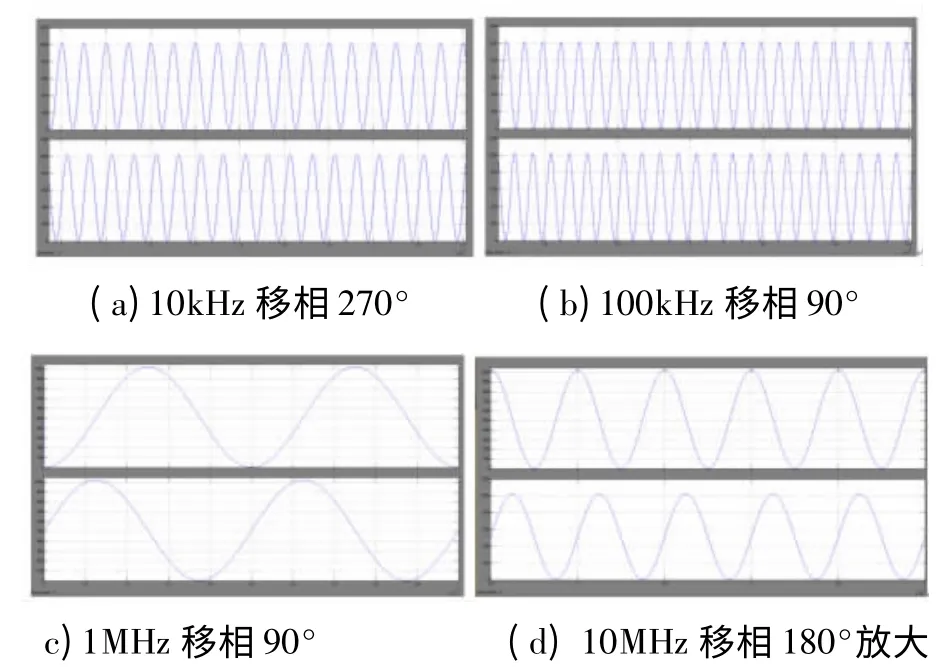

设置频率控制字FWORD 和相位控制字PWORD,在sim_dds 模型编辑窗口中,选择Simulation->Start,开始仿真,双击Scope 模块观察输出波形,如图6所示。

图6 不同的FWORD 和PWORD 的10 位数字信号

当FWORD =214748,PWORD =767 时,输出10kHz 移相270°的10 位数字信号,输出如图6(a)所示。由于频率较低,地址信号能将ROM 中所有1024 点都取到,所以波形十分光滑;当FWORD =2147483,PWORD=255 时,输出100kHz 移相90°的10 位数字信号,输出如图6(b)所示;当FWORD =21474836,PWORD=255 时,输出1MHz 移相90°的10 位数字信号,输出如图6(c)所示。从图可见,随着频率增高,每周期内地址信号从ROM 中提取的信号逐渐变少,导致波形颗粒感增加。当FWORD=214748364,PWORD =511 时,输出10MHz 移相180°的10 位数字信号。由于信号频率很高,为了细致观察波形,单击窗口中的放大镜按钮,逐步放大查看效果,如图6(d)所示;当达到10MHz 时,每周期只能取到ROM 中的20 个点。

根据上述仿真过程,若想继续提高频率,需考虑增加地址线的位数和提高系统的时钟。针对医学领域的MIT 成像系统所要求的10k ~10MHz 来说,目前的设计已经可以达到标准。

4 结语

笔者长期从事EDA 教学和相关的应用系统设计工作,发现学生在进行硬件系统设计时盲目追求方案的实现,缺乏从工程需求出发提出解决方案以及验证模型设计可行性的能力。本文以磁感应成像系统中激励源的设计为例,介绍如何从工程需求确定解决方案,如何使用DSP Builder 完成系统设计中的模型验证,希望以此加强学生使用DSP Builder 进行工程系统设计的能力,提高学生在进行实际工程研发时分析问题和论证方案的能力。

[1] 刘国强,医学电磁成像[M]. 北京:科学出版社,2006,8:175-179

[2] Engineering in Medicine and Biology,Amsterdam[M].1996 6:1938-1939

[3] Basak Ulker Karbeyaz,Nevzat G Gencer,Electrical Conductivity Imaging via ContactlessMeasurement:An Experimential Study[J],Iowa,USA,IEEE TRANSACTION ON MEDICAL IMAGING,2003,22(5):627-635

[4] 李翠华.基于FPGA 直接数字频率合成器的设计[J],南昌,科技广场,2009,(07):197-198