基于FPGA的数字存储示波器设计

2013-06-29耿新力王中训

耿新力,王中训

(烟台大学光电信息科学技术学院,山东 烟台 264005)

示波器作为一种常用仪器,在实验室和工业化生产线是不可缺少的,并且至今成功完成了从第1代到第7代的改革,八十年代之后数字信号处理技术和微处理器的运用在该行业兴起,不久之后便出现了目前广为使用的高性能数字存储示波器[1]。数字存储示波器一般采用微处理器进行数据采集和系统控制,具备组合触发、超前触发、波形处理、毛刺捕捉、数字滤波、输出并拷贝、波形识读、长时间波形存储等模拟示波器所不具备的功能[2]。随着产业的发展,对数字存储示波器的功能和性能指标的需求不断提高,更高性能的数字存储示波器必将是发展的必然。本设计基于Altera公司的EP2C35系列处理器,在模拟数据的采样、信号频率的测量、自检信号的产生、个性化的波形显示等环节分别进行了创新性优化,最终设计制作出一款更高性能且廉价的数字存储示波器[3]。

1 系统方案

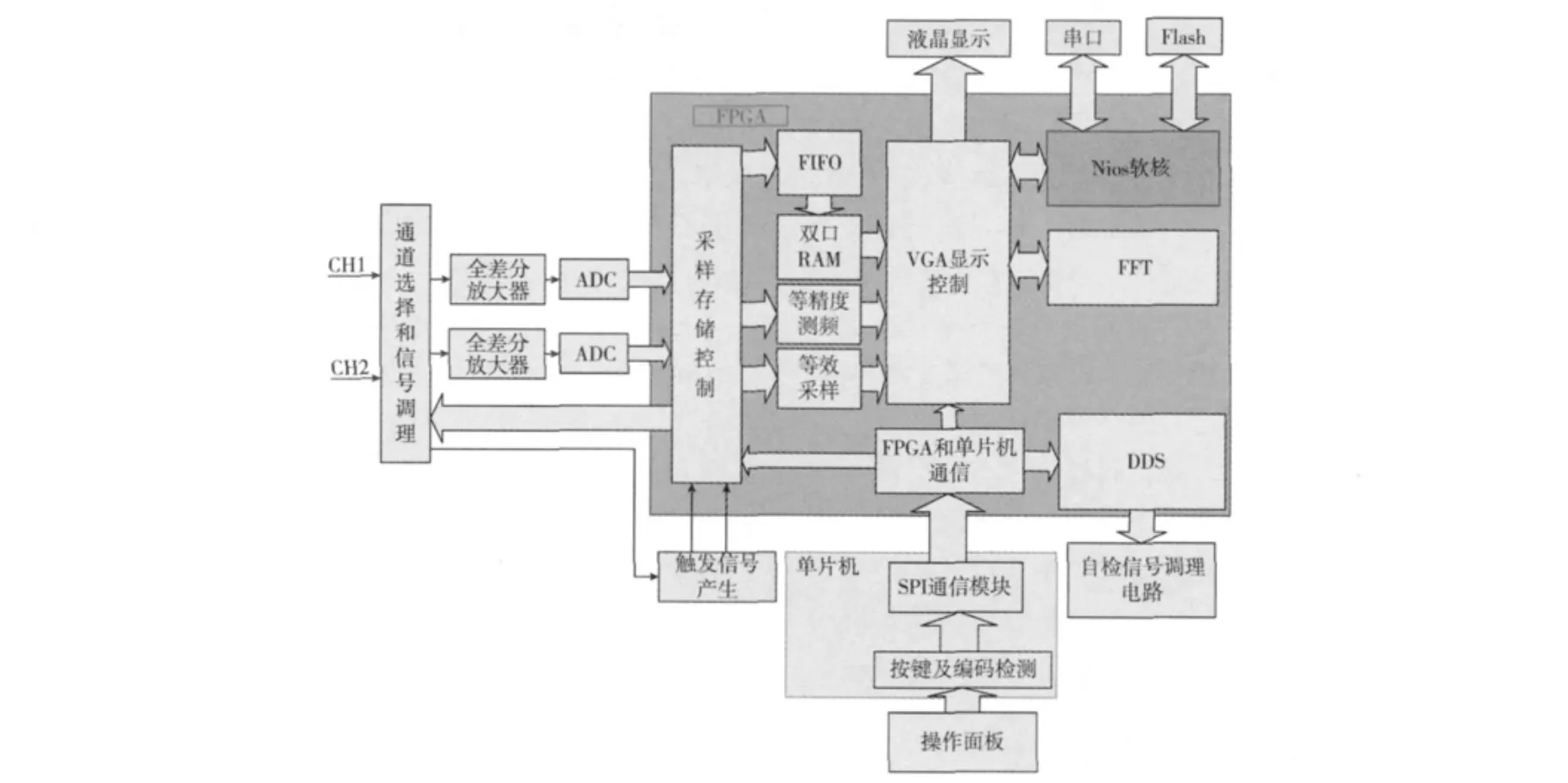

当信号进入数字存储示波器时,首先示波器将按一定的时间间隔对信号电压进行采样,之后对这些采样值进行数字化,即通过转换器变换得到代表每一个实际电压的二进制数字,进一步把这些数字贮存在存储器中,最终根据数字大小按一定比例把每一个采样点重现在显示器上,这样就能看到清晰的波形[4]。本设计的总体框图如图1所示。

本系统在采样和数字化阶段对电路进行了改进,首先要模拟信号经过全差分放大器的预处理将单端信号转化为差分信号,由高速ADC芯片将差分信号转换成二进制数字信号,通过采样存储控制模块控制FIFO(First Input First Output)[5]和双口RAM协调工作完成前端数据采集,通过FIFO来匹配信号采样时钟和系统时钟的不同,双口RAM存储采样后的数据,后端VGA显示控制模块从双口RAM中定期读取数据,并送至液晶屏实时刷新显示。为了给示波器提供自检信号,利用了DDS(Direct Digital Synthesizer)原理产生自检信号,另外为提高数据的利用效率,采集到的波形数据可以由FPGA内嵌的Nios软核编程传到计算机,也可存储到Flash中用于波形的回放。

2 系统各模块设计

2.1 垂直灵敏度和水平灵敏度

图1 系统总体框图

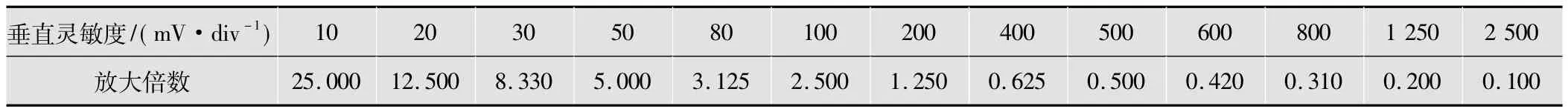

垂直灵敏度对应着对信号的放大倍数,设计由TI公司生产的高速运放Opa690构成的电压跟随器以隔离各模块并提高驱动后级电路的能力,配合VCA810实现了自动增益控制电路,部分档位的垂直扫描灵敏度所对应的调理电路放大倍数如表1所示[6]。

表1 部分档位与放大倍数的关系

水平灵敏度对应着ADC的采样速率,显示屏选用7 in(1 in=2.54 cm)寸液晶屏 AT070TN92,分辨率为800×480(RGB),将波形有效显示区域制定为600×400,垂直分为8个格,水平分为12个格,得到50×50像素的格子。对于每个格子有50个点,那么采样速率和时间档(水平灵敏度)的关系满足

式中,T为每个水平格代表的时间,和时间档相对应。

2.2 高速ADC采样模块

模拟信号到数字信号的转换电路主要由TI公司全差分运算放大器THS4503ID、RC组合接口以及高速ADC芯片ADS828构成。全差分运算放大器THS4503ID实现了单端信号到差分信号的转换,差分信号具有抑制共模干扰的能力,差分信号相当于一对相位相差180°的单端信号相减,因此能提供2倍于单端信号的输入信号动态范围,如图2所示,若同样提供2 V(峰峰值)的信号,差分信号每一条仅需1 V(峰峰值),这样净空较大,失真较小。

放大器和高速ADC之间的RC接口电路可以提供隔离,并且可以起一个低通的噪声滤波器的作用,10 bit高速ADC转换器ADS828的最高采样频率为75 MHz,满足最大实时采样频率为70 MHz的要求[7]。

图2 单端信号转化为差分信号

2.3 触发信号产生电路

为了在屏幕上显示比较稳定的波形,对于周期信号必须保证每次采样的起始位置相同。为了兼顾高速电压比较器TL3016良好的高频特性和LM311滞回比较器优良的低频特性,本系统利用TL3016和LM311制作双路触发信号产生电路,根据实际信号频率选择不同的触发信号产生电路。

2.4 波形数据采集模块

由图1的系统框图以及本系统控制水平灵敏度的方法(通过改变高速ADC采样时钟频率来改变水平灵敏度)可以看出,这个设计必然带来ADC的采样时钟和FPGA系统时钟的不匹配问题,为解决前后时钟不匹配问题本系统引入了一个深度为1024 点的FIFO来匹配采样时钟和系统时钟,辅以双口RAM来暂存采样数据,两者协调工作不仅提高了本系统的工作效率也保证了显示的稳定。

2.5 等精度频率测量模块

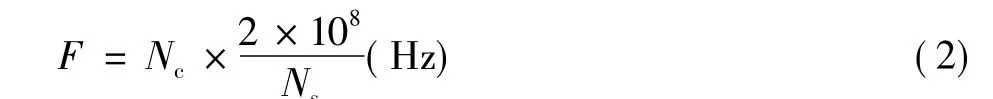

如图3所示,被测信号经过触发信号产生电路和相应的整形电路产生比较标准的方波信号,由FPGA的I/O口输入频率测量系统,标准信号由50 MHz系统时钟倍频至200 MHz,在系统初始状态预置一个预置闸门,当预置闸门为高电平(允许计数)时,当被测信号的下降沿到达D触发器输入端时同时启动计数器1和计数器2分别对标准信号与被测信号计数,而当计数到预置闸门拉低的时候实际闸门并不是立即关闭,而是等待下一个被测信号的下降沿的到来,当D触发器采样到该下降沿时才能关闭实际闸门[8],假定一次测量过程中实际的闸门时间内对标准信号的计数值为Ns,对被测信号的计数值为NC,由于该系统采用的标准信号为200 MHz,所以被测信号频率为

图3 等精度频率测量系统框图

2.6 幅度测量

示波器要能够对被测量信号的频率、峰峰值和有效值进行实时性的准确测量,本系统利用FPGA在数字信号处理方面的速度和精度的优势,可以直接对采集到得数字量结合统计学原理很方便地测得被测信号的峰峰值和有效值并予以显示。

2.7 基于DDS的自检信号发生器

由于示波器在特定的场合需要校正,特制作基于DDS(直接数字合成)的自检信号发生器,使本系统使用场合更广,功能更加强大。DDS从相位角度考虑能够产生正弦波、三角波、方波以及任意编辑波形,而且波形的频率、幅度、相位均可以灵活调整,并且精度较高、具有较高频率切换率。

DDS方程为

其中:fO为需要输出的模拟信号的频率,K为频率控制字,fc为DDS模块的系统时钟频率[9]。

2.8 SOPC资源配置及波形存储

软件部分利用了FPGA内嵌的软核Nios,来控制波形的存储、回放,并且将波形数据通过串口传送到计算机,之后便可以利用图形化设计软件VB或LabVIEW在计算机上设计比较人性化的显示界面,或者对采集到的波形数据进行处理。

Flash存储器使用AMD公司的AM29LV320DB90EI,存储区可以配置成两种,一种模式是,存取2 Mbyte个字,每个字16 bit,分别为D0~D15。另一种存取模式是存取4 Mbyte个字,每个字8 bit,分别为D0~D7。系统选用的高速ADC是10 bit,所以将AM29LV320DB90EI配置成第一种模式。根据存储波形的多少控制存储地址。掉电后波形数据存在Flash相应空间中,需要再次显示上次或某个波形时只要按该波形对应的存储地址读出即可。

3 测试结果及分析

3.1 测试条件

测试温度为26℃,信号发生器为RIGOL-DG1022型,选用RIGOL-DS1102C型示波器作为标准示波器。采用分模块的测试方法依次测试各项功能。

3.2 测试结果

3.2.1 波形测试

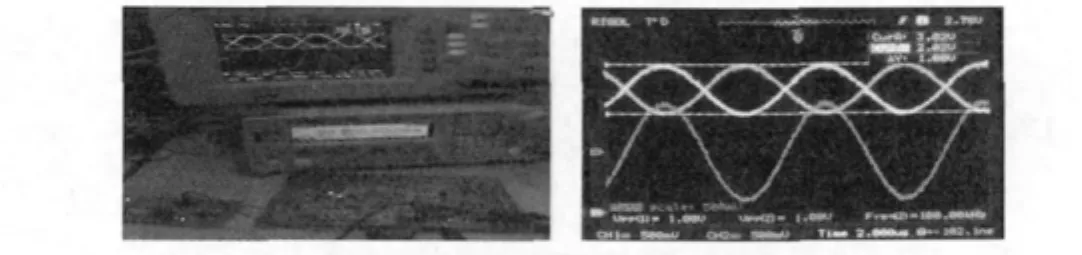

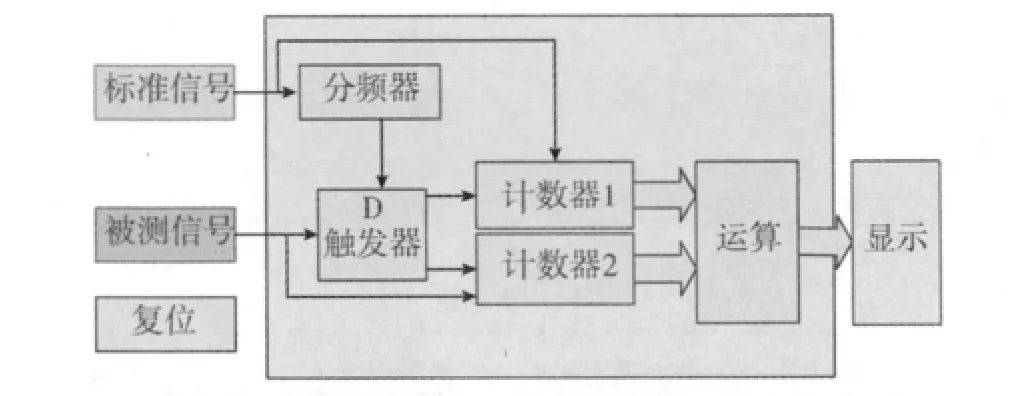

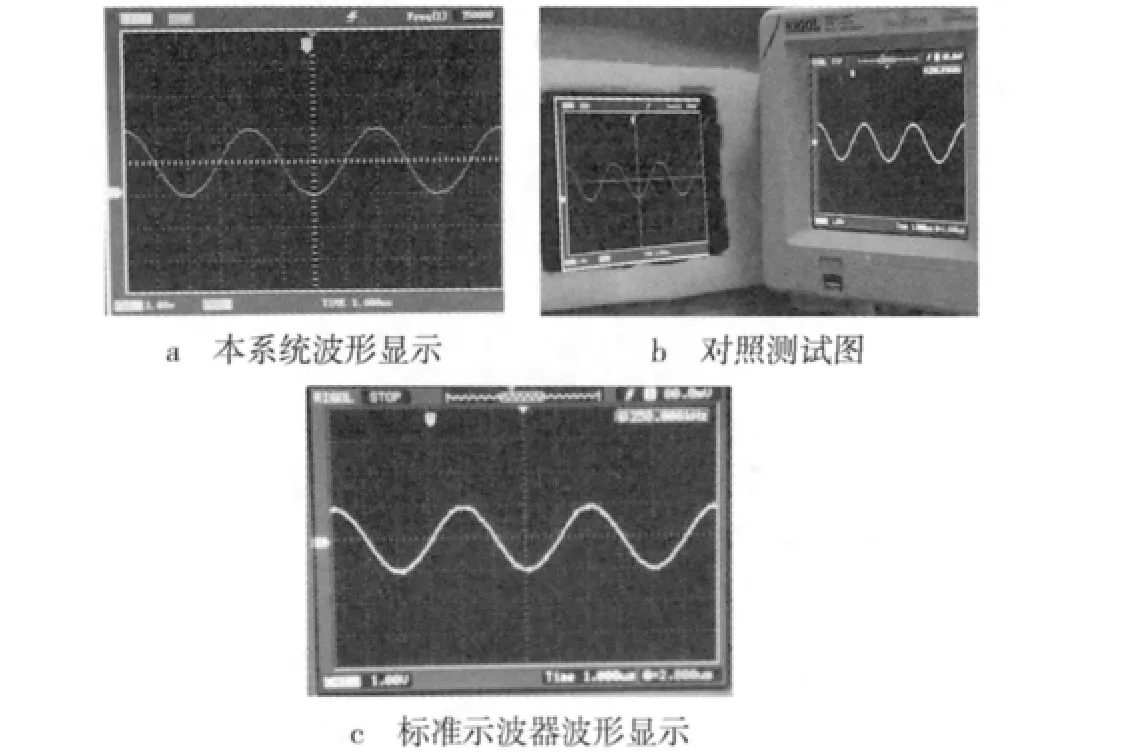

测试结果如图4所示。

图4 本系统波形显示与标准示波器波形显示对照图

通过对比标准示波器和本系统的波形显示可以看出系统工作稳定,各项基本指标显示正确,同时也验证了对模拟信号预处理、触发方式、数据存储机制的优化的正确性。

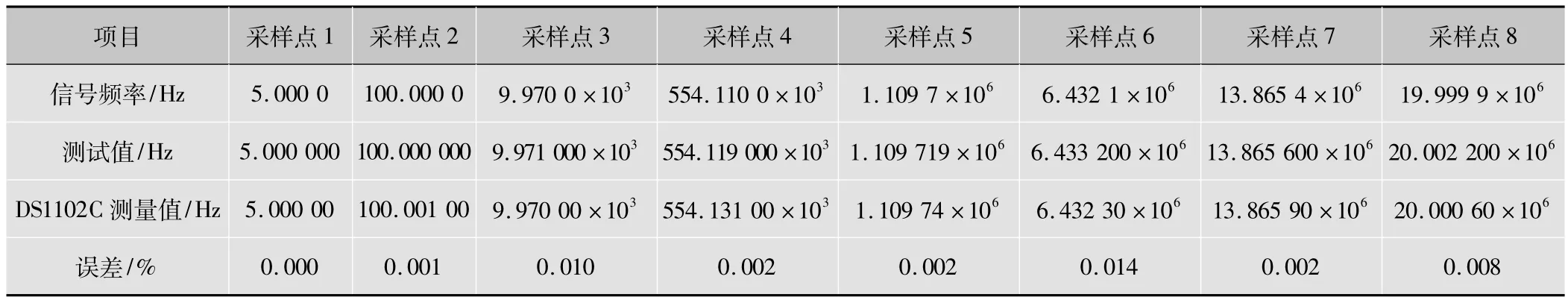

3.2.2 频率、电压测试

调节函数发生器,依次保持输入信号的电压、频率不变,将输入信号的频率、电压依次以一定步进值步进,观察系统测量值,测量数据如表2、3所示。

通过频率和电压的测试结果可以说明,系统可以准确的测试频率5~20 MHz,幅度(峰峰值)0~10 V的模拟信号,并且频率的误差控制在0.000% ~0.015%之间,幅度测试误差1.00% ~4.50%之间,在允许范围内。

3.2.3 波形数据多方位存储测试

经测试,当需要存储波形数据时可正确通过NIOS调用双口RAM里的波形数据,并将这些数据存储在Flash中,当需要回放原来的波形数据时也可以正确的调出原来存取的数据,并在显示屏上显示,不丢失采样点,另外系统与上位机的交互正常,完成了数据到Flash和上位机的多方位存储。

表2 频率测试结果及误差表

3.2.4 基于DDS的自检信号测试

经多次检测,自检信号产生模块可以正确输出频率0~5 MHz,幅度(峰峰值)0~10 V的无失真模拟信号,另外也可对波形的频率和幅度以任意步进值进行编辑,达到了预定要求。

4 结论

本设计通过FPGA进行了数字存储示波器的设计,克服了同步信号的提取和高频噪声的消除等难点问题。采用双路触发信号产生电路既兼顾了低频信号的测量也兼顾了高频信号的采集,解决了采集高速信号和低速信号之间的矛盾,取得了良好的效果,另外在等精度测频模块对标准信号的选取也经过了多次仿真和实施,使得数值的选取和理论的研究真正具有实用性。该系统提出FIFO+RAM存储机制、数据的多方位存储、信号预处理等优化方法,对数字存储示波器的发展具有一定的参考和实用价值。

[1]朱明强.基于单片机及CPLD的数字存储示波器的研究与设计[D].北京:北京交通大学,2008.

[2]汤向恒.模拟示波器扩展为数字示波器[J].自动化与仪器,2003,18(5):26-28.

[3]刘君华.现代检测技术与测试系统设计[M].西安:西安交通大学出版社,1999.

[4]徐欣,于红旗.基于FPGA的嵌入式系统设计[M].北京:机械工业出版社,2005.

[5]ROBERTO P A.A versatile linear insertion sorter based on an FIFO scheme[C]//Proc.Symposium on VLSI,2008.[S.l.]:IEEE Press,2008:357-362.

[6]TESSIER R,BETZ V,NETO D,et al.Power-efficient RAM mapping algorithms for FPGA embedded memory blocks[J].IEEE Trans.Computer-Aided Design of Integrated Circuits and Systems,2007,26(2):45-52.

[7]王松武.电子创新设计与实践[M].北京:国防工业出版社,2005.

[8]夏宇闻,黄然.Verilog SOPC高级实验教程[M].北京:北京航空航天出版社,2009.

[9]CAO X H,LUO F L,BAI F T,et al.A DDS waveform generator for electromagnetic nondestr-uctive testing[J].Key Engineering Materials,2005(6):12-21.