基于DSP+FPGA的远程屏幕传输系统

2013-06-29王雪萍唐林波赵保军

王雪萍,唐林波,赵保军

(北京理工大学信息与电子学院,北京 100081)

远程屏幕传输是指将一台计算机上的屏幕信息通过计算机网络实时传输到另一台计算机上并重新显示出来,在计算机远程控制和监控中有广泛应用。传统的视频监控存在实时性差和图像清晰度不高的缺点[1]。本文设计了一种基于DSP+FPGA的远程图像传输系统,实现主机屏幕图像截取、压缩和传输。采用TCP/IP协议,通过网络接口传输给局域网上其他计算机,在其他计算机上进行实时解压缩显示。局域网上任何一台计算机上均可看到本机屏幕上的内容,对计算机进行实时监视。

本文采用两种方案实现远程屏幕传输,提出了系统的总体实现结构,并给出系统不同模块的具体设计。

1 系统的整体设计方案

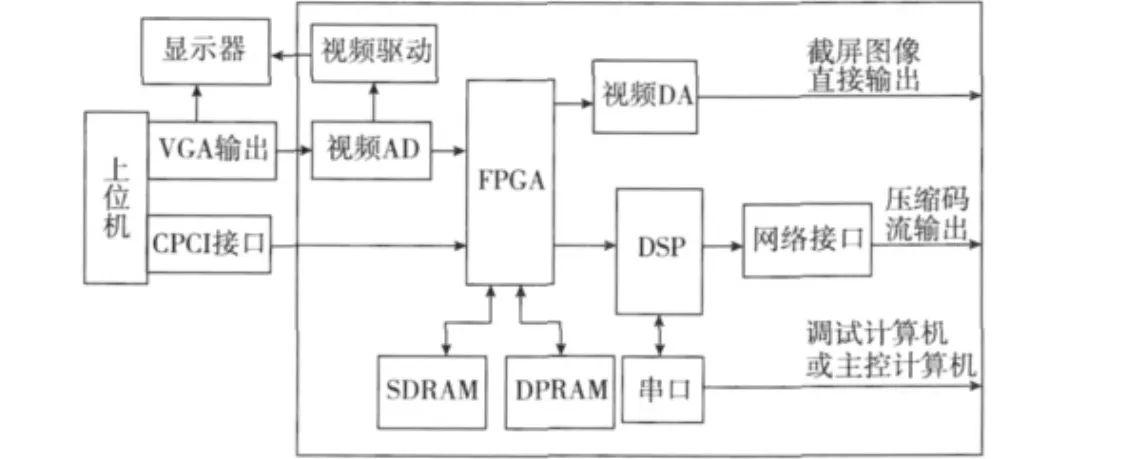

图1是远程屏幕传输系统的结构框图。使用两种方案进行截屏,主要是截屏数据源和FPGA的处理数据工作不一样,DSP进行数据压缩的功能是相同的。方案一是上位机读取计算机内存中的数据通过PCI接口将数据发送给FPGA,FPGA进行数据格式的调整,存储到DPRAM中。再将DPRAM中的数据发送给DSP。同时,从DPRAM中以符合VGA显示的时序读取数据并再次转换数据格式,进行实时的VGA截屏显示。方案二是电脑VGA接口输出模拟RGB信号经过视频AD转换成数字信号,FPGA对图像原点和大小根据需要进行改变。两种方案中DSP的作用都是对传输图像数据进行H.264压缩后使用以太网传输。其中数据压缩部分调用DSP内嵌硬件模块进行H.264压缩。DSP内嵌的ARM处理器将数据打包后通过以太网传输,在截取图像大小为576×384×30 f/s时,采用2 Mbit/s码率能获得比较清晰的图像。最后,接收端使用H.264解码软件实时播放传输过来的压缩图像。

图1 系统结构框图

2 系统详细设计

2.1 上位机截屏

上位机主要实现方案切换和方案一中的计算机截屏。方案切换是通过上位机发送控制信号传递给FPGA实现的。方案一中的截屏数据是计算机显存中的数据,每个像素点是以R、G、B数据格式存储的,每个色彩通道为8 bit。因此一帧图像以原始数据大小传输给FPGA,传输图像数据较大。获取屏幕图像的上位机软件界面采用VS2003或 VS2010 编写[2],经实测,在 Visual Studio 2010平台上用C#编写截图类函数,程序中的截屏部分调用dotnet4.0中执行效率较高的工具集,比VS2003效率提高30%以上。为了提高资源利用率,程序采用线程截图的方式进行主机屏幕截屏。同时,还可以进行单帧截屏图像的保存,保存为BMP文件格式。计算机的PCI驱动由Windriver软件生成。软件操作简便、人机交互良好,界面如图2所示。

图2 上位机操作界面(截图)

2.2 FPGA数据处理

FPGA主要实现PCI总线接口、SDRAM数据存储、I2C总线配置芯片、方案一图像数据格式转换功能和方案二图像大小裁剪的功能。FPGA选用ALTERA公司生产的EP3C55F484。有327个I/O用户引脚和55856 个逻辑单元。片上具有260个256×36 bit的RAM存储块。FPGA外接双口DPRAM缓存数据,选用IDT70T3339芯片,存储容量为512 kbyte×18 bit。视频DA选用ADV7123是一款单芯片、3 通道、10 bit高速数模转换器[3]。

与上位机的数据通信采用CPCI接口。CPCI是PICMG提出的一种工业接口标准,采用PCI总线技术,在此基础上改善了机械结构,支持热插拔,可靠性高。本系统PCI接口是在FPGA中利用Altera公司提供的PCI IP核来完成。PCI Compiler提供了使用Altera器件实现PCI接口设计的完全解决方案。PCI IP核的功能即是将复杂的PCI总线转换为相对简单易操作的PCI本地总线,它从PCI总线侧获得传输命令和读写数据的地址后,一方面对这个操作命令做出反应,将其传达给LOCAL总线,另一方面将PCI总线传送过来的数据地址映射为LOCAL总线可识别的地址。当LOCAL总线准备好后,PCI IP核会收到LOCAL侧做出的响应信号。然后根据读/写命令的不同执行相应的时序。在上电启动时它为FPGA申请空间,操作FPGA时它将PC机给出的地址转换为FPGA可以识别的地址[4]。本系统通过PCI接口与PC机传输图像数据,由上位机应用程序控制系统工作,FPGA每帧中断通知上位机截取图像,故系统工作于32 bit主/从模式。PCI的BAR0预留2 Mbyte的存储空间,基地址 BAR1预留256 byte I/O空间。由于PCI总线上地址线和数据线复用,所以还需要地址/数据控制模块来实现对地址数据传输的控制。PCI接口本地端逻辑设计应当完成地址译码、命令译码以及中断控制功能。PCI接口逻辑设计中,调用Altera在SOPC Builder中提供的PCI IP核,与自行设计的译码逻辑相连接,完成PCI总线功能[5]。上位机截屏的图像数据存放在计算机内存中。单周期的访问速度太慢,不适合做批量数据传输。因此PCI内部设置了专门用于批量传送的DMA控制器将数据传送给FPGA。通过NOIS中的程序向DMA控制器配置传输首址、传输长度和使能DMA位等参数启动。

本系统设计最高支持1024 ×1024 大小图像截屏传输,从上位机获取的一帧图像的原始数据量是1024 ×1024 ×3=3 Mbyte,数据量大。采用SDRAM作为存储器外设。在FPGA内部产生SDRAM控制器来完成SDRAM的初始化、自动定时刷新、存储单元地址管理,读写模式配置等功能。设计中调用Altera在SOPC Builder中提供的基于Avalon总线的SDRAM控制器核来实现该功能。芯片选用MT48LC2M32B,容量为2 Mbyte×32 bit。

本系统中VGA输出视频信号采用XGA(1024 ×768)视频格式,60 f/s,选用 TI公司的视频 ADC芯片TVP70025I完成该高清模拟视频的模数转换,采样精度及方式选取为8 byte,4∶2∶2(Y∶Cb∶Cr) 采样。TVP70025I输出数字化视频分量(Y、Cb和Cr)、数据时钟(DATACLK)、场同步(VSOUT)和行同步(HSOUT)信号给FPGA。FPGA通过I2C总线[6]对TVP70025I内部寄存器进行初始化设置,并启动模数转换过程。

方案一中上位机传输到FPGA的图像数据处理过程:FPGA中断接收上位机截屏数据缓存SDRAM中,然后将RGB格式转换成YUV422格式。首先转换成YUV444格式,产生写片外双口的写使能、写地址,以YUV422格式存储图像数据,最后以30 f/s读出传输给DSP。按显示时序读取片外双口中数据,并产生VGA显示时序。经过视频DA芯片后实时显示截屏图像。

方案二中上位机VGA口输出给视频AD芯片的图像是XGA格式,大小固定,帧频为60 Hz。需要在FPGA内部裁剪成需要的以图像上任意坐标为原点的,大小可改变的图像。并通过DPRAM缓存数据改变传输速度。通过上位机PCI接口可以获得上位机设定的图像原点坐标值。

2.3 数据压缩

FPGA传输给DSP的是一帧的YUV422格式的图像数据,使用以太网传输,短时间内处理如此大的数据量对存储容量、信道的带宽和数据的处理速度来说都是很大的困难,因此有必要在存储和传输图像数据时进行压缩。H.264在同样的视频清晰度下,编码效率比MPEG-4提高50%,压缩比更高,而且提供友好的网络接口,有利于在网络中的视频传输[7]。

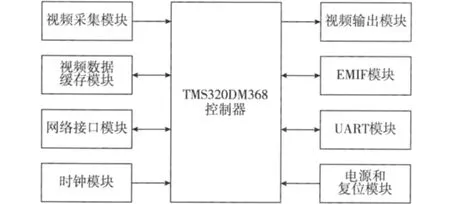

TI推出的DM368集成了ARM处理器,应用程序的开发需要搭建交叉编译环境,需要宿主机和目标机,宿主机需要安装TFTP服务器为完成目标机的主要映像文件的下载工作。宿主机还需要配置NFS文件系统,宿主机编译的文件可以通过NFS利用网络直接加载到目标机的RAM中运行。图3是DM368的硬件设计方案框图。

图3 DM368的硬件设计方案框图

DM368有一套完整的基于LINUX操作系统的解决方案。系统的软件框架分为3个应用层:应用层,信号处理层和I/O层。信号处理层负责硬件H.264编码,算法采用XDM封装,ARM下的应用程序可以调用符合XDM应用程序接口的API函数[8]。

在LINUX系统下实现H.264压缩视频编码的应用程序需要多个线程来对多个外围设备进行操作。分为thread线程、video线程、显示线程、捕获线程和写线程。在video线程中,video线程从capture线程接收数据,调用硬件编码器对其进行编码,将编码后的数据送到write线程,write线程将数据写到Linux的文件系统中。使用专用的I/O和capture线程来最大限度地发挥ARM和DSP核的作用。

本系统的实时视频传输功能是采用RTP协议来实现的,实时传输协议(Real-time Transport Protocol,RTP)是用于互联网上针对多媒体数据流传输的一种协议[9]。video线程将视频流进行H.264编码,编码后的视频流即为一个NALU单元。RTP封包按照RFC3984标准规定的格式将NALU单元封装为标准的RTP包,然后再发送给客户端,这些功能是通过RTP thread完成。

3 实验结果与分析

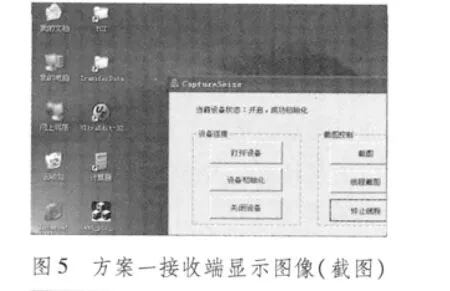

FPGA程序使用QUARTUSⅡ软件,Verilog语言编写,并使用MODELSIM软件仿真。DSP程序使用CCS3.3软件,C语言编写。本系统两种方案均成功截取屏幕图像,并在解码端显示。图4是远程屏幕传输系统板卡6U CPCI版型实物图。在上位机开始线程截图时同时记截图的帧数N,终止截屏后,弹出对话框显示从开始截屏到结束截屏的时间T。通过N/T可以计算出发送的帧频,测试在截取576×384大小计算机屏幕时,经反复测试,达到30 f/s的传输速度。在截取1024 ×1024 大小计算机屏幕时,传输速度是15 f/s。可见当截取屏幕越大时,截屏速度会相应的降低,传输时间也会变长。通过网线连接发送板卡和接收端,在接收端的主机上使用H.264解码软件显示。使用MATLAB软件计算方案一上位机截取原始图像和接收端解压缩后图像(图5所示)的PSNR值为64.0291 。方案二接收端解压缩后图像(图6所示)的PSNR值为40.1564 。方案一接收到的图像质量比方案二的效果更好一些。

方案一是直接截取现存中的数字图形缺点是要占用25%左右的CPU资源(对于双核CPU)。另一种方案是对上位机的VGA信号进行AD变换,然后截取AD变换之后的图像。这种方案的优点是不占用CPU资源,缺点是截取图像AD转换图像时,像素点数值会产生一定的误差,图像会比第一种模糊。是由于截取图像是从VGA口经过AD转换,在压缩图像前就产生了一定的误差。但从直观视觉上,两种方案都可以达到较好的显示效果,可长时间稳定工作。

4 小结

本文设计并实现了一种基于DSP+FPGA的远程屏幕传输系统,采用两种方案实现计算机屏幕截屏,实际应用时可根据需要通过上位机选择方案截屏图像传输,使用灵活。调用DM368硬件编码模块,实现H.264压缩格式的实时视频压缩编码,克服远程屏幕传输系统中普遍存在的实时性差、稳定性差的缺点。同时,截取屏幕原点和大小均可改变,具有灵活性。

[1]董祖雄,谢捷生.远程屏幕传输及其数据压缩的实现方案[J].微型机与应用,2001,10(9):55-56.

[2]吴栋淦.两种屏幕图像获取方案的比较[J].机电技术,2007,9(3):9-11.

[3]Altera Corporation.EP2S90 data sheet[EB/OL].[2012 -06 -06].http://wenku.baidu.com/view/3d78d7eab8f67c1cfad6b893.html.

[4]王宏斌.PCI总线IPCORE的FPGA实现[D].西安:西安电子科技大学,2006.

[5]秦珍.基于IP核的PCI卡在图像采集系统中的应用[D].西安:西安电子科技大学,2010.

[6]戴立新,王泽勇,王黎,等.I2C总线的接口及应用[J].现代电子技术,2009(2):132-134.

[7]刘卫亮.基于H.264的无线视频传输平台的设计与硬件实现[D].西安:西安电子科技大学,2010.

[8]彭启宗.达芬奇技术[M].北京:电子工业出版社,2008.

[9]夏朋浩.非制冷热成像信号处理与压缩技术研究[D].南京:南京理工大学,2012.