GP-SDR软件无线电信号处理平台的硬件设计

2013-06-29罗清,赵利

罗 清,赵 利

(桂林电子科技大学信息与通信学院,广西 桂林 541004)

随着通信技术的不断发展,各种编译码算法、调制解调方式不断涌现出来,各种通信服务依靠于不同的标准和支持这一标准的通信设备。这给不同通信体制下的通信接口服务提出了难题,软件无线电(Soft Defined Radios)的提出是解决这一问题的有效途径之一。软件无线电的中心思想是构建一个开放性、模块化的、标准的、可重构的通用硬件平台,将一系列的通信功能诸如工作频段、调制解调类型、数据格式、加解密算法等通过软件加载来实现的开放式体系结构[1]。

软件无线电系统设计可采用DSP、FPGA、ASIC的方法实现,其中ASIC又分为多片ASIC和可编程ASIC。采用DSP成本高、系统功耗大、在高速信号处理场合,实时性不够好,但可升级性高,擅长算法复杂的信号处理;采用FPGA成本低、灵活性高、功耗低,实时性好,但对复杂算法的数字信号处理能力相对欠缺;多片ASIC不仅成本高,而且系统没有可升级性,可编程ASIC虽然成本较低,但是可升级性弱。基于此,本文设计了一种GP-SDR软件无线电数字信号处理平台,此架构的软件无线电信号处理平台能够兼顾成本、功耗、灵活性以及可升级性,是一种很好的软件无线电解决方案。

1 方案设计

1.1 总体架构设计

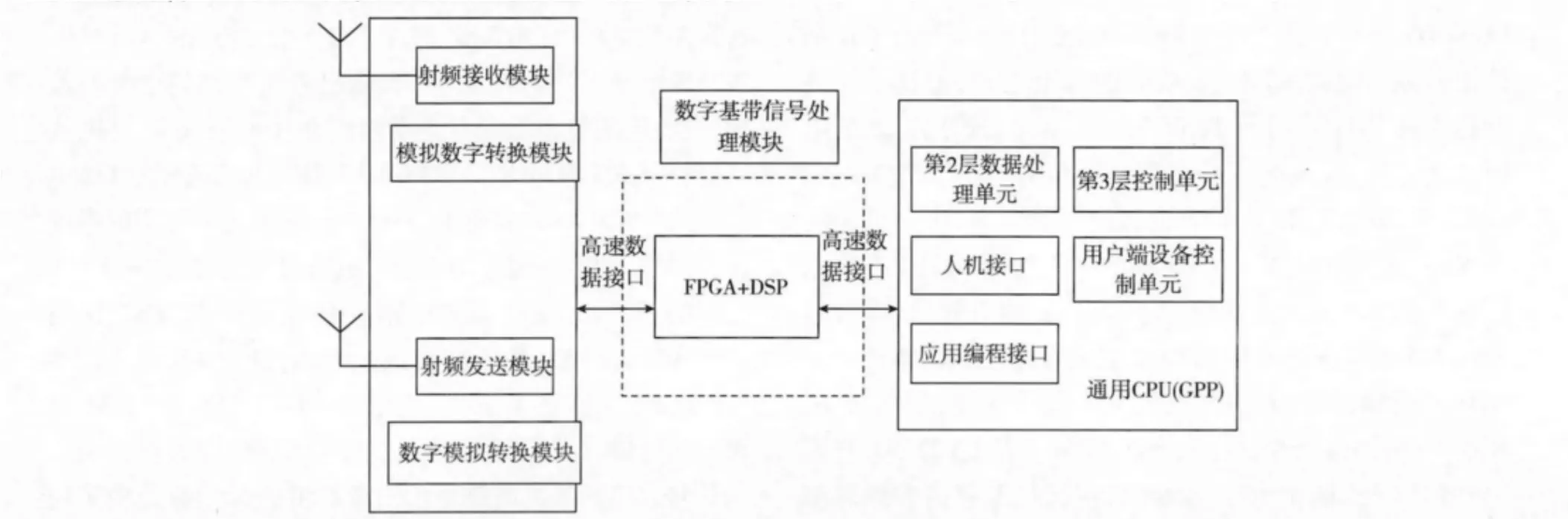

GP-SDR的软件无线电信号处理平台的硬件结构如图1所示。

图1 GP-SDR的软件无线电信号处理平台硬件结构框图

基于此架构的软件无线电信号处理平台具有如下优点:

1)增强了系统的灵活性,节约了成本,协议栈结构易于升级,更加接近理想的软件无线电系统;系统的信号处理能力得到很大的提高,各个部分能充分发挥各自的优势,使得系统的资源分配更加合理,优化了系统结构。

2)协议栈全部基于GPP编程实现,代替传统系统中由专用套片实现的方法,开发周期短,成本低。

3)GPP多核间灵活的多线程调度,单指令多集的应用,充分发挥多核CPU并行处理的能力;高吞吐量的通用硬件接口PCI-E或USB3.0/2.0接口,保证了硬件与软件之间数据的交互。

1.2 数字信号处理平台方案设计

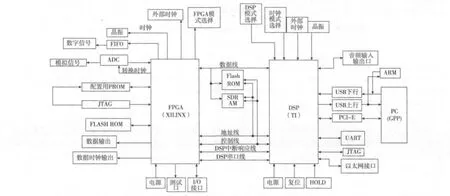

DSP+FPGA构成的数字硬件系统最大的优点是结构灵活,具有较强的通用性,适合模块化设计,从而能够提高算法效率;同时开发周期短,系统易于维护与升级,适合高速实时信号处理。GP-SDR软件无线电信号处理平台硬件结构如图2所示。

图2 GP-SDR的软件无线电信号处理平台硬件结构框图

DSP的外围电路包括电源电路、时钟电路、复位电路、JTAG调试电路、外部存储器总线接口电路,以及各种外部接口,包括音频输入输出接口、以太网接口、UATR接口以及USB接口;FPGA的外围电路包括电源电路、时钟电路、存储器电路、复位电路、调试电路以及EMIF接口。

DSP采用的是TI公司的32 bit浮点处理器TMS320C6713[2],它的最高主频可以达到 225 MHz,且可以同时执行8条指令,每秒可以处理1.8×109条浮点运算指令,是一款高性能、多功能的DSP芯片;内核电压供电芯片采用TI公司的TPS75801,它是一款输出可调的电压转换芯片,输入电压最高5.5 V,最低2.8 V,输出电压最高5 V,最低1.22 V,DSP 内核电压为1.26 V,可以满足要求;IO电压供电芯片采用AMS1117,设计中采用5 V电压输入,3.3 V电压输出的固定电压输出方式;复位芯片采用MAXIM公司的MAX708T,芯片能够在输入电压低于3.08 V时输出复位信号,保证DSP能工作在正常的供电环境中;时钟输入来源于外部时钟发生器CY22150,它是CYPRESS公司生产的一款抗时钟抖动、偏移的在线可编程时钟发生器,能够输出高精度的时钟信号。JTAG接口是基于IEEE1149.1标准的一种边界扫描测试方式。

FPGA采用的是XILINX公司的Spartan-3A DSP FPGA 系列的XC3SD3400A[3],集成系统门多达3.4 ×106个,内部更是有多达126个DSP48A Slice、8个DCM,资源非常丰富。设计中使用了独立于DSP的电源系统,包含了2.5 V,1.8 V,3.3 V 三种 IO 电压,其中 1.8 V 的 IO 电压是为与DDR2接口所需要的;输入电压为+5 V,通过电压转换模块PTH05050WAZ获得3.3 V、2.5 V的IO电压,PTH05050WAZ是TI公司一款输出电压可调的电源转换模块,通过调节调压电阻获得输出在0.8~3.6 V之间的任何电压值;通过PTH04000WAZ获得1.2 V的内核电压,PTH04000WAZ也是TI公司一款输出电压可调的电源转换模块,同样的通过调节调压电阻可以获得0.9~3.6 V之间的任何电压值。复位电路采用TI公司的TPS3307与TPS3808,TPS3307用于监控内核电压,TPS3308用于监控1.8 V,2.5 V,3.3 V 三个 IO 电压。CY22150 为 FPGA 提供输入时钟,通过FPGA内部的DCM分频倍频获得需要的信号,AD转换的时钟也由CY22150提供。设计中采用了2片微软公司的DDR2芯片MT47H64M16HR组成128 Mbyte×32 bit的大容量存储系统用于快速存取整个信号处理过程当中产生的大量数据。

FPGA通过DSP的EMIF接口与DSP相连,接口信号包括32 bit数据总线 ED[0∶31]、地址总线[2∶21]、部分握手控制信号和一些中断控制引脚。

GPP-CPU部分主要是一些高层协议栈的设计,是整个系统重要的设计环节之一,经过DSP+FPGA处理的基带数据通过高速数据接口USB3.0传入GPP做后续的处理,整个信号处理流程当中,DSP+FPGA只做数字信号的基带处理,GPP负责完成后续的信号处理。

2 关键模块设计要点

2.1 DSP、FPGA 配置模块设计

为储存DSP和FPGA自启动需要的配置信息,各自用1片Flash来存储这些信息是一种比较常见的处理方式。为节省成本,系统设计中,DSP与FPGA共用一片配置Flash,由DSP控制FPGA的配置过程[4]。采用的是AMD公司的AM29F160D,容量为1 Mbyte×16,DSP加载模式设置为EMIF加载启动,这种自加载方式从CE1空间的地址处拷贝1 kbyte的数据,然后系统从地址0处开始执行。FPGA加载模式设置为从并模式,由DSP通过EMIF接口将配置数据送至FPGA的配置锁存器对FPGA进行配置。

2.2 时钟模块设计

通过DSP内部的分频倍频器产生的时钟一般都有抖动及衰落,为给DSP提供高质量的时钟信号,决定采用CY22150为DSP提供时钟输入以及EMIF工作时钟。CY22150是CYPRESS公司一款在线可编程的时钟发生器,可以产生6个低衰落、低抖动的高质量时钟输出,最高输出频率时钟为200 MHz,设计中,DSP的输入时钟为25 MHz,EMIF工作时钟为100 MHz。同理,FPGA的输入时钟也由CY22150提供,再经过FPGA内部DCM分频倍频得到其他需要的时钟信号。

AD采样过程中,时钟的抖动会引入相位噪声,时钟源产生的抖动会使ADC的内部电路错误地触发采样时间,结果造成模拟输入信号在幅度上的误采样,从而恶化ADC的信噪比,故而AD采样需要一个低抖动的高质量时钟,CY22150为AD转换提供时钟。

2.3 USB3.0 接口设计

欲使经过DSP+FPGA处理的大量基带数据得到实时的处理,则必须保证与GPP接口的高速性与稳定性,USB3.0就是一个很好的选择。USB3.0的数据带宽是USB2.0的10倍,达到5 Gbit/s,而且具有低功耗、可以通过线缆提供更大的功率等USB2.0所没有的优点。

2.4 GPP-CPU 软件协议栈设计

GPP-CPU是整个系统设计的重点环节之一,主要实现各个功能单元及相关接口的设计,功能单元包括数据处理单元、控制单元、用户端设备控制单元,接口包括人机交互接口、应用编程接口;数据处理单元的作用是负责处理经过DSP及FPGA处理的数字信号的后续信号处理工作,控制单元的作用是负责整个系统信号处理过程中的控制及系统资源的分配工作,用户端设备控制单元的作用是维护及管理用户端设备,人机接口的作用是为用户管理及维护系统设备和资源提供一个可视性高、易操作的接入接口。GPP-CPU需要处理如此多复杂的数据及事务无疑给GPP-CPU的效率提出了很大的考验,基于通用CPU的机制保证了GPP-CPU的效率,这些机制主要有:

1)多线程的编程保证了多项任务在多个CPU核中的并行执行,充分发挥了多核CPU的优势;

2)基于通用操作系统,使用高效率的数据零拷贝技术,大幅度提高了数据在协议栈各层之间的拷贝吞吐量;

3)单指令多操作(SIMD)指令集充分发挥了CPU的数字信号处理能力。

3 设计难点

GP-SDR软件无线电信号处理平台有很多优点:1)平台配置灵活,有多种配置方式;2)基于GPP-CPU上位机的开发更易于修改与移植;3)整个平台的架构更接近理想的软件无线电系统。系统实现起来有一定难度,首先,基于DSP+FPGA通用硬件模块的硬件设计与调试是难点之一,硬件设计包括原理图设计、PCB布局、PCB布线[5-6]。对于原理图的设计来说,由于设计当中重要元器件的管脚数目比较多,TMS320C6713有272个管脚,XC3SD3400A有676个管脚,而且芯片之间又有通信,连接也比较复杂,因此采用了平坦式的原理图结构,按核心元件的功能划分为电源模块、存储器模块、DSP模块、FPGA模块4大模块,AD/DA中频板作为一个单独的子板进行设计。在PCB布局方面采用按功能模块分区布局的策略。PCB布线是整个硬件制作过程当中非常重要的一环,直接关系到电路板性能的优劣。设计中用到的DSP及FPGA都是BGA封装,而且管脚数很多,因此采用了6层板的设计。布线过程当中应把握几个大原则:1)模拟与数字部分尽量分开,不要跨区域布线;2)不同层的布线尽量垂直,减少层间信号耦合;3)差分线尽量靠近等长布线,以便信号同时到达;4)由于电源线及底线要承受较大的电流,在空间允许的情况下尽量加大它们的线宽。接下来是硬件平台的调试,总的原则是按功能模块划分对每个模块单独进行调试,最后是各个模块联合调试。其次,DSP+FPGA系统的软件设计以及驱动的开发也是设计的难点之一;最后,高层协议栈在GPP-CPU在上的实现以及与DSP+FPGA系统的通用高速硬件接口的设计与开发也是设计当中比较困难的部分。

4 仿真验证

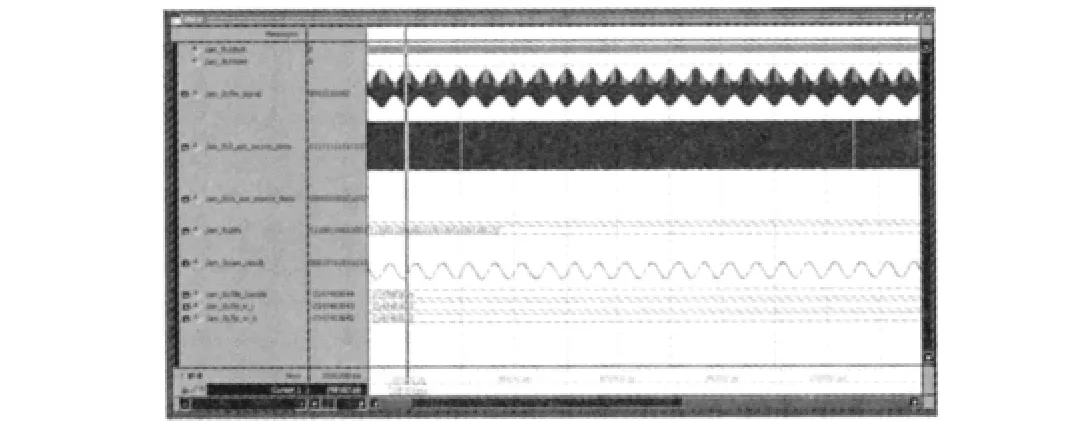

XCS3D3400A内部嵌入有126个DSP48 Slice,为验证方便,这里用FPGA来实现DSP的功能。结合GNU Radio对系统进行仿真。GNU是一种最小程度的结合硬件(通常是USRP),用软件来定义无线电波的发送和接收模式的一种软件体系。结合GNU Radio的USRP(Universal Soft Radio Peripheral)对AM信号的解调进行了仿真验证,用MODELSIM观看仿真结果,仿真结果如图3所示。

图3 AM信号的解调(截图)

由图3可知,系统可正确实现AM信号的解调,这说明系统方案是可行及合理的。

5 总结

GP-SDR软件无线电信号处理平台结构合理,优势明显,是一种较好的软件无线电信号处理解决方案。

[1]杨小牛,楼才义,徐建良.软件无线电原理及其应用[M].北京:电子工业出版社,2001.

[2]TMS320C6713 data sheet[EB/OL].[2012-08-02].http://wenku.baidu.com/view/6093b70f6c85ec3a87c2c5a1.html.

[3]Spartan-3A DSP FPGA family data sheet[EB/OL].[2012-08-02].http://www.docin.com/p-465412822.html.

[4]李飞飞,苏延川,王鹏.基于DSP的FPGA配置方法研究与实现[J].现代电子技术,2011(24):60-62.

[5]白武奇.基于软件无线电的的硬件设计与调试[D].西安:西安电子科技大学,2008.

[6]钮心忻,杨义先.软件无线电技术与应用[M].北京:北京邮电出版社,2001.