一种X波段五位数字移相器的研究与设计

2013-06-08安士全郭本青

安士全,郭本青

(中国电子科技集团公司第三十八研究所,合肥 230088)

0 引言

移相器是雷达、通信设备中的一种关键器件,用于实现对传输信号相位的控制。移相器的相移精度和响应速度等指标的好坏直接影响到系统波束在空中定位的准确性和波束主瓣对旁瓣的抑制度高低,影响系统指标。有源相控阵雷达天线一般由成百上千个相同的T/R组件组成,移相器的数量巨大。因此,对移相器的要求除了要满足技术指标外,其成本考虑也是一个重要因素。

利用GaAs HJ-FET 器件作为开关元件,本文设计了一种低成本的X波段五位数字移相器。利用ADS软件首先对5个移相单元分别进行设计,后将5个移相单元级联进行整体仿真优化,并进行了加工和测试。测试表明,移相器各性能参数满足设计指标。

1 移相器的工作原理及电路设计

数字移相器一般由微波开关、传输线或电抗元件构成。通过改变微波开关的控制偏压,移相器电路呈现两种不同状态,信号在开关两种不同状态而产生相移。图1 是移相器的一般工作原理,输入和输出端一般是50 Ω的匹配线,控制端的不同输入,移相器上会出现两个不同的状态。在这两种状态下,信号会存在两个不同的传输相位Ø1和Ø2,则相移为△Ø=Ø1-Ø2。

图1 移相器的工作原理

五位数字移相器由5个移相单元级联而成。每个移相单元是一个独立的二态移相器,各有2个状态。在各自的开关控制下,通过控制各个移相器的工作状态实现每一位的移相功能,对5个独立的移相位进行不同状态的组合,可以使得移相器系统在0°~360°范围内,以11.25°为步进,实现25=32个相移状态,如图2所示。

图2 五位数字移相器级联示意图

PIN 二极管是常用的微波控制元件,具有插损小、反应时间短、体积重量小、对温度变化稳定性好等优点。FET 器件通过栅极电压控制漏源间的导通和截止,也可以作为开关使用,且其成本更低,功耗更小。本文采用NEC 公司的FET 器件NE3210S01 作为开关控制元件,整个移相器由5个移相单元串联而成。

X波段移相器的设计,首先对每一移相位进行单独的仿真,建立电路的仿真拓扑结构图,然后将5 位级联起来仿真。设计中采用Rogers 公司的RO4003 型基板,介电常数3.38,基片厚度0.508 mm,导体厚度0.035 mm,金属电导率88×107。NE3210S01 器件导通时栅极电压0 V,截止时栅极电压-1.2 V,设计采用Agilent 公司的ADS 仿真软件仿真,线性分析采用厂家提供的HJ-FET的S 参数。

1.1 加载线移相器设计

在实现小相移时通常采用加载线型移相器形式,具有结构简单、插入损耗小、驻波比低、移相精度高等特点。因此,11.25°、22.5°移相位采用加载线型电路结构。图3为改进型加载线移相器的电路结构。改进型的开关线移相器利用加载线移相器原理,在开关线移相器的一条支路上并联电纳,使得2 条支路上的传输相位曲线斜率相接近,从而减小2 条支路的固有相移偏差,具有更高的相移精度。

图3 改进型加载线移相器电路结构

以22.5°为例,在ADS中建立移相单元拓扑结构如图4所示。将移相器的相移量、输入输出驻波比以及开关两态的插损设为优化目标。优化过程中,一般先选用随机法以便电路快速达到较好性能,当优化到一定程度后,再采用梯度法,进一步优化电路性能。22.5°移相单元的仿真模型及结果如图4所示,可以看出移相误差在0.5°以内。

图4 22.5°位移相电路建模及仿真结果

1.2 反射型移相器设计

对于45°、90°和180°移相位,由于移相度数较大,采用反射型移相结构。反射型移相器移相精度高,但结构复杂,尺寸较大,适合移相度数较大的情况。图5是反射型移相器的电路结构。

图5 反射型移相器原理图

反射型移相器前端是一个3 dB 正交混合网络,从端口1 输入的功率被等分耦合到端口2和端口3,混合网络后面接的是一段微带线,用于匹配端口2、3和终端。然后通过开关接入反射终端Γ1和Γ2,反射端口1的输入功率反射到端口4。端口4的输出电压波为

其中θ 是端口1 到端口4的传输总长度,状态2时

由两式得

则移相器的移相度数:

以45°为例,建立ADS 拓扑结构如图5所示。通过对移相、插损、回波损耗等参数设为目标进行优化,最终的仿真结果如图6所示。

图6 45°位移相电路建模及仿真结果

1.3 整体电路设计

确定每一移相单元电路结构后,根据具体指标要求进行整体分析和仿真,将5个移相单元级联起来,对5个移相状态分别进行仿真。为了使32个相位状态下所实现的相移量尽可能接近标准相移值且等间隔,需要对各部分的优化尺寸再进行微小调整。同时,为了较好地控制各状态下的插入损耗起伏,对级联起来的各单元移相电路之间的微带传输线尺寸进行多次取值分析,以求减小各级之间的驻波干扰。

最终对五位移相器整体进行仿真。结果显示,在12~12.5 GHz 频率范围内RMS 小于3°,系统插入损耗小于2.8 dB,插入损耗最大变化小于0.6 dB,输入驻波比小于1.4,仿真结果符合设计指标。

各位移相器的驻波特性相当重要。当移相器的驻波较大时,各移相单元之间由于来回反射引起相位不确定而产生误差。所以,为避免产生较大的相位误差以及减小回波损耗,各移相单元在满足相位精度和插入损耗指标的前提下,输入输出驻波比要尽可能小。

2 移相器的测试

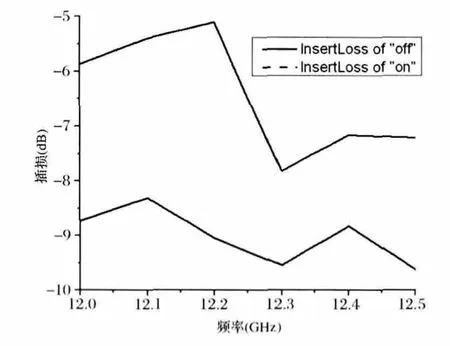

根据上述设计,加工的X波段五位数字移相器电路实物图如图7所示。利用矢量网络分析仪对移相器进行了测试。在测试过程中,FET 器件的控制电压设置为-2 V。插损和相位的测试结果分别如图8、9所示。可以看出,在设计的12~12.5 GHz 频段内FET器件全导通和全截止两种状态下(移相为0°和348.75°时)的插损值在7.5 ±2 dB 范围内,各基本移相位及移相器整体的反射系数均优于-12 dB,如图10所示。移相精度90°位误差最大,为±3.2 °,180°位最理想,最大误差±2.1°,其余移相位都在±2°以内,其中11.25°移相位的最大误差小于±1.2°,总体来说与仿真结果符合良好。如果对90°位进行重新优化设计可以将移相器的精度进一步提高,更好地使用。测试结果中插损的指标与仿真结果差别比较大,主要有如下几方面原因:(1)测试用的输入输出连接器带来一定插损;(2)微带板材及加工工艺带来的传输损耗;(3)微带板与盒体间采用螺钉固定方式,接地不好,插损较大;(4)测试本身带来一定误差。因此,若要改善插损指标,可以在微带板板材、加工工艺、电装等方面着手,采用传输损耗小的板材,且微带线表面镀金,微带板的安装采用焊接方式等。

图7 X波段五位数字移相器实物图

图8 移相器插损测试曲线

图9 移相器移相精度测试曲线

图10 5个基本移相位及整体移相器的驻波测试曲线

3 结束语

本文利用FET 器件作为开关元件,运用ADS 仿真软件,采用先独立后整体的设计思路,对X波段移相器进行了仿真设计和优化,并进行了实际电路加工和测试,测试结果基本达到预期目标。因此,在对移相器的尺寸要求不高的场合可以替代MMIC 移相器,而整个移相器的硬件成本仅为MMIC 移相器价格的几分之一,可以有效降低移相器的成本,具有一定的经济意义。

[1]清华大学《微带电路》编写组.微带电路[M].北京:人民邮电出版社,1976.

[2]Bahl I J ,Bhartia P.微波固态电路设计[M].顾墨琳,译.南京:SSS 丛书编辑部,1991.

[3]CAMPBELL C F,BROWN S A.A Compact 5-bit Phase Shifter MMIC for K-band Satellite Communication Systems[J].IEEE Trans.on Microwave Theory and Techniques,2000,48 (12 ):2652-2656.

[4]吴斌.S波段五位数字移相器研究[D].成都:电子科技大学,2006.

[5]万建岗,高玉良,许明.基于ADS 仿真的S波段五位数字移相器设计[J].空军雷达学院学报,2008,22(3).