基于FPGA的交通灯控制系统设计

2013-06-07刘艳昌王廷雨

刘艳昌,王廷雨

(河南科技学院,河南新乡453003)

基于FPGA的交通灯控制系统设计

刘艳昌,王廷雨

(河南科技学院,河南新乡453003)

针对传统利用单片机或PLC等控制芯片设计交通灯控制系统存在控制精度不高、外围电路复杂、程序修改不灵活、成本较高的问题,采用Verilog HDL语言,以QuartusII软件为系统设计平台,对各功能模块进行设计.在原理图文件中添加各功能模块元件符号,然后通过连线组合各底层模块来实现顶层模块设计.系统具有参数修改灵活、外围电路少、控制精度高、可靠性强、成本低等优点.通过软件进行仿真,并在ASK2CB开发板上下载模拟.结果表明:控制系统工作正常,满足设计要求.

FPGA;交通灯控制系统;Quartus II;Verilog HDL

随着社会经济的快速发展和人民生活水平的不断提高,由车辆大幅增加而带来的交通问题日趋严重.因此,交通信号灯作为城市交通监管系统的重要组成部分,对于保证人和车辆安全、快捷、高效通行发挥着巨大作用[1-2].本文利用Verilog编程语言,采用自上而下的模块化编程思想,用软件方式设计硬件,对交通灯控制系统进行设计,整个系统以QuartusII软件为设计平台进行了综合、模拟仿真,并下载到FPGA芯片EP2C8Q208C8上进行硬件调试,验证了系统设置的预定功能,具有一定的实用性.该系统克服了采用PLC、单片机等控制芯片带来的控制方法的修改和调试需要硬件电路支持的困难,从而使系统在开发速度、降低成本、设计灵活、控制精度、功能实现上都得到大幅度提升.

1 系统设计要求

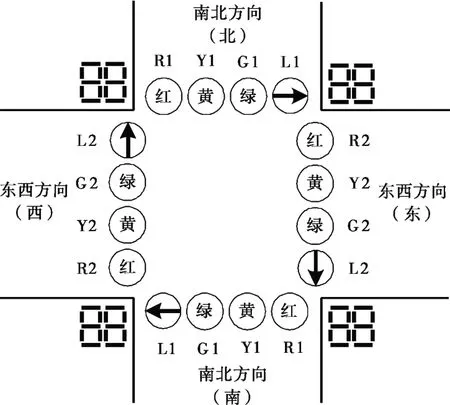

(1)在十字路口的南北和东西两个方向各设一组红黄绿左转弯指示灯,其中南北方向为:红灯(R1)、黄灯(Y1)、直行绿灯(G1)和左转弯绿灯(L1);东西方向为:红灯(R2)、黄灯(Y2)、直行绿灯(G2)和左转弯绿灯(L2).交通灯控制系统如图1所示.

图1 交通灯控制Fig.1 Traffic lights control

(2)由于南北方向为主干道,车流量大,要求南北方向车辆通行时间长于东西方向.

(3)为了使设计系统符合实际交通规则,要求系统指示灯在绿灯、红灯以及左转绿灯之间变化时都要有黄灯作为缓冲.

(4)主副干道各指示灯显示时间可预置和调整,各指示灯点亮持续时间以倒计时形式在两个数码管上显示,且在有应急车通行时,主副干道应具有应急功能,保证应急车辆优先通过.

2 方案确定

2.1 工作规则

对设计要求进行分析可知,两个方向交通灯点亮工作顺序分别为:

南北方向:绿灯→黄灯→左转绿灯→黄灯→红灯;

东西方向:红灯→绿灯→黄灯→左转绿灯→黄灯.

2.2 轮流点亮的状态转换规律

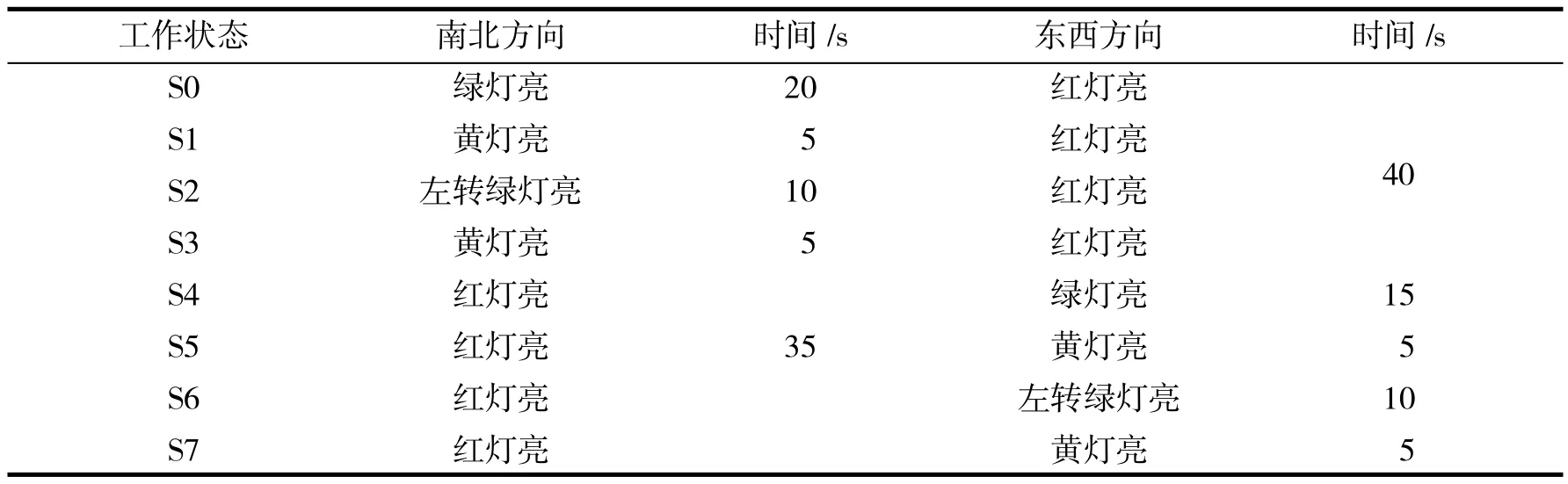

以南北和东西方向的黄灯、绿灯、左转绿灯和红灯点亮持续时间分别为5 s、20 s、10 s、35 s和5 s、15 s、10 s、40 s为例说明交通灯轮流点亮的状态规律[3-4].具体状态转换如表1所示.

表1 交通灯状态转换Tab.1 State conversion of traffic light

从表1可知,要使交通灯管理交通和协调交通的作用有意义,要求南北方向的红灯点亮持续时间等于东西方向绿灯+黄灯+左转绿灯+黄灯所消耗的时间总和.同理,东西方向的红灯点亮持续时间等于南北方向绿灯+黄灯+左转绿灯+黄灯所消耗的时间总和.

2.3 系统总体设计

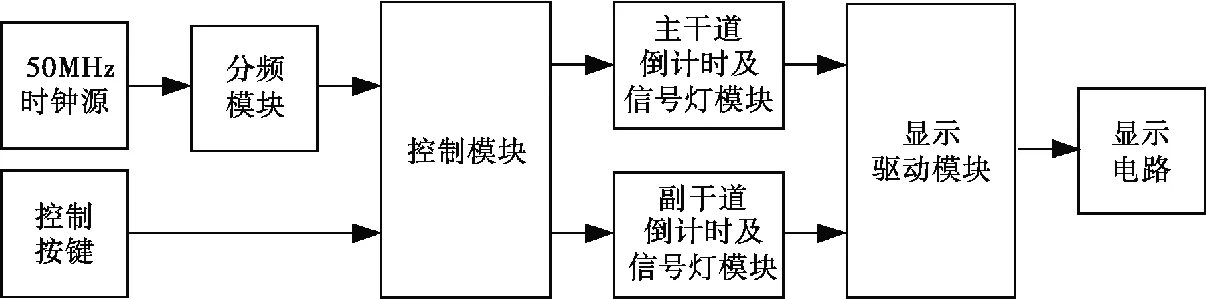

根据交通灯的工作规则[5-6],整个控制系统主要由控制模块、分频模块和显示电路等构成,如图2所示.其中分频模块主要实现将输入的50MHz的基准时钟信号转换为1Hz的激励信号,驱动控制模块工作.控制按键主要实现时间调整、模式控制和复位等功能.控制模块主要控制交通灯按工作顺序自动切换,同时将灯亮剩余时间以倒计时的方式在两位数码管上显示.显示电路包括两部分:一是由7段数码管组成的倒计时显示器;二是由发光二极管代替的交通灯.显示驱动模块主要把两组倒计时模块输出的BCD码转换为7段码,分别送给数码管显示.

图2 系统总体设计方案Fig.2 Design schemeofsystem

显示驱动模块包括译码和动态扫描两部分,将要显示时间和日期的BCD码转化为7段码,在扫描频率下动态循环点亮8位数码管.

3 系统设计与实现

系统设计采用模块化的编程思想,其底层模块主要由分频模块、控制模块、主干道计时模块、副干道计时模块和显示驱动模块组成,具体设计如下.

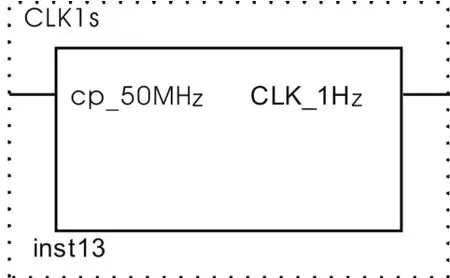

3.1 分频模块设计

分频模块是把输入clk为50MHz的基准信号分频为1Hz的激励信号,供控制模块所需.

在QuartusII软件中选择File→New QuartusIIProject,进入New ProjectWizard界面,输入新建工程位置d:/trafficlight,并把Project名和顶层设计文件名设为同一名trafficlight,然后选择File→New→Verilog HDLFile,在窗口右半部分出来的Verilog.v文件中输入所设计的分频程序,保存文件名fenpin.v,最后把文件fenpin.v置为顶层文件进行编译、功能仿真,并将分频模块生成元件符号以备顶层设计时用[7-8].分频模块电路符号如图3所示.

图3 分频模块电路符号Fig.3 Symbolof frequencymodule circuit

3.2 控制模块设计

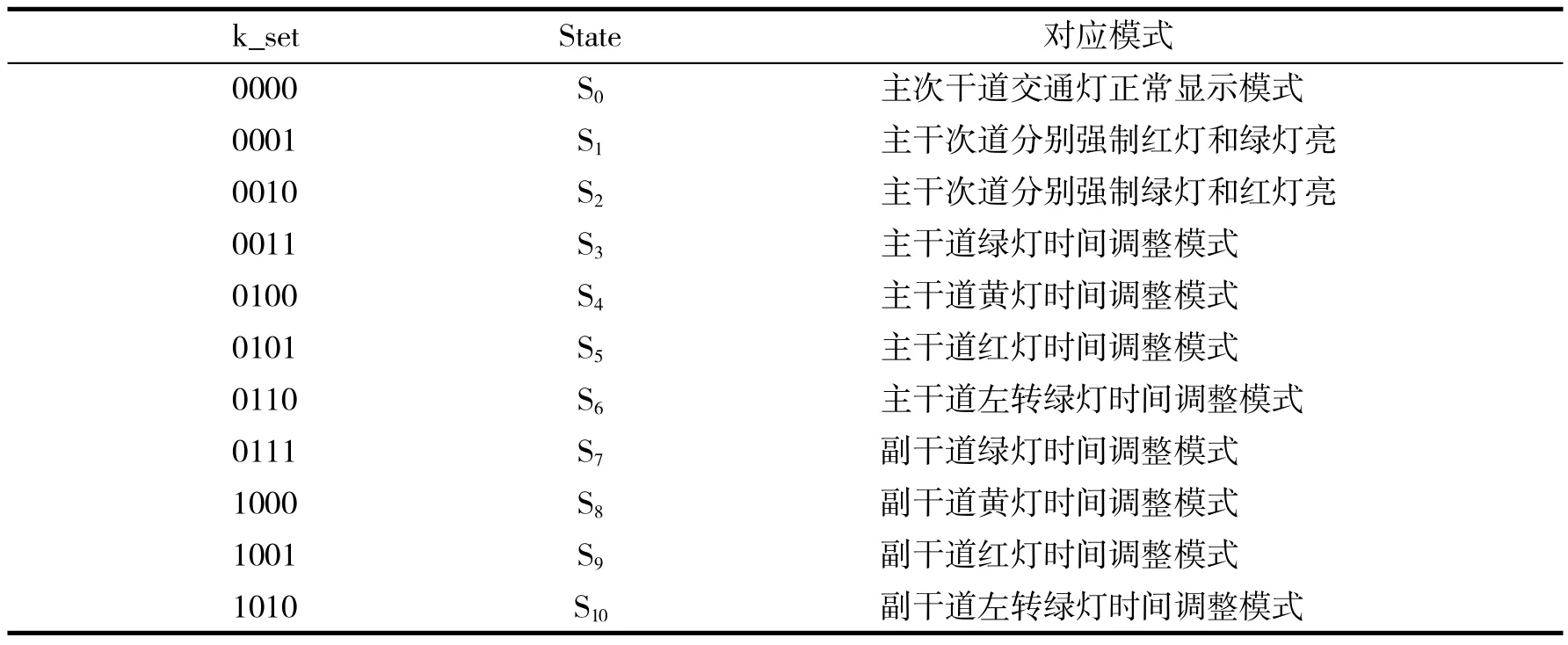

控制模块采用按键产生控制信号,但由于按键有抖动现象,所以需要对按键进行消抖处理,本系统采用软件实现按键消抖.该模块具有控制模式选择、复位、时间预置和调整等功能,设置4按键krest、kset和kup和kdown作为输入,且均为低电平有效.其中输入信号:krest为控制全局复位;kset为控制调整模式状态转换;kup和kdown为加减控制信号键,用来调整倒计时时间.输出信号:state[3..0]为状态控制信号,由kset控制;G1_time[6..0],Y1_time[6..0],R1_time[6..0],L1_time[6..0]分别为主干道各指示灯的计时时间输出,G2_time[6..0],Y2_time[6..0],R2_time[6..0],L2_time[6..0]分别为副干道各指示灯的计时时间输出,通过改变他们的值来控制信号灯的倒计时时间.具体调整模式状态,如表2所示.

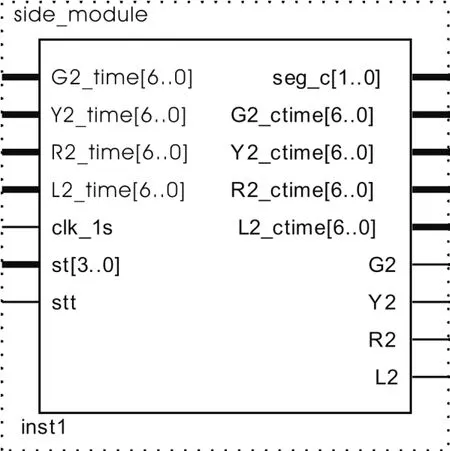

表2 状态控制转化表Tab.2 Conversion ofstate control

新建control_module.v文件,输入相应的控制模块程序,同时进行功能仿真验证设计正确性,并生成元件符号以备顶层设计时用,具体步骤详见分频模块设计.控制模块电路符号如图4所示.

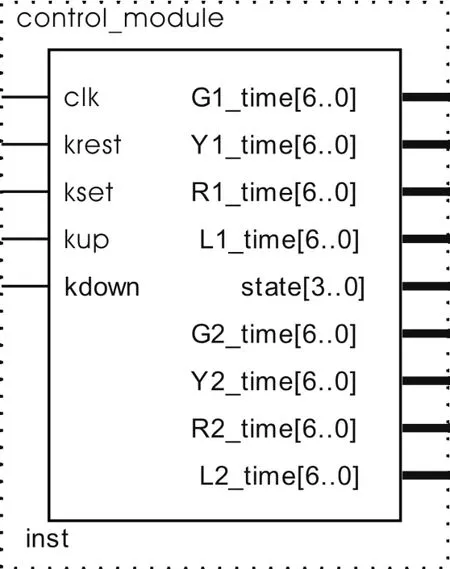

3.3 主干道计时模块设计

该模块主要实现主干道各指示灯状态转换和点亮持续时间,并以倒计时形式在同一位置数码管上显示.其中,输入信号:clk_1s为倒计时提供1 s计数脉冲;G1_time[6..0],Y1_time[6..0], R1_time[6..0]和L1_time[6..0]分别为主干道各指示灯的输入参考值,为本模块计数及产生信号灯转换提供判断依据;stt为复位信号;st为模式控制信号,等同于state[3..0].输出信号:G1_ctime[6.. 0],Y1_ctime[6..0],R1_ctime[6..0]和L1_ctime[6..0]分别为主干道各指示灯的当前倒计时显示数值,送给显示模块显示;seg[1..0]为主干道显示模块提供显示状态条件,0为绿灯,1为黄灯,2为红灯,3为左转绿灯;G1、Y1、R1和L1分别为主干道各指示灯的输入控制信号,且高电平点亮.

新建main_module.v文件,输入相应的主干道计时模块程序,同时进行功能仿真验证设计正确性,并生成元件符号以备顶层设计时用,具体步骤详见分频模块设计.主干道计时模块电路符号如图5所示.

图4 控制模块电路符号Fig.4 Symbolofcontrolmodule circuit

图5 主干道计时模块电路符号Fig.5 Symbolofmain road timingmodule circuit

图6 次干道计时模块电路符号Fig.6 Symbolofside road timingmodule circuit

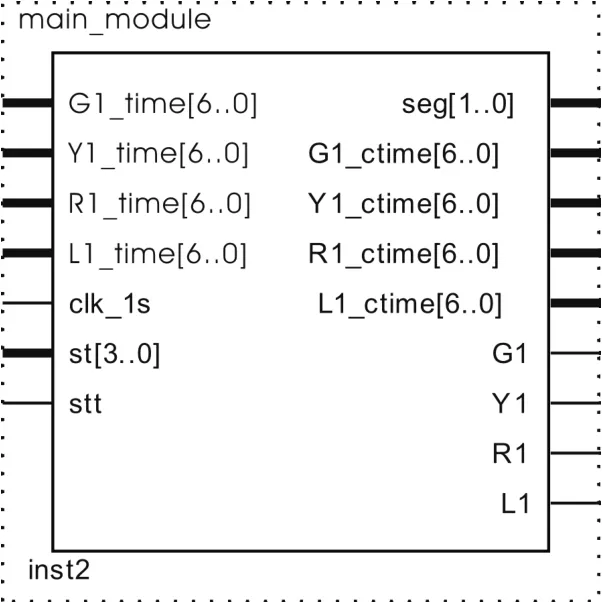

3.4 副干道计时模块设计

副干道计时模块设计与主干道计时模块设计类同,只是受控制模块和主干道影响,交通灯点亮顺序和倒计时时间不同而已,不再详细赘述,其副干道计时模块电路符号如图6所示.

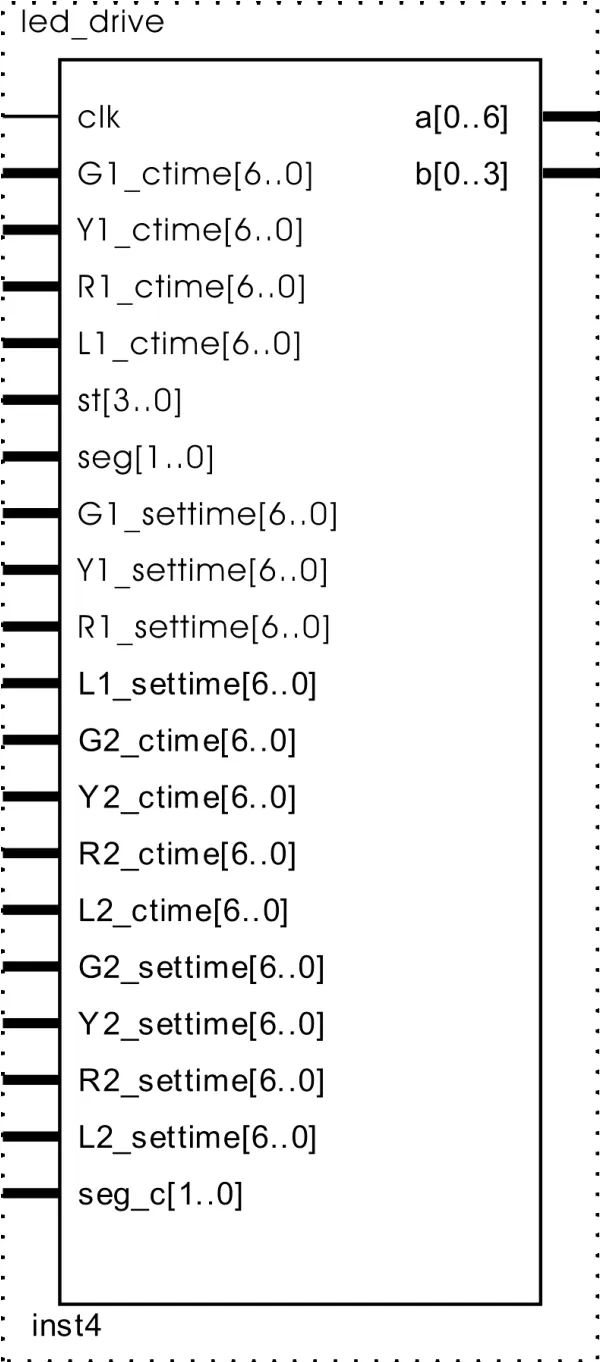

3.5 显示驱动模块设计

显示驱动模块主要实现把主副干道指示灯点亮持续时间的BCD码转化为7段码,以倒计时的方式在数码管上显示.其中,输入信号:G1_ctime[6..0],Y1_ctime[6..0], R1_ctime[6..0]和L1_ctime[6..0]分别为主干道各指示灯正常倒计时的当前值;G1_settime[6..0],Y1_settime[6..0], R1_settime[6..0]和L1_settime[6..0]分别为主干道各指示灯倒计时的时间调整值;G2_ctime[6..0],Y2_ctime[6..0], R2_ctime[6..0]和L2_ctime[6..0]分别为副干道各指示灯正常倒计时的当前值;G2_settime[6..0],Y2_settime[6..0], R2_settime[6..0]和L2_settime[6..0]分别为副干道各指示灯倒计时的时间调整值.输出信号:a[0..6]为数码管的段选,不同时刻显示不同的数字高电平有效;b[0..3]为数码管的位选,选择哪个数码管显示数字,低电平有效.

新建led_drive.v文件,输入共阴极数码管显示驱动模块程序,同时进行功能仿真验证设计正确性,并生成元件符号,以备进行顶层设计时使用,具体步骤同上.显示驱动模块电路符号如图7所示.

在各底层各模块设计与实现的基础上,新建原理图文件trafficlight.bdf,并在原理图文件的绘图区中双击鼠标左键,将project中的上述5个功能模块元件添加到原理图中,通过对各模块之间连线实现顶层电路设计.

图7 显示驱动模块电路符号Fig.7 Symbolofdisplay drivermodule circuit

4 顶层电路的仿真与实现

4.1 顶层设计文件的仿真

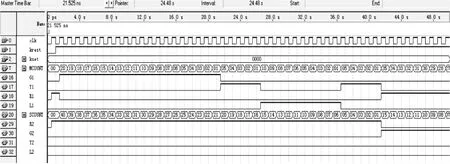

在设计好的顶层电路窗口上,新建一个波形文件,并保存文件名为trafficlight.vwf;选择菜单EditEnd time和Grid Size分别设置合适的仿真结束时间和周期;选择菜单Assignments Setting,并在Simulation mode下选择功能仿真模式Functional后,在Name窗口中双击左键添加所需要仿真的输入输出引脚,并把输出值设为十进制代码显示;给输入引脚clk指定输入仿真时钟波形;选择菜单Processing Generate Functional Simulation Netlist生成网络表;最后点击Processing Start Simulation(或点击)进行仿真.

交通灯顶层电路正常时序功能仿真波形如图8所示.由图8可知,倒计时显示时间和对应指示灯亮灭切换状态协调一致,可见系统可以实现正常的时序控制功能.

图8 顶层电路正常时序功能仿真波形Fig.8 Functionalsimulationwaveform ofcommonly scheduling in top-levelcircuit

交通灯顶层电路强制时序功能仿真波形如图9所示.这里以副干道为例,在系统正常时序控制模式下(k_set=0000),当系统响应强制时序控制模式(k_set=0001)时,主干道由绿灯亮变为红灯亮,次干由红灯亮变为绿灯亮,同时倒计时显示时间暂停,当k_set=0000时,强制功能失去控制,系统进入正常模式时,且各灯恢复到原来状态,倒计时从暂停时间开始正常计数,可见该系统能够实现强制时序控制功能.

4.2 顶层电路的实现

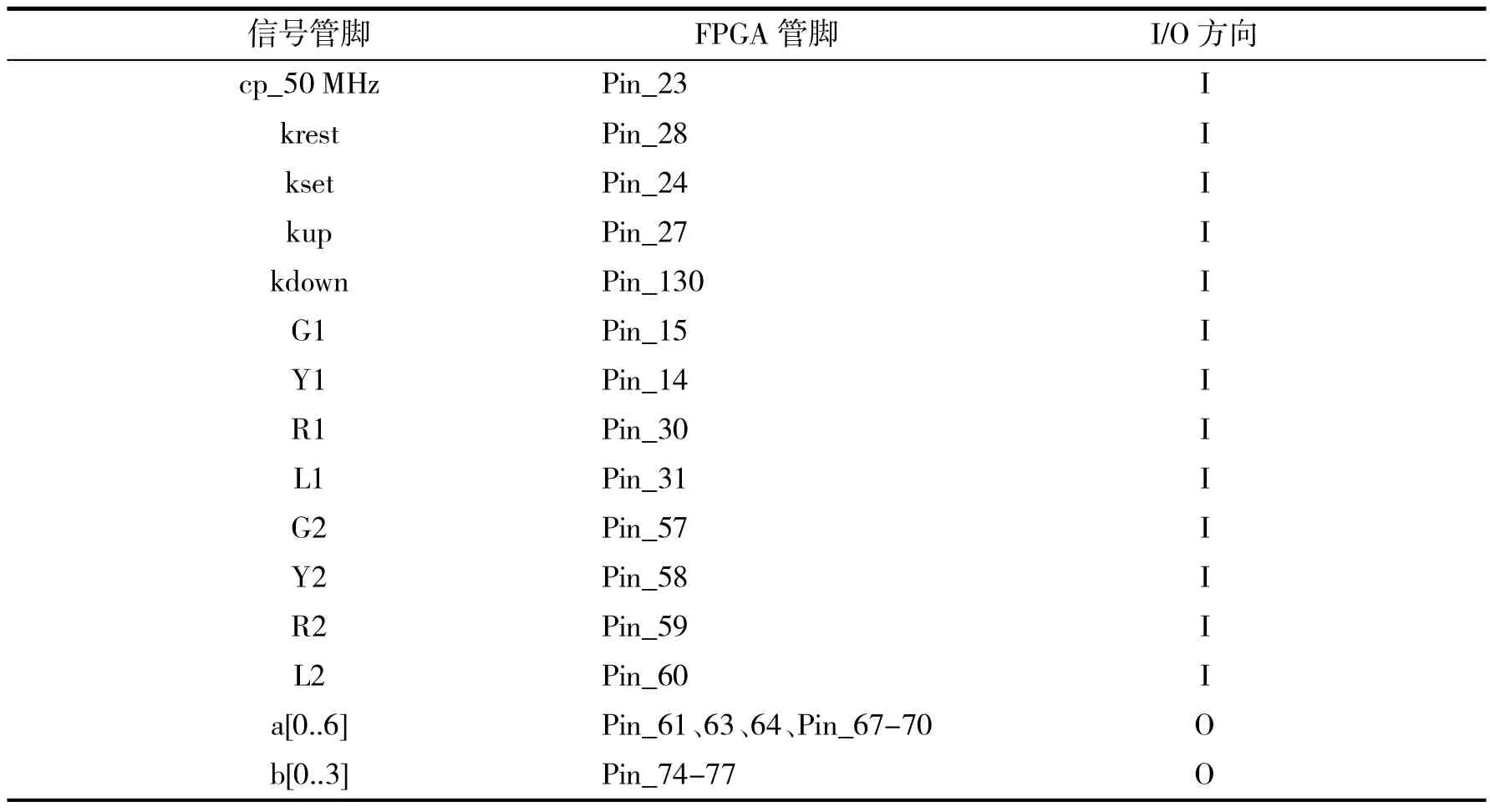

将顶层电路设计文件下载到ASK2CB型FPGA开发板上,系统运行正常,验证了整个系统设计的正确性,其具体实现过程如下:

(1)使用菜单AssignmentsDevice,选择可编程逻辑器件EP2C8Q208C8,并将所有未使用到的管脚全部置为三态输入,以防止某些高电压下会有较大电流灌向引脚,造成未用到的Flash芯片烧坏.

(2)选择菜单Processing Startcompilation(或者点击)进行工程编译,有错误返回进行修改,直到编译成功后,再选择菜Processing Analyze Current File(或者点击)进行综合.

(3)选择菜单Assignments Pins,弹出Pin Planner窗口,参照FPGA硬件电路对其用到的管脚进行分配,具体管脚分配如表3所示.

表3 管脚分配Tab.3 Pin assignment

(4)选择菜单Tools Programmer(或者点击)下载文件,点击Hardware Setup,在currently selected Hardware下拉菜单中选择USB-Blaster后关闭该窗口,再点击将当前工程文件中所生成的文件trafficlight.sof添加进来,采用JTAG下载模式把该文件下载到目标器件EP2C8Q208C8芯片中.

(5)针对表1主副干道灯亮时间关系做在线调试.系统复位按键krest置高电平1时,系统开始工作.先主干道绿灯亮,副干道红灯亮,然后按照预定状态持续时间和交通灯工作规则,倒计时器工作状态与相应交通指示灯状态同步,表明检验结果与设计要求相符.为了防止掉电程序丢掉,用AS下载模式把调试成功的文件m fdclock.pof文件烧写固化到FPGA芯片上即可长期使用.

5 小结

本设计借助QuartusII软件平台,采用verilog硬件描述语言,完成对系统硬件功能的设计,不仅缩短了开发周期、降低了成本、提高了设计效率,而且在程序修改和运行调试上更加灵活、方便、快捷.最后将设计系统程序下载到FPGA芯片EP2C8Q208C8中,经过调试,整个系统南北东西方向交通灯协调运行正常,性能更加稳定.

[1]楚岩,汪海光,邵严.基于FPGA的交通信号灯控制系统[J].现代电子技术,2012,35(9):184-186.

[2]王维松,王金生,章伟,等.十字路口智能交通灯控制系统的FPGA实现[J].电子科技,2012,25(9):37-38.

[3]林建华.基于VHDL语言的交通灯控制系统设计[J].仪器仪表用户,2011(3):31-32.

[4]付铭骥.基于FPGA的交通灯系统控制设计[J].现代电子技术,2011,34(15):167-169.

[5]沈晟.基于FPGA的交通灯控制系统的设计与实现[D].昆明:昆明理工大学,2010.

[6]袁海林,刘思颂,黄薇.基于FPGA的交通灯的设计与实现[J].电子质量,2013(3):15-19.

[7]华清远见嵌入式培训中心.FPGA应用开发入门与典型实例[M].北京:人民邮电出版社,2008:148-160.

[8]罗杰.Verilog HDL与数字ASIC设计基础[M].武汉:华中科技大学出版社,2008:188-196.

(责任编辑:卢奇)

Design and im p lementation of traffic light system control based on FPGA

Liu Yanchang,Wang Tingyu

(Henan Instituteof Scienceand Technology,Xinxiang453003,China)

Aimed at the traditional problems such as inaccurate control,complex peripheral circuits,inflexible program modification and higher costs,the design traffic light control systems adopt PLC or single chip microcomputer as a control chip,the system of each functionalmodule is designed with Verilog hardware description language and Quartus II software platform.Each functional module component symbols is added in the schematic file,and then achieve top-level module design through the connection combination from each bottom-level module.The overall design of the system has the advantages of parameter modification flexible,simple hardware circuit,high control precision,reliability,low cost and so on.The program is simulated by software and ran in ASK2CB development board. The result show that the control system works smoothly andmeets all requirements.

FPGA;traffic light control system;Quartus II;Verilog HDL

TP386

A

1008-7516(2013)04-0067-07

10.3969/j.issn.1008-7516.2013.04.016

2013-04-19

刘艳昌(1979-),男,河南鹤壁人,硕士,助教.主要从事智能控制与信息检测处理技术研究.