异构双核系统中多媒体应用的智能任务控制器

2013-04-25杨阳

杨 阳

(西安电子科技大学 电子工程学院,陕西 西安710071)

随着IC处理技术的不断创新和数字信号算法的进步,通过提高主频来提升单个处理器计算能力的传统方法,在提升性能的同时带来了诸如芯片功耗、发热量过高等问题。这种现象在嵌入式系统领域显得尤为突出。因此,双核处理器系统应运而生。由于可以满足以上特定需求,双核处理器尤其是异构双核处理器[1]已经成为目前的主流方案。随着双核平台中应用的复杂度快速增长,内核的计算资源将会被多个任务分时段共用。因此,为更好地利用异构双核处理器的计算能力,合理的任务管理机制必不可少。随着嵌入式系统在人们日常生活中的普及,异构双核体系结构正在发挥其巨大的实际应用价值,对异构环境下的任务调度[2]方法的研究具有广阔的应用前景。

1 研究背景

任务调度的本质是资源的合理分配,尽量提高系统的执行效率、稳定性和资源的利用率,实现多个处理核之间的动态负载平衡。对于异构环境而言,任务调度首先是将应用程序分割成若干个并行的子任务,生成应用模型。应用模型尽可能地提高任务间的并行性,并将这些任务调度到一定的处理器结构上并行执行。

常见的异构双核处理器大多集成了通用微处理器(MPU)和数字信号处理器(DSP)。MPU由于其自身结构特点,适合执行任务管理,而DSP适合计算密集型任务,二者协作提高系统效能。因此,传统上多采用MPU完成任务管理和调度[3]。然而,处理器在处理现行的线程或任务时会冻结其他线程,系统无法同时处理两个线程。此外,MPU上的任务管理会引起MPU和DSP间的频繁通信。由于MPU中的任务调度和任务更新等,DSP的总执行时间中存在空闲时间。当任务粒度减小时,尽管单次任务调度和任务更新时间保持不变,但由于次数增多,任务管理的总时间变长,系统整体效能因此也受到影响。

为减小任务管理时间和处理器间通信次数,部分研究者提出了利用DSP完成任务管理的双核系统架构[4]。然而,DSP上的程序控制和中断处理的消耗较大。DSP上有大量的寄存器用来存储临时数据流,但DSP几乎没有缓存机制来确保执行中的可预见性。这些结构设计会带来频繁的上下文交换,包括用户模式和内核模式间的转换,从而造成巨额开销。另外,用计算能力较强的DSP专用模块执行常见的简单算术逻辑运算则非常低效。

针对以上两种方式的优缺点,提出了适用于异构双核系统上的多媒体应用的智能任务控制器。此设计利用了多媒体应用自身的特点,有效解决了处理器间通信的问题。

2 任务模型

任务模型是根据应用程序分割之后的任务及其之间关系建立的模型,是系统进行任务调度和资源分配的基础。设计采用适合描述信号处理系统中数据样本流的进程网络。此进程网络属计算模型,多个并行进程可同时在此网络中运行。此模型为直接图表标记法,每个节点代表一个进程,每条边代表一个单向先进先出数据列。进程能够从对应的数据列中获取数据,然后将生成的一组数据输出到相邻的数据列中。当进程或节点试图从空输入列中获取数据时,它会被阻塞。

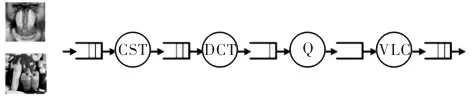

图1描述了JPEG编码[5]的进程网络。如图1所示,JPEG编码分为4个进程,分别为彩色空间变换(CST)、离散余弦变换(DCT)、量化(Q)和可变长度编码(VLC)等。这四个进程两两连接成CST-DCTQ-VLC列。

图1 JPEG编码流程

3 智能任务控制器

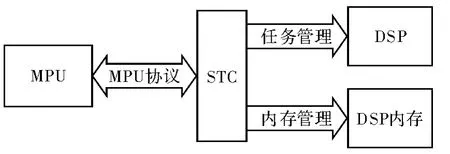

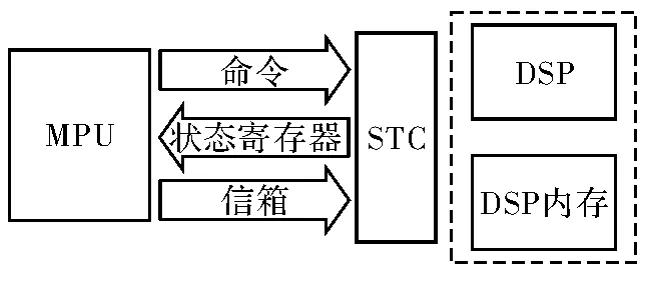

集成了智能任务控制器(STC)的异构多核处理器架构如图2所示。此架构提供集成化的API,易于构建流媒体应用模型。程序员不用考虑内存分配、任务调度、负载平衡、同步和资源竞争等架构细节。STC不仅负责运行中的任务管理,而且通过并行处理MPU和DSP上的任务,减小来自MPU的压力以及系统开支。

图2 异构多核处理器架构

智能任务控制可分为处理器间通信和任务管理等两个基本功能。有这些功能做辅助,MPU只需利用STC提供的高阶API构建多媒体应用模型,然后将应用传递给STC执行。应用初始化和传递完成后,STC将内核和内存动态分配给从应用中提取的任务。

3.1 任务管理

STC用3个表格管理任务,监视MPU状态和控制多线程DSP处理器的计算资源,它们分别为任务控制表(TCB)、队列表和分配表。

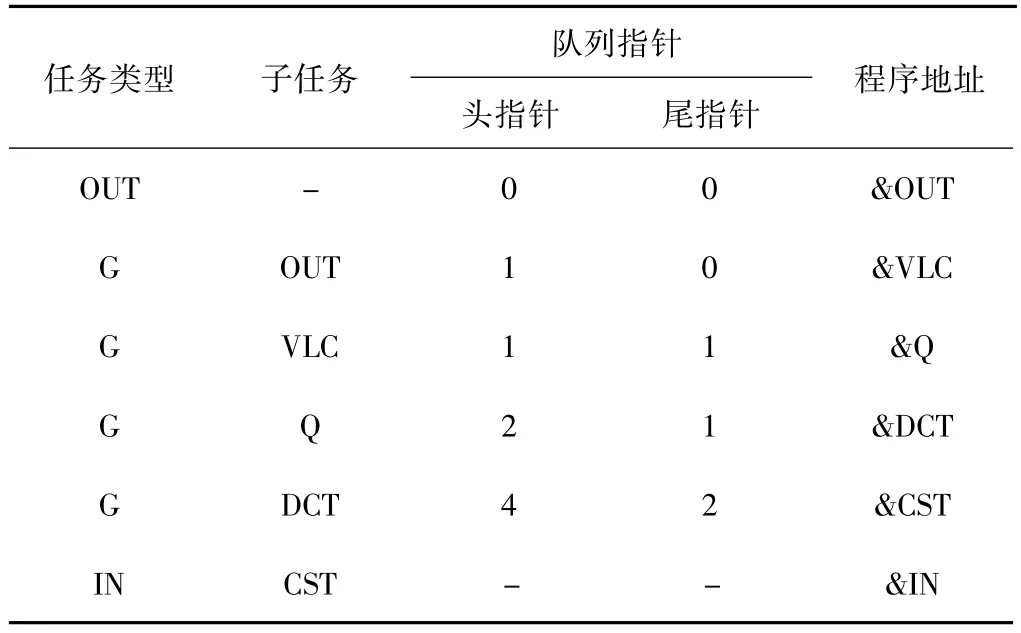

任务控制表的每一行对应任务列表中每个任务以及完成该任务必不可少的信息,包括任务类型、子任务、队列指针和程序地址等。

表1 任务控制表

本文将任务类型分为3种,输入任务(IN)、输出任务(OUT)和通用性任务(G)。利用输入进程可以从大的输入缓存中分流多个数据到进程的内部队列。相反,利用输出进程可以从内部队列中分离多个结果到输出缓存中。借助于输入进程和输出进程,可以利用程序局部化特性降低IPC开支。与输入进程和输出进程不同,其它用于应用的通用性进程由特定功能的交替多线程DSP处理器处理。图1中,CST、DCT、Q和VLC等均为通用性任务。子任务用来指示进程在进程网络中的优先权。例如,图1中,CST的子进程是DCT。当CST从数据列中获取一组数据后,它需要生成一组结果数据到它的子数据列中。

进程网络中每个进程的数据列都存在头指针(Head)和尾指针(Tail)。任务控制表利用头指针和尾指针来表示每条数据列上输入数据和输出数据的逻辑索引地址。对于每个任务,可用的数据数量可以由头指针和尾指针的差值来确定。

程序地址用来记录处理器指令内存中任务的首个指令地址。在DSP执行任务前,应初始化程序计数器(PC)到对应的程序地址。

队列表对应数据网络中每个任务数据列中数据单元的内存分配,如表2所示。例如,VLC的数据列中的两个数据单元分别存在于DSP处理器数据内存的第5页和第3页。

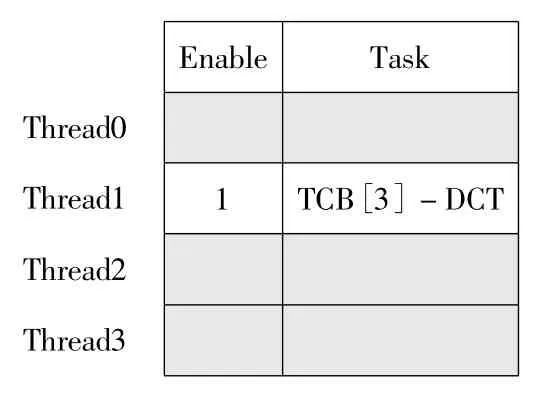

分配表用来管理DSP处理器的硬件资源。如表3所示,每个DSP线程的状态都存储在分配表中。”1”表示使能线程,也就是说,硬件线程1正在被任务控制表所占用。此时共有3个可用的硬件线程。

表2 队列表

表3 分配表

任务调度政策决定哪个任务会在DSP上运行。本设计降序分配给进程网络中每个任务一个优先级以确保计算流畅执行。图1中,优先级从VLC到CST分配,即VLC拥有最高优先级而CST拥有最低优先级。所以,越接近进程网络末端的任务越早执行,如此,进程网络的计算流将不会被阻塞。

3.2 处理器间通信

如图3所示,在提出的双核系统中,DSP协处理器和MPU通过以下方式通信。其中,信箱用于DSP与MPU的同步。STC将从MPU获取的特定地址视为命令,并响应这些命令。

图3 处理器间通信

STC作为DSP的代理,处理处理器间通信,并管理DSP资源以执行任务。任务完成后,DSP告知STC,STC利用信箱告知MPU。最后,MPU清除DSP内存中的结果并获取另一待执行的任务。通过输入输出双缓存,提高了处理期间通信效率。如前所述,输入进程可以从输入缓存分流数据,而输出进程可以分离数据到输出缓存。前者用于数据转移,后者用于任务计算。当MPU需要输出数据到DSP去执行时,它只需读取自身的状态寄存器,无需等待DSP的响应或者中断DSP计算。另一方面,一旦任务完成,STC便立即通过信箱告知MPU。

4 实验分析

利用ESL[6]设计方法构建了一个双核模拟平台。此平台包含ARM处理器模型、AMBA AHB总线模型、内存模型以及其它相关模块的模型。其中,两颗ARM926处理器模型由AMBA AHB总线连接,分别作为MPU和DSP。MPU的工作频率为250 MHz,DSP的工作频率为500 MHz。

仿真验证阶段,设计采用像素为256×256的JPEG图像编码为实际应用模型。为证明本设计的有效性和优越性,采用了两组对照组,分别为MPU和DSP实现任务管理。MPU实现任务管理时,操作系统将JPEG编码过程分成CST、DCT、Q和VLC等4个任务,然后再分配这些任务到DSP去完成计算加速。DSP管理任务时,DSP上的轻量级内核将会完成任务分割和调度,而STC则无需任何实时操作系统或内核。

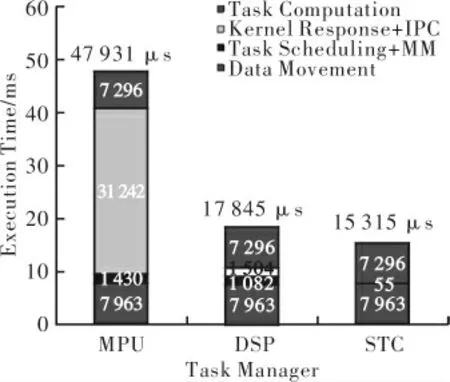

图4为3种任务管理机制的执行时间。可以看出,STC实施任务时,内核响应和处理器间通信时间仅为1μs。且由于其专用的硬件设计,任务调度和内存管理仅需要55μs。与MPU和DSP实现任务管理相比,分别减少了68%和15%的执行时间。

图4 执行时间

5 结束语

针对异构双核嵌入式系统中的任务管理问题,提出了一种适用于多媒体应用的智能任务控制器。在利用MPU和DSP各自优点的基础上,动态分配任务并消除了处理器间通信对系统性能造成的影响。由实验结果可以看出,该智能控制器与传统方式相比响应时间短,硬件利用率高,运行时间短,实现了系统性能的提升。

[1]ZHANG Ziming.Data partitioning on heterogeneous multicore platforms[C].Austin TX:IEEE International Conference on Cluster Computing,2011.

[2]QU Gang.Power management of multicore multiple voltage embedded systems by task scheduling[C].Xi'an:International Conference on Parallel Processing Workshops,2007.

[3] 刘侃侃.异构多核环境下的任务调度方法研究[D].杭州:杭州电子科技大学,2009.

[4]Texas Instruments Inc.TMS320 DSP/BIOS User Guide[M].Texus:Texas Instruments Inc,2001.

[5]Charles Poynton.Digital video and HDTV algorithms and interfaces[M].USA:Morgan Kaufmann,2012.

[6]GRANT M,BRIAN B,ANDREW P.ESL design and verification[M].USA:Morgan Kaufmann,2007.