基于协议芯片和工具链的ARINC659总线开发平台

2013-04-25臧威,刘芳,李锐

臧 威,刘 芳,李 锐

(中国航空工业自动控制研究所 软件工程中心,陕西 西安710065)

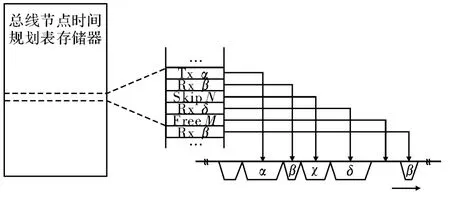

飞行控制系统是典型安全关键系统,总线就是神经中枢,系统的安全性、可靠性与之密切相关。素有“SAFE BUS”之称的ARINC659总线[1]基于时间触发协议,其时间行为通过设计阶段的指令表规划确定。如图1所示,由于总线时间槽与规划表存储器中的指令存在着一一对应关系,可以看到,在时间槽α内,总线必将执行指令TXα,以此类推,其余时间槽位内的总线行为也是唯一确定的,这正是时间确定性的体现。总线的性能可满足飞控系统需求,享有“SAFE BUS”之名,波音777已将该总线成功应用到航电通信中。

时间规划是总线应用的关键。传统方式下,规划工作主要依赖纯文本操作,由于缺乏相应规则保障机制,过程繁琐且效率低下,完整表指令开发至少需要一周时间。随着采用ARINC659总线的课题日益增多,通用总线开发平台研制工作越显迫切。在国外,相关技术被Honeywell公司垄断并实施封锁;在国内,文献[2~5]对总线的部分运作机制和逻辑进行了研究和实现,文献[6~7]则对总线芯片逻辑验证平台的搭建进行了阐述,但包含硬件逻辑设计、特别是配套软件工具链在内的集成开发平台的研制工作相关研究甚少。本文阐述了自主研制的ARINC659集成开平台:通过完全遵循《ARINC659协议》、具有自主知识产权的协议芯片和开发工具链的协同运作,构建出涵盖硬件、逻辑设计到指令表规划、编译链接、加载和监控调试的全流程集成开发平台。工程试验和应用表明,其大幅降低了应用的复杂度,提高了开发设计的效率,加快了工程化应用的步伐。

图1 ARINC659总线时间触发运作模式

1 平台架构

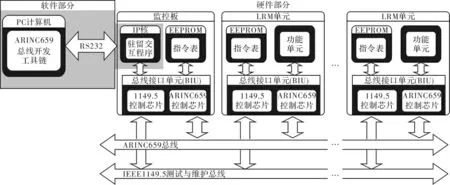

ARINC659集成开发平台由硬件和软件部分构成。硬件部分的协议芯片是平台核心,开发工具链是总线行为确定性设计的有力保障,两者相辅相成。图2显示了开发平台的总体架构。

图2 开发平台主体架构

1.1 平台硬件

平台硬件部分由总线逻辑、监控板和LRM节点单元组成,总线包括ARINC659背板通讯总线以及IEEE1149.5[8]调试加载总线。节点单元通过接口单元(BIU)挂接在总线上,在总线协议芯片的控制下进行通讯。平台硬件相当于一台工程应用中的飞行控制计算机,它已含括其中最为关键的部分。

1.2 平台软件

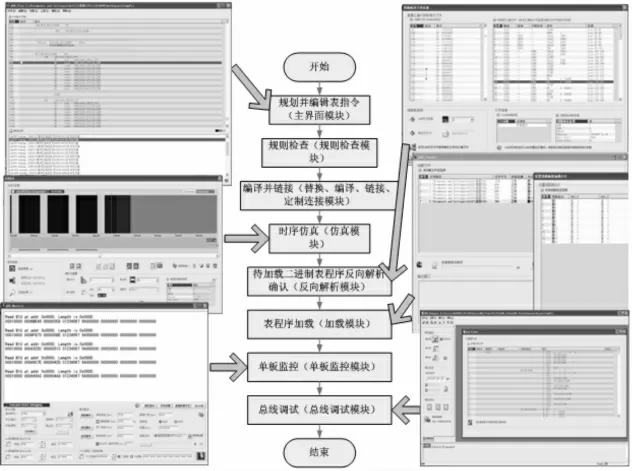

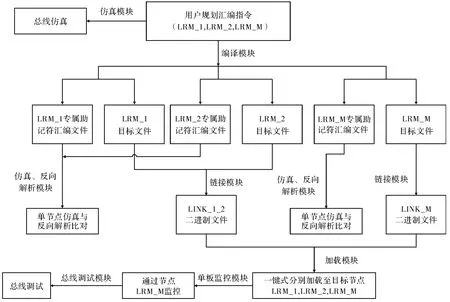

平台软件部分包括PC终端上运行的ARINC659总线开发工具链以及驻留平台硬件监控板IP核内的交互程序。PC终端完成指令表规划、窗口波形仿真、规则检查、编译链接等基础功能。交互程序是平台软硬部分的纽带,PC终端通过RS232总线与它实现数据互传并建立软硬件握手通讯机制,开发工具链的指令表一键式加载、单板监控和总线调试等高级开发功能的实现正基于此。图3显示了软件主要界面模块在指令表开发流程中的分布情况,可以看到,从指令表规划到总线调试,在流程的每个环节上,都有专用的软件模块负责相应的工作。

图3 总开发流程和工具链的部分图形化界面模块

2 平台实现

2.1 硬件部分

(1)总线逻辑(芯片)。ARINC659总线采用四余度架构,每一余度具有独立时钟,主时钟连同以上4个时钟构成了芯片的5个时钟域,而时钟域的同步性能在一定程度上决定着芯片研制的成败。

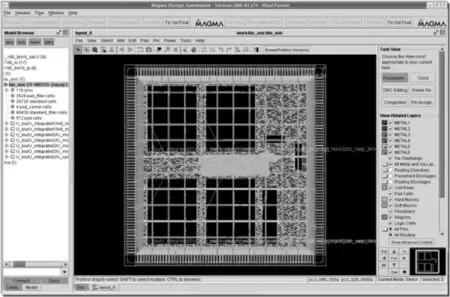

基于对两款总线协议的消化与理解,通过对时钟域同步、双BIU之间协同工作、比较与互监控、BIU发送数据的自监控、异步RAM的同步读写冲突等技术的研究,文中研制了具有自主知识产权的时间触发通讯平台协议芯片,如图4所示,进行了流片并通过了系统级验证。

图4 协议芯片的版图

ARINC659总线和IEEE1149.5总线的协议芯片出现在监控板和各节点单元的BIU中,逻辑均严格遵循各自协议。各节点总线接口单元中均含有两款协议芯片,节点通过BIU收发数据并均按照相应总线协议的规定运作。另外,芯片逻辑研制过程中,为配合调试监控技术,还定义了多种记录总线运行状态的寄存器。

(2)监控版。EEPROM存放二进制指令表,ARINC659总线协议芯片按照指令表控制着监控节点的数据收发等总线行为。加载、监控和调试中,通过IEEE1149.5总线,节点单元以“从”身份受控于“主”身份的监控板。监控板采集过程中的数据和状态信息,专为调试、加载和监控研制,飞控计算机正常工作时,它将不再出现。另外,前述的交互程序位于监控板逻辑的IP核内。

(3)LRM节点单元。EEPROM存放二进制指令表,ARINC659总线协议芯片按照指令表控制本节点数据收发等总线行为;通过IEEE1149.5总线协议芯片的控制,节点单元与监控板进行通讯,实现加载、调试和监控等功能。节点单元是组成飞控计算机基本的功能模块,具有各自的专属功能单元。

2.2 软件部分

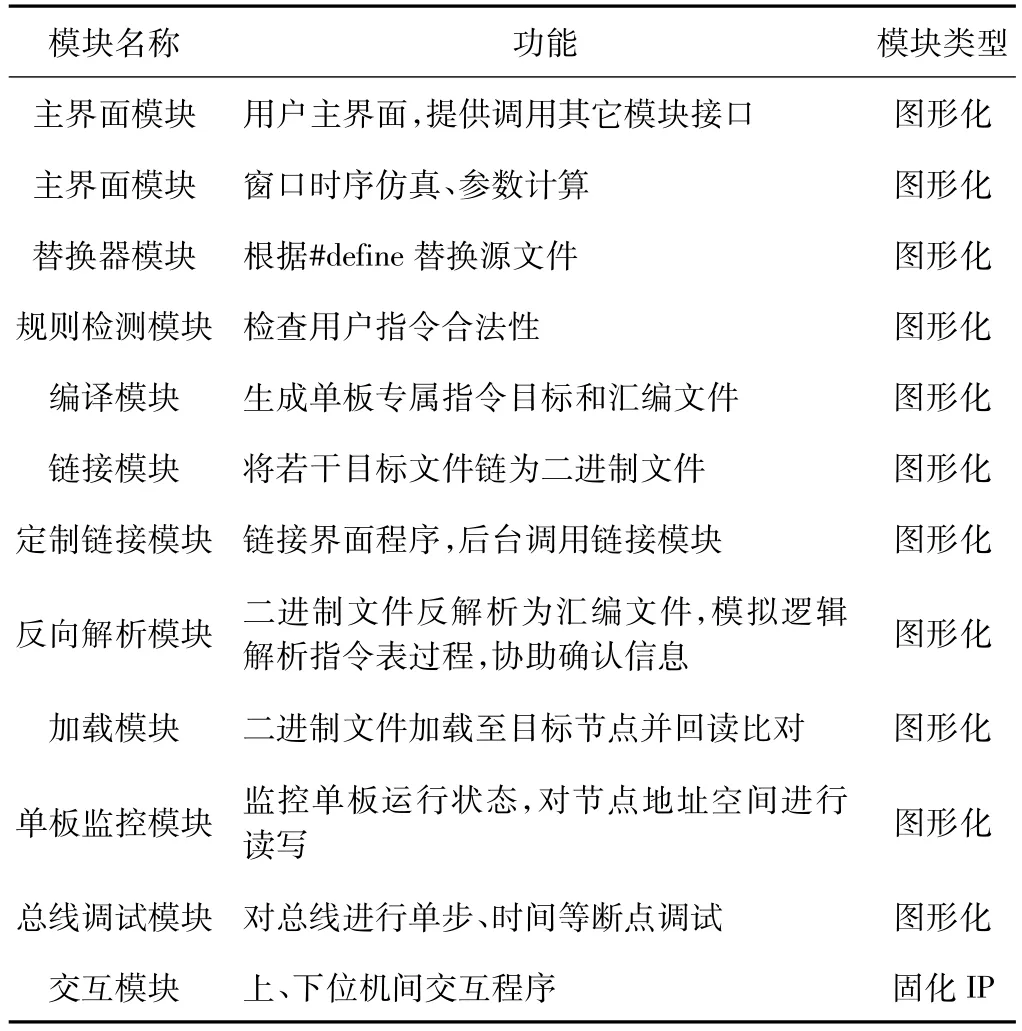

表1所示为全部软件模块的属性信息。软件部分各个模块通过功能协同,形成开发工具链。研制中突破的关键技术包括:指令规则检测比对技术、波形时序仿真算法与图形化仿真技术、指令编译链接技术、ARINC659总线调试技术和故障注入技术等。

表1 软件工具链模块属性

(1)替换器模块。用户可采用类似C语言“#define”宏定义的格式编写指令表,工具链通过调用替换器得到遵循协议的指令表。这种机制是对《ARINC659协议》的创新拓展,增强了表指令的可读性和可维护性。

(2)仿真模块。完成指令窗口时序仿真和重要参数计算。按时长比例显示时序波形,用户在硬件调试前便可基于图形化界面分析窗口分布、波形周期等重要信息;同时,还生成仿真报告,并与源文件进行了交叉关联。这些机制可使得规划漏洞及早修补,避免后级传递。

(3)编译、链接模块。编译模块解析总线指令表获取每个单板专属指令的汇编和目标文件:汇编文件用于单板仿真和反向解析比对,目标文件用于链接生成二进制文件。总线指令面向全部节点,而专属指令只针对某一节点,每条指令采用异于总线指令的编码方式描述本节点个体行为。采用该方式可提升单板指令执行效率并节省存储空间。

链接模块将若干目标文件按平台方案规定格式拼接整合为二进制加载文件,可参与合并的文件由“COMBINABLE”指令指定。加载文件含带若干节点的指令,故加载节点可在指定的飞控机槽位间复用并执行相应功能。

(4)单板监控模块。完成单板的监控功能。用户通过连续读取、周期读取、单次写入、文件写入等方式,控制和观测目标节点状态,协助完成板级调试和故障排查。

(5)总线调试模块。模块严格遵循《ARINC659协议》定义的调试特征,基于IEEE1149.5调试总线,实现ARINC659总线单步、时间断点等调试技术,完成机箱级综合调试。用户可对总线进行故障注入,并对总线数据进行观测、修改,从而模拟实际运行中多种可能故障状态。模块将总线运作状态显形化,有效协助用户发现并解决机箱系统级潜在故障和问题。

3 应用示例与性能比对

ARINC659总线每个余度的功能模块挂接在ARINC659总线上,用户通过规划模块的时间槽位及动作,完成飞控系统诸多参数与控制信号的传递。

通过一份含有3个模块的指令表阐述了基于集成平台的开发过程。实际应用案例更为复杂,但其机制相似。让节点LRM1将自带RAM的10个字发送至LRM2。为配合监控环节之需,再让LRM2把数据发送给监控板LRM_M,从而实现LRM1至LRM2数据发送的监控。监控可通过用户指令设置与监控板信息采集实现。

步骤1在主界面模块中创建工程并编写指令表。

步骤2调用自动编译链接功能,完成替换、规则检查、编译和链接。链接器按“COMBINABLE”的指定把LRM_1和LRM_2的目标文件链为二进制文件LINK_1_2,LRM_M的目标文件则单独形成二进制文件LINK_M。

步骤3调用仿真器进行仿真,查看波形分布、相关参数和仿真日志,如图5所示。

图5 仿真结果和日志

步骤4基于硬件开发平台(插装有监控节点LRM_M和普通节点LRM_1、LRM_2),调用加载器将LINK_1_2、LINK_M两份二进制文件加载至相应目标节点。

步骤5调用单板监控器,读取LRM_M上RAM中以0x160为起始的连续10个地址单元,监控LRM_1发送LRM_2的数据、时标版本信息以及其它状态信息。

步骤6将连同监控节点在内的3个节点移装至飞控计算机,调用总线调试模块进行单步、时间等断点调试和其它总线操作。至此完成了最基本的开发过程,如图6所示。

图6 基于集成开发平台的开发过程

基于集成平台的基本开发过程,相对于采用传统方式开发较简单。借助ARINC659集成开发平台,摆脱传统方式,用户只需通过图形化界面一次性开发针对全体模块的通用表指令程序,通过规则检测和仿真模块可锁定并指导排除其中漏洞和隐患,编译与链接模块将通用表程序“拆解”为针对单个或某些模块的专属二进制表指令,加载模块通过智能识别目标板自动进行加载,最后通过调试与监控模块,用户可以动态监控、跟踪运行状态。

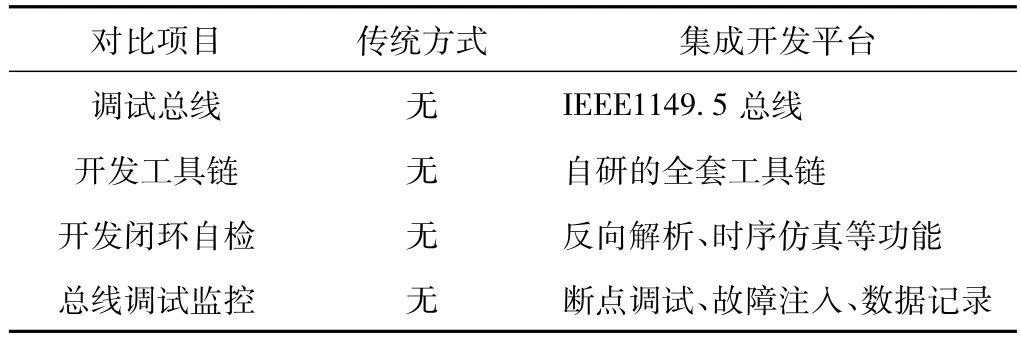

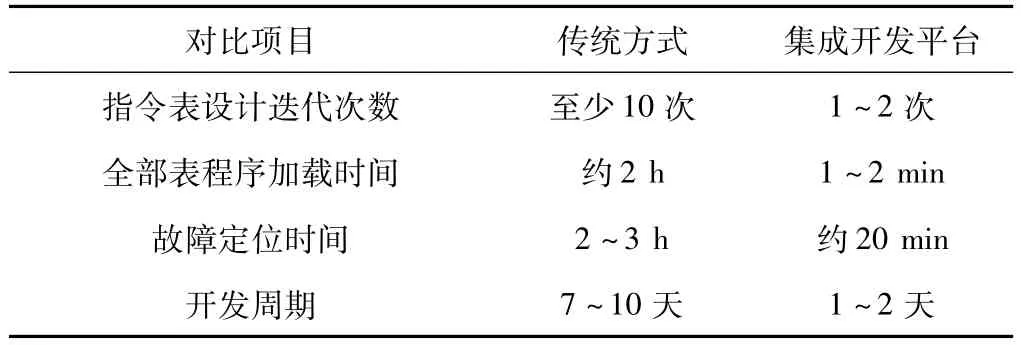

为更好地说明平台优势,将传统方式与平台开发方式的性能数据及某重点课题经历的传统方式与集成平台方式开发的两个阶段,由表2和表3将前后方式的功能覆盖和性能指标进行了对比。

表2 功能覆盖对比

表3 性能指标对比

从对比结果可见,相较于传统方式,基于平台的开发模式实现了更为完备的功能覆盖,从仿真、监控到调试,这些功能保障了开发的闭环和可控,进而形成了完善的总线开发流程。而由量化指标看,从指令表设计到故障排除,平台可使时间投入得以缩短为几分之一至几十分之一,通过两年多的应用实践,平台取得了良好的效益。

4 结束语

以协议芯片和开发工具链的研制为核心,构建了ARINC659总线集成开发平台,并形成了基于平台的全套开发流程。开发平台实现了时间规划工作的智能覆盖,缩短了总线开发周期,提升了工作能效。

[1]Airlines Electronic Engineering Committee.Backplane Data Bus ARINC659 Specification[S].Annapolis,USA:Aeronautical Radio Inc,1993.

[2] 汪迪娜,樊晓桠,安建峰.ARINC659总线监控卡的设计与实现[J].微电子学与计算机,2011,47(8):44-46.

[3] 何向栋,樊晓桠,安建峰.ARINC659总线接口跨时钟的研究与设计[J].计算机工程,2010,36(20):214-216.

[4] 李宝羽,张盛兵,安建峰.ARINC659总线协议同步机制的研究与实现[J].航空计算技术,2009,29(2):117-119.

[5] 孟锐,张盛兵,安建峰.ARINC659总线协议容错机制的一种设计与实现[J].航空计算技术,2008,38(6):111-118.

[6] 马宁,李玲,田泽,等.ARINC659总线协议芯片的仿真验证[J].计算机技术与发展,2010,20(1):205-208.

[7] 强新建,田泽,淮治华.基于ARINC659的FPGA原型验证平台的构建与实现[J].计算机工程与设计,2010,31(12):2726-2728.

[8]Test Standards Technology Committee of the IEEE Computer society.ISBN 1-55937-558-2 IEEE Standard for Module Test and Maintenance Bus(MTM-Bus)protocol[S].New York,USA:the Institute of Electrical and Electronics Engineers,Inc.,1995.