一种新型高速宽带数字下变频器的FPGA实现

2013-04-25庞少龙马志刚吴子贤

庞少龙,马志刚,吴子贤

(西安电子科技大学 电子工程学院,陕西 西安710071)

随着软件无线电技术被广泛应用于蜂窝通信及各种军用和民用的无线通信系统中。作为软件无线电接收机的核心技术,数字下变频技术也得到普遍应用。

传统的数字下变频器(DDC)结构包括数控振荡器(Numerical Controlled Oscillator,NCO)、混频器、低通滤波器和抽取器。其实现方法占用FPGA资源多,运算复杂程度高,功耗高而效率低。因此常见的高效DDC实现方法采用了多相抽取滤波结构,在滤波运算前就降低了数据的采样速率,减轻了后续滤波环节的运算负担,降低了DDC运算复杂度和功耗。本文基于多相抽取滤波的高效结构,给出了一种更加简化高效的宽带DDC实现方法。

用现场可编程阵列(FPGA)来实现数字下变频器有许多好处。FPGA在硬件上具有较强的稳定性和较高的运算速度,在软件上具有可编程的特点,可以根据不同的系统要求,采用不同的结构来完成相应的功能,便于进行系统功能扩展和性能升级。

1 数字下变频器原理

1.1 典型数字下变频器

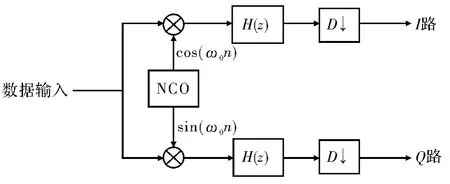

典型的数字下变频的实现框图如图1所示。采样数据输入后与两个正交的本振序列相乘,再通过数字低通滤波滤除带外信号,便可以得到基带的正交基带分量I和Q。

图1 典型数字下变频系统实现框图

图1中低通滤波器和后接的抽取器一起构成了标准的抽取系统,通常采用多相滤波结构来实现。如果抽取因子D很大,低通滤波器所需的阶数又较高时,实现这种单级多相滤波结构则比较困难,必须采用多级抽取实现。

1.2 基于多相滤波结构的数字正交变换下变频器

此种基于多相滤波的数字正交变换新方法,该方法不仅不需要正交本振,而且后续数字低通滤波器阶数也较低,用FPGA实现相对简单。

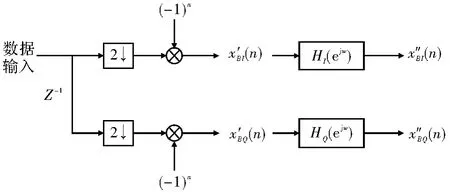

即,x'BI(n)和x'BQ(n)两个序列分别是同相分量xBI(n)和xBQ(n)的2倍抽取过程,实现过程如2图所示。

图2 正交变换的多相滤波实现

容易证明,x'BI(n)和x'BQ(n)的数字普为

也就是说,由于采取了奇偶抽取,导致运算结果在时域上相差了半个采样点,这种时间上的“对不齐”可以采样两个延时滤波器实现,且两个延时滤波器满足以下条件

实际上,HQ(ejω)和H1(ejω)就是抽取滤波器中第奇数个滤波器系数和第偶数个滤波器系数。因此,只需按照滤波器的设计方法求出滤波器系数,并以此提取奇数个滤波器系数和偶数个滤波器系数即可。由于HQ(ejω)和H1(ejω)主要被用于调节序列的延时关系,并不用于对采样信号滤波,因此,HQ(ejω)和H1(ejω)只需要很低的滤波器阶数[1]。

2 数字下变频器的FPGA实现

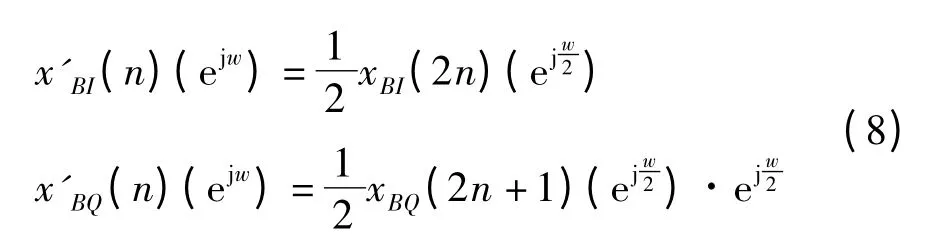

此处以一种雷达数字中频接收机为例来说明基于多相滤波正交变换结构的数字下变频在FPGA上的实现。输入信号为中频500 MHz,带宽分别为100 MHz、20 MHz、2 MHz、点频,脉冲宽度20μs的线性调频信号。该信号经过A/D变换后送入FPGA进行数字下变频。选用FPGA型号为Altera公司Arria GX系列的EP1AGX60。用一片EP1AGX60配合软件设计即可实现此DDC的全部功能。ADC与DDC的系统框图如图3所示。

图3 ADC与DDC的系统框图

2.1 两倍抽取降速的FPGA实现

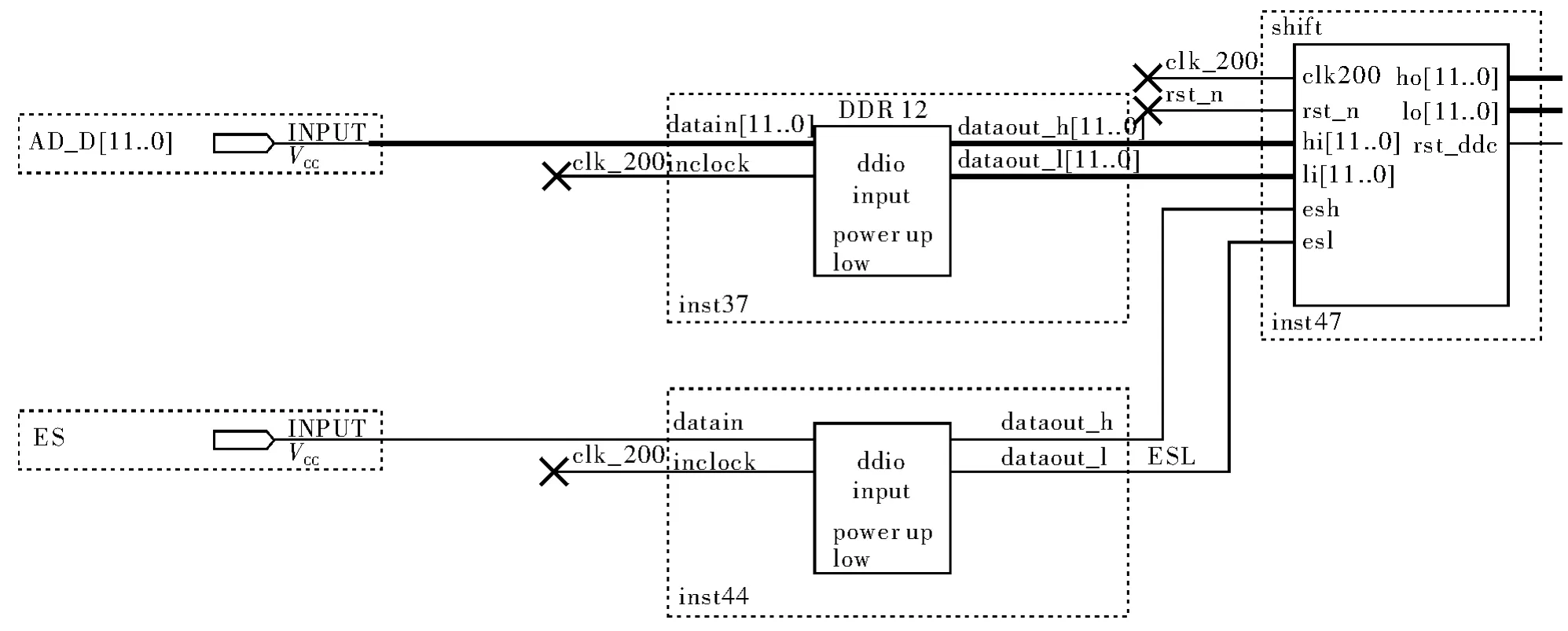

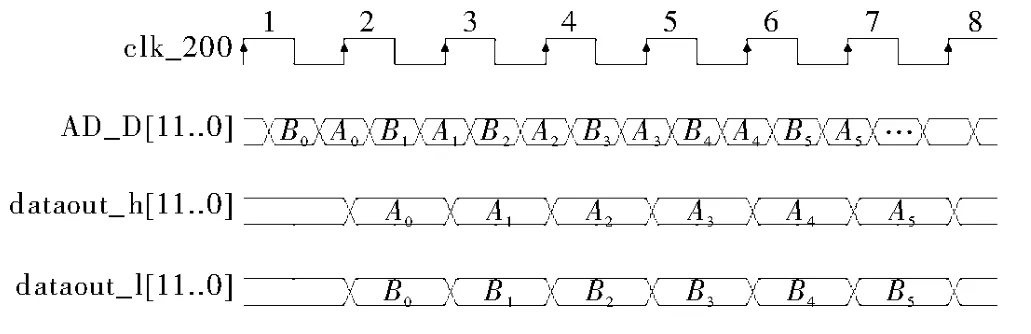

依据多相滤波正交变换的结构首先应将400 MHz数据率的12位数据进行两倍抽取。因为ADC提供给FPGA的全局时钟为200 MHz,做两倍抽取可以将200 MHz的双沿数据转换为两路单沿200 MHz的数据,达到初步降速的目的[2-3]。具体实现采用DDIO双沿采数的IP核,其逻辑框图如图4所示。

其工作时序如图5所示,每个时钟周期DDIO模块输出的两个12位数据dataout_h[11..0]与dataout_l[11..0]为本时钟周期上升沿和上个时钟下降沿所采集到的两个12位数据An和Bn。

图4 DDIO两倍抽取降速框图

图5 DDIO两倍抽取降速时序图

2.2 数控振荡器(NCO)模块的FPGA实现

数控振荡器(Numerically Controlled Oscillator,NCO)的作用是产生正弦、余弦样本。频率较低时要产生NCO的正余弦样本,可以用实时计算的方法。但在超高速采样的情况下,实时计算方法实现起来比较困难,所以NCO一般采用直接数字合成(DDS)的方法实现:通过相位累加器得到相位值,将相位值截短后查正弦/余弦表,得到所需的正弦/余弦值。相位值截短和生成正弦/余弦表时的幅度量化均会带来噪声[5]。

在一些特定情况下,选用合适的采样率,能够不使用直接数字合成(DDS)而用固定系数来产生正弦、余弦样本。这样不仅避免了相位值截短和幅度量化带来的噪声,同时实现起来相对容易,占用的FPGA资源少。本系统即是用固定系数来产生正弦、余弦样本[6]。

为将信号频谱搬移到基带,根据式(6),将NCO及乘法器部分简化,只通过信号取反来产生。即I路数据为原始数据经DDIO接收后的其中一路数据乘以(-1)n;Q路数据为原始数据经DDIO接收后的其中一路数据乘以(-1)n。对I、Q录数据进行乘以(-1)n的操作后,输出的两路数据就为正交变换后的数据,如图6所示。

2.3 平衡相位滤波器的FPGA实现

图6 NCO与乘法器模块

当信号经过NCO与乘法器模块后,I路数据与Q路数据在时域上会相差半个采样点,这半个延迟差是由于采用奇偶抽取所引起的,所以采用两个时延滤波器加以校正。将两路数据分别通过两个32阶的抽取滤波器,输出即为I和Q两路基带数据。其滤波器系数分别为原型32阶滤波器的第奇数个和第偶数个系数,用于调节两路信号的相差。该滤波器采用Altera公司提供的FIR IP核实现,FPGA逻辑如图7所示。

图7 平衡相位滤波器

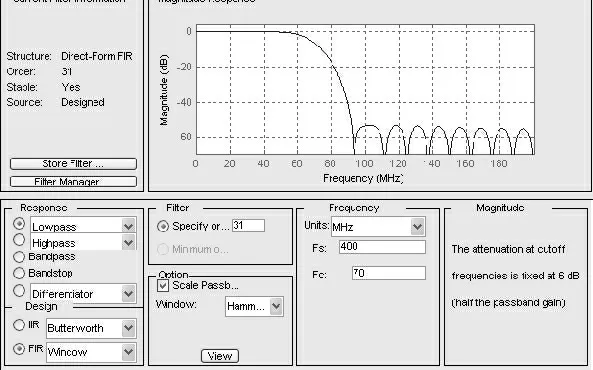

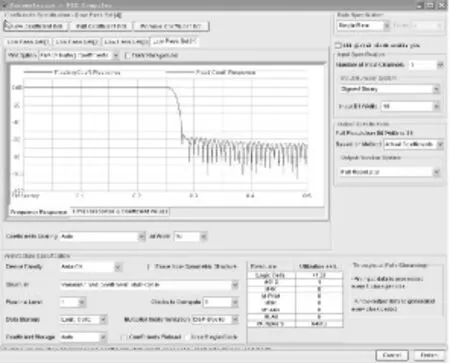

该平衡相位滤波器的具体设计采用基于窗函数的“汉明窗”设计方法,采用Matlab的fdatool设计工具完成,其设置参数如图8所示。将生成的滤波器系数导入到FPGA的FIR IP核中。

图8 平衡相位滤波器参数设置

在FPGA中平衡相位滤波器FIR IP核的配置如图9所示。

2.4 抽取滤波器的FPGA实现

图9 平衡相位滤波器的配置

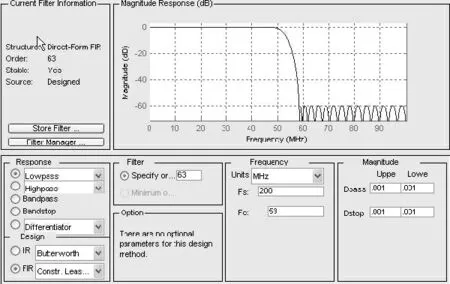

抽取滤波器为64阶,其实现如图10所示。采用直接型结构,输入数据分别和相应的系数相乘,然后通过流水线加法器将结果进行累加输出。

滤波器设计采用基于最优化设计方法,采用Matlab的fdatool设计工具完成。对于20 MHz的带宽,截至频率设置为14 MHz;对于2 MHz的带宽,截至频率设置为4 MHz;对于2点频带宽,截至频率设置为2.9 MHz,其他参数设置相同,如图11所示。

图11 100 MHz带宽信号抽取滤波器参数设置

滤波器的实现采用Altera提供的IP核,具有稳定、速度快、效率高、使用配置方便且直观的优点。Reload_fir为系数可重载滤波器,根据BW控制字的不同,选择不同的滤波器系数,从而实现不同的带宽选择。Para_cnt为抽取使能控制,根据不同的带宽,选择不同的抽取倍数,并使其输出信号作用于D触发器的使能端口,实现抽取功能。

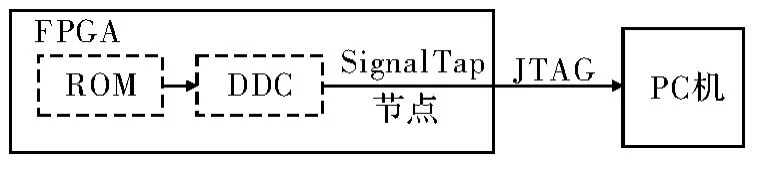

3 DDC实验结果

DDC功能测试连接如图13所示,采用Matlab产生2 048个标准的宽带中频信号数据,并把产生的中频数据存储到FPGA的ROM中,作为DDC逻辑的数据源。然后通过SignalTap对数字下变频逻辑的运算结果进行存储并分析。

图12 可重载滤波器的配置

图13 DDC功能测试连接图

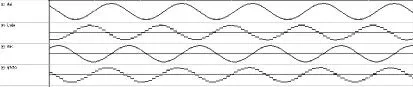

为观测方便,产生501 MHz的单频数据存放于测试ROM中,对DDC的输出结果实时进行监控,带宽(BW)20 MHz时输出结果如图14所示。

图14 DDC功能测试结果(BW=20 MHz)

输入信号频率为501 MHz,由理论分析可知,经DDC后输出信号频率为1 MHz。图14中,dai和daq为经过第一级平衡滤波器后的I路和Q路输出结果,idata和qdata为最终的结果,此时信号速率为20 MHz,对应图中波形每个周期有20个采样点。

4 结束语

介绍了一种运用FPGA设计基于多相滤波正交变换结构的数字下变频器的新方法,它能够较好地降低滤波器的阶数,同时运用FPGA内部IP核实现FIR滤波器以提高设计效率。通过改变软件设计改变数字下变频器的要求,具有较好的可扩展性与灵活性。

[1] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[2] 高志成,肖先赐.宽带数字下变频的一种高效实现结构[J].电子与信息学报,2001,23(3):255-260.

[3]WHITE S A.Applications of distributed arithmetic to digital signal processing:a tutorial review[J].IEEE ASSP Magazine,1989,6(3):6-19.

[4] 张希良.基于下频技术的软件无线电数字滤波器研究[D].济南:山东大学,2012.

[5] 刘瀛祺,金力军,陈吉锋.软件无线电中抽取滤波器的研究与FPGA实现[J].电子科技,2006(7):38-42.