基于SOPC的双目视频采集及显示系统设计

2013-02-13吕东欢欧阳宁

张 彤,吕东欢,欧阳宁

(桂林电子科技大学 信息与通信学院,广西 桂林541004)

责任编辑:魏雨博

立体视觉(Binocular Stereo Vision)是机器视觉研究的热点[1],双目视频信号的同步采集及实时显示是整个研究的前提和基础,但现阶段大部分多路视频采集卡都是基于分时复用或多路切换,不能真正实现双目视频的同步采集及实时显示[2-3]。针对这一现状,本文将SOPC(System on Programmable Chip,片上可编程系统)技术与FPGA(Field Programmable Gate Array,现场可编程门阵列)相结合,提出了一种以Nios II处理器为核心的软硬件协同设计的双目同步视频采集及实时显示系统,由DMA(Direct Memory Access,直接内存存取)控制器和Avalon-MM(Avalon Memory Map,Avalon存储器映射接口)模块组成的DTFC(Data Transfer Fast Channel,数据快速传输通道)完成视频数据采集和输出,破除处理器与外设在数据交换上的瓶颈,实现了真正的双目视频同步采集与实时显示。

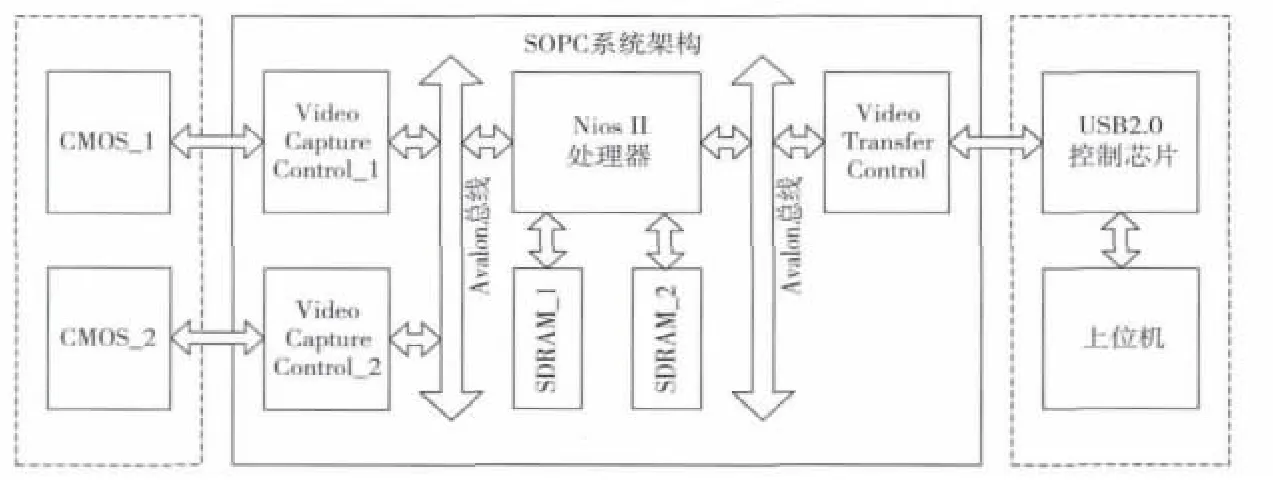

图1 系统结构框图

1 系统设计

系统结构框图如图1所示。

系统包括视频采集、视频输出、视频存储及核心控制模块。其中Video Capture Control_1和Video Capture Control_2为视频采集模块,按照CMOS传感器(CMOS_1,CMOS_2)的时序产生控制信号,采集视频图像数据,CMOS传感器采用2片OmniVision公司的OV7670 CAMERACHIP,通过串行成像控制总线(SCCB)配置传感器内寄存器,使其以30帧/秒(f/s)的速度平稳输出VGA(640×480)画质的视频流;Video Transfer Control为视频输出模块,通过状态机判断Slave FIFO的空满状态,将数据输出至USB2.0控制芯片CY7C68013A,CY7C68013A是一款Cypress公司生产的高性能USB接口微控制芯片,最高传输速率可达480 Mbit/s,Cypress公司还提供了完善的软件开发包,从而降低了上位机软件的开发难度,加快了开发进度。

视频存储及核心控制模块的核心是1片Altera公司的Cyclone IV系列FPGA(EP4CE15F17C8N),其具有15 408个LEs,同时具有516 096 bit的RAM,在保持低成本和低功耗的同时,大幅提升了在图像采集与处理方面的能力;为了降低系统复杂度,提高系统最高运行频率(fmax),应用Altera公司最新发布的流水桥架构(pipeline),将低速外设通过流水桥与高速处理器相连,使系统的工作时钟达到100 MHz以上;针对系统运行频率高和视频信号数据量大的特点,视频存储模块(SDRAM_1,SDRAM_2)配置了2片SAMSUNG公司型号为K4S561632H的256 Mbit同步动态随机存取内存器(Synchronous Dynamic Random Access Memory,SDRAM)作为SOPC系统的运行空间和图像缓存空间(Framer Buffer),实现数据的乒乓传输,实验证明,系统可以稳定运行在120 MHz;串行配置芯片EPCS16作为FPGA硬件系统和NiosII软件程序的存储空间,保证系统上电后即可运行。上述控制器均由Nios II软核自带的通用控制器实现,极大地简化系统的设计,同时提高了系统的通用性和可移植性。

上位机在EX-USB FX2开发套件的基础上结合OpenCV开发了视频实时显示软件。视频采集与视频传输模块均已Avalon-MM模块的形式集成在SOPC系统中,并与DMA控制器组成了数据快速传输通道,解决了双目视频系统在同步性与实时性上的难题。

2 系统硬件设计

2.1 视频采集模块设计

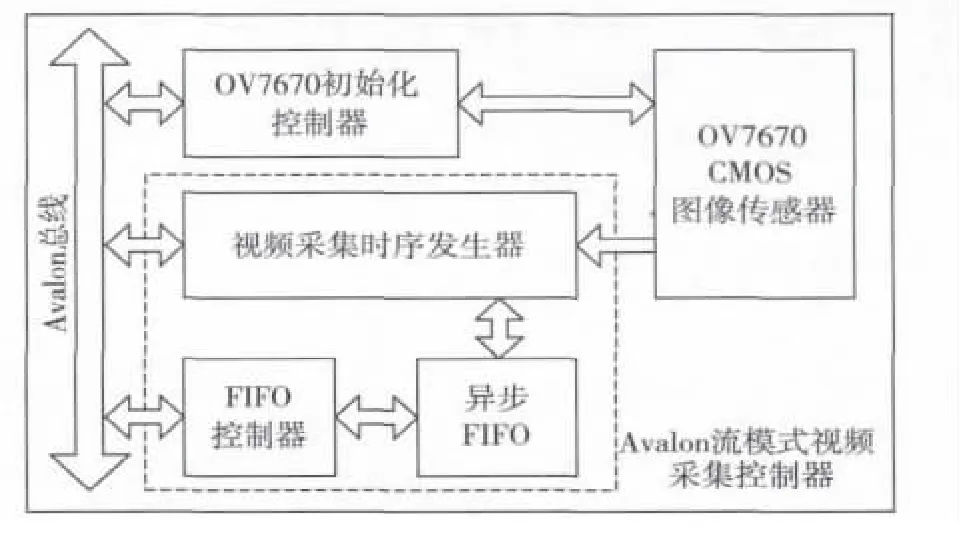

视频采集模块包括OV7670初始化控制器与Avalon流模式视频采集控制器,如图2所示,采集过程由Nios II处理器控制,处理器首先发出OV7670处理器初始化信号,对2片OV7670图像传感器进行初始化,在收到初始化成功信号后启动Avalon流模式视频采集控制器和对应的DMA控制器,将双路视频信号采集至指定的Framer Buffer,将FPGA的并行性与Nios II处理器的可编程性相结合,充分发挥了软硬件各自特点。

图2 视频采集模块

OV7670初始化控制器应用Verilog HDL硬件描述语言根据SCCB总线时序编写可综合的寄存器传输级(RTL)程序对OV7670摄像头进行初始化配置,所要配置的主要寄存器如表1所示[4]。

表1 OV7670关键寄存器配置参数

每路摄像头对应1个Avalon流模式视频采集控制器[5],Avalon流模式视频采集控制器主要包括信号同步与视频采集时序发生器两部分。由于摄像头的工作时钟(24 MHz)与Nios II系统的工作时钟(120 MHz)处在不同时钟域,为保证双路视频数据同步性,对单比特控制信号,如场(VSYNC)、行(HREF)、像素(PCLK)信号经过两级触发器串联同步器后方能使用。对多比特数据信号,如OV7670输入数据需要经过带格雷码地址发生器的异步FIFO后方能使用。经过上述处理后可以将系统的平均无故障时间(Mean Time Between Failures,MTBF)控制在可接受范围内,保证系统可靠性与同步性。

视频采集时序发生器主要完成RGB565格式的像素拼接和将视频数据流封装成帧的工作,OV7670数据输出时序如图3所示。OV7670的数据总线宽度为8 bit,1个RGB565格式像素(pixel)需要将2个时钟周期(cycle)的数据拼接在一起。2个视频采集时序发生器在收到处理器发来启动信号后,同时开始采集帧同步信号(VSYNT),在捕获该信号的下降沿后将两路视频数据以像素为单位(16 bit)按Avalon从模式端口时序送上Avalon总线,Avalon总线以系统时钟为工作时钟,将视频数据通过各自的DMA(DMA1,DMA2)控制器读至对应的Framer Buffer(Framer Buffer1/Framer Buffer3,Framer Buffer2/Framer Buffer4)。系统时钟为120 MHz,也就是说,流模式传输的最大带宽为240 Mbit/s,相较于PIO(Peripheral I/0)端口传输极大地提高了系统的吞吐量,可以满足VGA(640×480)画质,30 f/s视频实时采集的要求。像素拼接减少了Avalon总线对FIFO的读写次数,降低了后续数据处理复杂度,DMA控制器的引入即保证采集的同步性又破除了系统在数据传输上的瓶颈。

图3 OV7670数据输出时序

2.2 视频存储模块设计

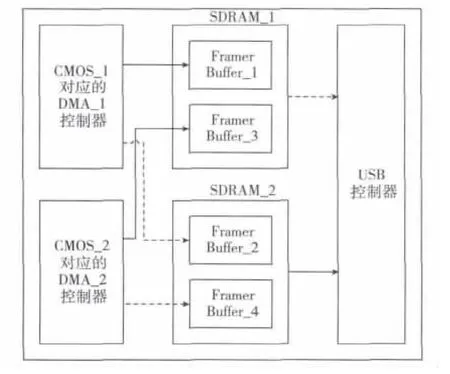

视频存储模块主要是以2片SDRAM为核心,配合与之对应的DMA控制器,实现数据的乒乓传输。SDRAM作为单口器件只能进行串行传输,无法同时对数据进行采集和输出,如果使用传统的乒乓传输设计方法,双目视频传输需要4片SDRAM,PCB布线难度极大。本设计应用SOPC在控制性上的优势,操作2组DMA控制器(DMA_1,DMA_2)配合2片SDRAM实现了双目视频数据的乒乓传输,数据流向如图4所示。

图4 视频数据流向图

Nios II处理器启动与双路视频采集模块对应的DMA_1和DMA_2控制器,将数据从异步FIFO读至SDRAM_1中缓存Framer Buffer,SDRAM_1可缓存1帧2路视频数据。同时,视频输出模块对应的DMA控制器将数据从SDRAM_2中读出并写入USB缓存中,通过USB芯片将视频数据发送到USB总线中。采集与输出同时进行,每采集完1帧数据之后,互换DMA的目标SDRAM,形成1次乒乓传输,这样将采集数据和传输数据同时进行,避免了串行传输的时间浪费,提高了系统响应速度的同时大幅降低了系统的硬件复杂度。

2.3 视频输出模块设计

视频输出模块包括异步FIFO缓存器与Avalon流模式视频输出控制器[6],如图5所示。由于系统时钟(120 MHz)高于USB芯片(CY7C68013A)时钟(48 MHz),所以加入异步FIFO缓存器暂存数据。根据视频信号数据流传输特点,权衡FPGA内资源与数据传输速度后,采用宽度为16 byte,深度为4 096 byte的异步FIFO作为缓存,并在控制模块中引入反压机制(Back Push),将异步FIFO的almost_full信号作为反压信号发送至DMA控制器,DMA控制器根据该信号终止或继续数据传输。

图5 视频输出模块

为了达到最高传输速率,将CY7C68013A设置为Slave FIFO从机模式。Avalon流模式视频输出控制器作为外部主控制器产生写FX2内部FIFO时序、握手信号和输出使能信号,其核心为一个有限状态机(Finite State Machine,FSM),如图6所示。

图6 视频输出状态机

状态转移过程如下:

Idle_State:视频输出模块收到Nios II处理器发来的输出启动信号,跳转至Initial_State,否则停留在Idle_State。

Initial_State:指向IN FIFO,激活FIFOADR[1∶0],跳转至Flag_State。

Flag_State:如果FIFO满标志位为0(FIFO不满),则跳转至Transf_State;否则停留在Flag_State。

Transf_State:激活SLWR,将数据送上总线,跳转至End_State。

End_State:检测是否将1帧视频数据传输完成,若完成则跳转至Idle_State,否则跳转至Flag_State。

视频输出模块在Nios II处理器发出启动信号,完成1帧2路视频信号输出后进入等待状态,整个过程自动完成,将处理器从繁重的输出传输中解放出来专注于系统控制,经实际测试,系统的输出速率可以达到40 MHz/s以上,可以满足上位机实时显示的要求。

3 系统软件设计

Nios II软件主要用于系统工作流程控制[7],合理配置DMA控制器,并配合视频采集模块和视频输出模块实现数据的高速传输,具体流程图7所示。

图7 SOPC软件流程图

DMA控制器的初始化是整个系统的关键,通过直接调用HAL层宏的方式提高软件的执行效率,初始化过程如图8所示,首先定义3个指向DMA控制器结构体的指针分别对应2路视频通道和1路USB输出通道,然后配置传输长度寄存器为1帧视频数据的数据量(640×480×2 byte),最后将2路视频通道的源地址指向对应Avalon流模式视频采集控制器的首地址(Avalon_OV7670_DMA_IP_0_BASE,Avalon_OV7670_DMA_IP_1_BASE),目的地址指向Framer Buffer的相应空间,USB输出通道的源地址指向Framer_Buffer的起始地址,目的地址指向Avalon流模式视频输出控制器的首地址(Avalon_USB_DMA_IP_0_BASE)。使用gcc编译的attribute技术将Framer Buffer_1和Framer Buffer_3声明为SDRAM_1上的2个数组空间,相对应的将Framer Buffer_2和Framer Buffer_4声明为SDRAM_2上的2个数组空间,后续每传输完1帧数据将视频采集模块与视频输出模块DMA控制器的目的地址互换就可以实现数据的乒乓传输,充分发挥了SOPC系统在可编程性上的优势。

图8 DMA控制器初始化流程图

4 系统测试

系统实现了双路视频信号同步采集并在上位机实时显示,图像传感器OV7670工作时钟为24 MHz,采集速度达到30 f/s,设置图像数据输出尺寸为VGA模式(640×480),输出格式为RGB565。经测试视频显示清晰流畅,两路信号高度同步,如图9所示,相同颜色条格处在图像的相同位置,图10为系统对同一棋盘格试验板的采集结果。

5 结论

本文介绍了一种以Nios II处理器为核心软硬件协同设计的双目同步视频采集及显示SOPC系统的设计实例。详细描述了各功能模块的设计方法,给出了双路视频同步采集、大数据快速传输及信号跨异步时钟域等视频采集和FPGA应用方面热点与难点问题的处理方法。利用视频采集控制器、视频输出控制器及DMA控制器组成的数据传输快速通道,以2片SDRAM实现了双目视频数据的乒乓传输(普通方式需4片SDRAM),极大地降低了系统的硬件复杂度。通过仿真验证和实际测试,该系统在同步性、实时性及稳定性上达到预期效果。后续利用SOPC技术在通用性和可编程性上的优势,可以进一步提高系统的清晰度和帧率,或添加图像处理协处理器实现图像标定和图像融合等高级算法。

[1]LIN Lili,ZHOU Wenhui.Binocular stereo vision synchronous acquisition technique based on FPGA[C]//Proc.2010 2nd International Workshop on Database Technology and Applications.Wuhan,China:IEEE Press,2011:22-28.

[2]刘攀,王红亮,孟令军.基于FPGA的数字图像采集存储系统的设计[J].电视技术,2010,34(6):32-34.

[3]吕苏谊,许江淳,李玉惠.基于SOPC的双摄像头视频采集系统设计[J].计算机科学,2010,37(7A):171-210.

[4]李德明,韩剑,江国强.基于OV7670的图像采集及显示系统设计[J].仪器仪表学报,2010(8):30-33.

[5]Altera Corporation.Avalon interface specifications[EB/OL].[2013-02-01].http://wenku.baidu.com/view/2be0303f0912a21614792980.html.

[6]吴磊,郭超平,申世涛.基于CY7C68013与FPGA的便携式数据采集系统[J].计算机应用,2012,32(S1):164-166.

[7]张显才,李向东,丁国宁,等.Nios II系统中DMA控制器的原理及应用[J].现代电子技术,2012,35(6):19-21.