H.264解码器帧内预测模块的优化

2013-02-13王光玮梁利平

王光玮,梁利平

(中国科学院 微电子研究所,北京100029)

责任编辑:时 雯

1 帧内预测

一直以来,视频信息以其直观性、高效性等优点而受到人们的青睐。但是视频信息包含的信息量太大,若要广泛应用,必须解决压缩与编码的问题。为此,国际标准化组织和视频图像专家组等组织制定了一系列的视频编解码和压缩的标准,其中由ITU-T(国际电信联盟组织)和ISO(国际标准化组织)联合推出的H.264视频编解码压缩标准具有突出的压缩效率[1],得到了广泛的认可和应用。

H.264采用了帧内预测、1/4像素插值、多参考帧预测、环路滤波等多种新技术,获得了优越的压缩性能[2]。但是,这些新技术在提高编码压缩效率的同时,提高了计算复杂度,对硬件平台提出了更高的要求。因此,针对H.264标准在硬件资源相对紧张的嵌入式设备上的应用,业界提出了多种有效的优化方法。如基于VLSI硬件设计加速H.264解码计算过程[3];用特定平台提供的SIMD指令进行数据的向量处理[4];或者针对H.264解码流程中一个或多个模块进行结构或者算法上的优化,提高执行效率[5-7]。

以上几种方法中,硬件加速的方法性能比较高,但是开发周期长,成本高,且不灵活,不利于升级;用SIMD指令虽然可以加速计算过程,但是和平台相关性很大,可移植性比较差。相对于前两种优化方法,后一种方案比较灵活,没有平台的限制,是一种通用的优化方法。

本文提出的优化方法属于最后一种,是对帧内预测模块提出的一种通用的优化方法。通过对H.264解码过程中帧内预测原理进行深入的分析,针对此模块中处理器与片外存储空间(SDRAM)数据交互频繁、4×4亮度块的预测模式计算复杂度较高的特点,对帧内预测模块采取了两方面的优化措施。其一是通过结合环路滤波的结构,去除了目前常用结构中片上存储空间(SRAM)的冗余存储,节省了解码所需的片上存储空间;第二个优化措施是通过预先在片上空间(SRAM)存储相邻4×4亮度块的帧内预测模式,简化4×4亮度块帧内预测模式的获取过程。通过以上两种优化措施,节省了解码过程片上存储空间需求、简化了4×4亮度块帧内预测模式的获取过程,并且减少了处理器与片外存储空间(SDRAM)的数据交互次数,大大提高了解码器的执行效率和解码性能。

2 帧内预测模块优化方案

帧内预测是H.264采用的一项新技术,利用一帧图像的空间相关性,由邻近块的信息来预测当前块的信息,进一步提高了压缩效率。这种预测来自以下两个方面:像素的预测和4×4亮度块预测模式的预测。本文的两个优化措施分别针对这两个方面。

2.1 片上冗余存储的优化

片上空间冗余存储的优化是针对像素的预测过程进行的优化。H.264帧内预测模式下,当前块的像素预测值是由邻近块的像素根据不同的预测模式预测得到。

H.264支持9种4×4块、4种16×16块的亮度预测模式和4种8×8块的色度预测模式[7],如图1所示。其中8×8色度块的预测模式和16×16的亮度块预测模式类似,因此图1并未重复给出。

图1 亮度块帧内预测模式

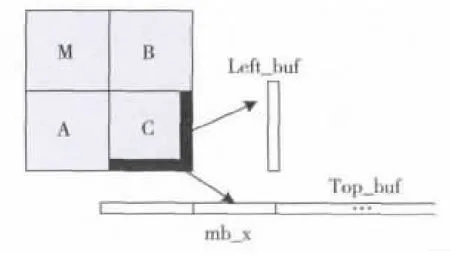

从图1中可以看出,当前块的像素预测可能会用到左方宏块最右一列、上方宏块最下边一行的像素值作为参考像素,且参考像素值必须为环路滤波前的像素值。目前普遍采用的处理方法是:重建宏块滤波前,最右一列和最下面一行的数据被分别保存于两个片上buffer中,如图2所示。后续邻近宏块为帧内预测类型时,直接读取两个片上buffer中的参考像素值进行帧内预测。

图2 常用的帧内预测存储结构

这种结构虽然可以在一定程度上减少处理器到片外空间读取参考像素的次数,但事实上这两个buffer中的数据是片上的冗余信息。本文结合环路滤波的结构,取消了这两个片上buffer,直接在环路滤波的缓存buffer中读取数据,去除了这部分冗余数据的存储。这里有必要先简单介绍一下环路滤波的结构。

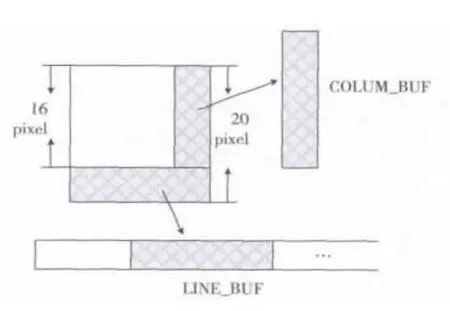

常用的以宏块为单位的环路滤波结构中[8],也存在两个类似的片上buffer来暂存相邻块的数据,不同的是这两个buffer存储的数据是环路滤波后的像素值。如图3所示,当一个宏块滤波结束后,把最右边四列和最下边四行像素值分别存储到片上LINE_BUF和LEFT_BUF两个buffer中,以便右边宏块和下方宏块滤波使用。

图3 环路滤波存储结构

从图3可以看出,这两个buffer同样包含了一个宏块最右边一列和最下面一行的像素值。通常认为这两个buffer中的像素值为滤波后的像素,因此不能被帧内预测模块利用。事实上,深入分析环路滤波过程可知,这两个buffer中帧内预测所用到的部分像素值在滤波前后并不会改变。图4a中实线是一个宏块中需要滤波的边界,图4b给出了在最强滤波强度下,一条边界两边可能改变的像素值(图中深色的像素)。从图4可以看出,一个宏块中最右一列和最下边一行的像素值在滤波前后是不改变的。因此完全可以将帧内预测模块中的两个buffer去掉,当需要左方和上方块的像素值作参考像素时,直接到环路滤波这两个buffer中读取相应的数据即可。这一优化措施不但去掉了片上的冗余存储,释放的空间可以将片外更有意义、使用频繁的数据存储到片上空间,而且减少了帧内预测模块中未滤波像素保存这一步骤,进一步提高解码性能。

图4 环路滤波原理

2.2 预测模式获取过程的优化

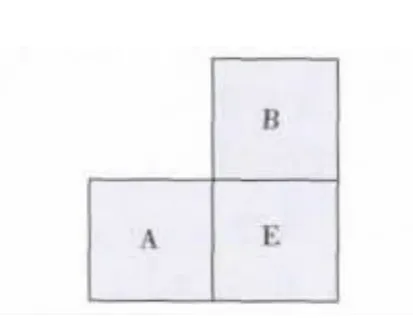

帧内预测的另一个重要步骤是每个4×4亮度块本身预测模式的获取。为了提高压缩效率,宏块头信息只给出16×16亮度块和色度块的预测模式,4×4亮度块的预测模式需要解码器根据邻近块的相关性计算得出。如图5所示,当前块E与左方块A和上方块B的预测模式有很大的相关性。

图5 预测模式有相关性的4×4块

4×4块预测模式的预测过程如图6所示,当前块E的预测模式由最可能预测模式和参数prev_intra4×4_pred_mode(以下简称参数1)及参数rem_intra4×4_pred_mode(以下简称参数2)来共同决定。最可能的预测模式为左方块A和上方块B的预测模式的最小值。若块A或块B为非帧内4×4预测模式,则相应的预测模式置为2(DC预测模式)。如图6所示,根据参数1和参数2的值对最可能模式进行修正,就得到当前块E的预测模式。

图6 4×4块预测模式的获取过程

由以上分析可知,每个4×4亮度块预测模式的获取,处理器需要频繁地在片外存储空间读取邻近块的信息并进行判断等步骤。当图像带有大量的细节,随着4×4块数目的增多,这部分的开销会陡增,降低解码性能。可见对这一部分的优化是十分必要的。

本文采取了在预测当前块模式之前就预先判断并存储相邻块的信息的优化措施。首先新增两个片上buffer:top_model_buf和left_model_buf。top_model_buf用来存储当前块上方整个4×4块行中每个4×4块的预测模式,left_model_buf用来存储左方4×4块的预测模式。

如图7所示,当前块E的上一行子块在解码过程中,同时把此子块预测模式的值存入top_model_buf中,若此块不是帧内4×4模式,则在top_model_buf的对应位置存入2(DC预测模式)。left_model_buf存储最近解码子块的预测模式,同样,若这个子块为非4×4帧内预测模式,则在buffer存储2。如此一来,top_model_buf类似一个循环存储结构,解码一个宏块行才全部更新一次,保存着当前解码行上一4×4子块行全部的预测模式。当前块E只需要到buffer的对应位置上读取相邻块的信息求最小值即可得到最可能预测模式。

图7 相邻4×4块预测模式的存储

下面来分析新增的两个buffer所需要的空间开销。因为每个4×4子块有9种预测模式,因此只需要4 bit便可以存储一个子块的预测模式。1个宏块中只需要存储最下面的4个4×4子块,因此1个宏块需要的比特数为4×4=16 bit。如果存储1个宏块最下边一行的像素,则需要16×8=128 bit。因此,相对于未优化前存储最下边一行像素的top_buf,这个buffer的大小仅为原来的1/8。可见本文的优化方法尽管将更多的信息存储到了片上存储空间,不但没有增加片上存储需求,反而释放了一定大小的片上存储空间,这对硬件资源相对宝贵的嵌入式系统来说是十分有意义的。

优化后的4×4块预测模式的获取流程如图8所示,相比于优化前的流程图6,复杂度大大降低。

图8 优化后的4×4块预测模式的获取过程

3 实验结果

本文将优化前后的解码程序分别在IME-Diamond仿真平台上做了验证,对比结果如表1所示。IME-Diamond仿真平台是32位定点处理器IME-Diamond的仿真软件,片上存储空间为128 kbyte,该软件可以精确统计每个模块消耗的周期数。测试所用的码流是由JM编码器产生的标准码流,用了4组300帧CIF格式的测试码流。表1分别给出优化前后帧内预测模块消耗的周期数,并给出了对比结果。

从表1可以看出,采取本文提出的优化措施对程序进行优化后,帧内预测模块消耗的平均周期数大大减少,相对于优化前平均提高了13%左右。

表1 优化前后帧内预测模块性能对比

4 结论

本文对H.264帧内预测模块做了两方面的优化,一是结合环路滤波的结构,却除了片上冗余信息的存储,在降低片上空间需求的同时简化了参考像素的存储流程;二是对4×4亮度块的预测模式获取过程的优化,在解码相邻信息块的同时对这些块的预测模式进行判断和存储,降低预测模式的获取的复杂度。通过这两种优化方法,在降低片上存储空间的前提下简化了帧内预测模式的处理流程,减少了处理器和片外数据的交互次数,提高了解码性能,尤其对于包含大量细节的图像,优化效果更加明显。

[1]Joint Video Team.ITU-T Rec.H.264 and ISO/IEC 14496-10 AVC,Draft ITU-T recommendation and final draft international standard of joint video specification[S].2003.

[2]WIEGAND T,SULLIVAN G,BGONTEDAARD G,et al.Overview of the H.264/AVC video coding standard[J].IEEE Trans.Circuits and Systems for Video Technology,2007,13(7):560-576.

[3]ZHANG N,LI M,WU W.High performance and efficient bandwidth motion compensation vlsi design for H.264/AVC decoder[C]//Proc.ICSICT 2006.[S.l.]:IEEE Press,2006:1896–1898.

[4]陈梅芳.基于TMS320DM642的H.264解码器优化[J].现代电子技术,2006(3):112-115.

[5]袁晓雷,魏江,张鹏.嵌入式平台H.264软件解码器的优化[J].电视技术,2010,34(5):36-39.

[6]任李悦,唐宁,滕舟.基于H.264解码器的软件优化[J].电子设计工程,2009,17(12):104-108.

[7]姜峰.基于DSP的H.264解码器运动补偿模块的优化[J].微电子学与计算机,2012,29(10):86-88.

[8]毕厚杰.新一代视频压缩编码标准—H.264/AVC[M].北京:人民邮电出版社,2005:83-89.

[9]胡宏华,谌德荣.基于DSP的H.264解码器优化设计[J].中北大学学报:自然科学版,2011,32(6):763-767.