基于NiosⅡ的图像采集系统设计

2013-01-31孟令军尹维汉彭晴晴

孟令军,尹维汉,彭晴晴,李 柱

(中北大学 电子测试技术国家重点实验室仪器科学与动态测试教育部重点实验室,山西 太原030051)

NiosⅡ是Altera特有的基于通用FPGA构架的软CPU内核。和传统的单片机及单片机系统相比,NiosⅡ处理器具有速度快、高度的灵活性和可配置性及设计流程简单等优点[1-2]。

图像采集是图像信号处理系统的前端部分。图像采集系统在当今工业、军事、农业和医学等领域都有着极其广泛的应用[3]。文中提出了一种基于NiosⅡ处理器的图像采集系统的实现方法。该方法经过适当修改可应用于对多种场合的图像采集。

1 硬件平台设计

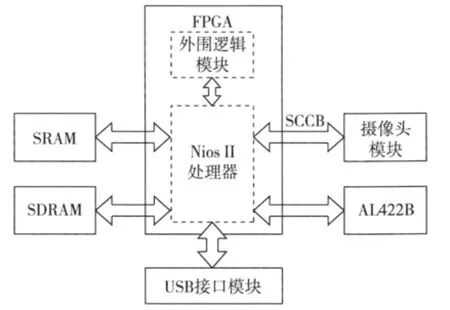

该图像采集系统硬件电路主要由FPGA模块、SRAM、SDRAM、OV7725摄像头、AL422B缓存、USB接口模块等部分组成,各模块之间的关系如图1所示。系统中FPGA采用Altera公司CycloneⅡ系列的EP2C35F484C8N芯片,该芯片资源丰富,可方便系统的扩展,系统软核在FPGA芯片上构建,部分外围逻辑单元使用FPGA芯片的IP核或用VHDL程序设计;摄像头模块采用OmmiVision公司生产的图像传感器OV7725,该图像传感器体积小,工作电压低,能够提供单片VGA摄像头和影像处理器的所有功能,通过SCCB总线控制;AL422B是由AVERLOGIC公司开发的一款缓存芯片,在系统中作为摄像头模块数据FIFO;USB接口模块基于FT245芯片设计,为系统与上位机的接口,用于接收计算机指令及向计算机上传图像数据;此外,系统硬件还包括外部SRAM及SDRAM存储器模块等。

图1 系统总体框图

2 SOPC设计

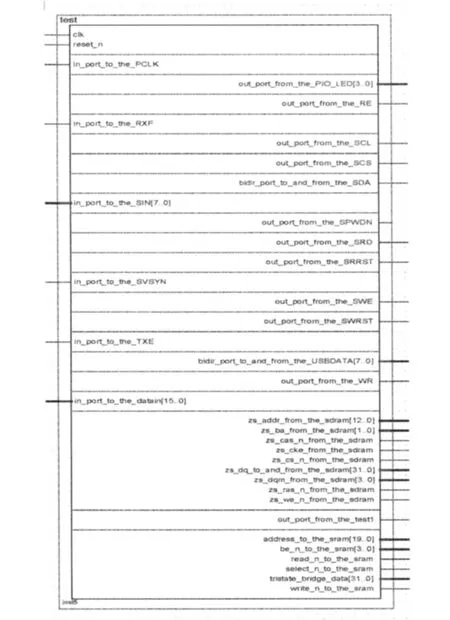

该系统SOPC部分主要包括NiosⅡ处理器模块、PLL模块及系统复位控制模块等,其中Altera公司的NiosⅡ是基于RISC架构的嵌入式处理器软内核,是系统的SOPC部分的核心模块。根据该系统要实现的功能,选择了合适的CPU和外部设备,构建了系统的NiosⅡ处理器模块,如图2所示,主要包括CPU核及以下几种外设:OV7725摄像头,SCCB控制接口,AL422B图像数据接口,SRAM、SDRAM、USB接口等。

图2 NiosⅡ处理器结构图(截图)

3 NiosⅡ程序设计

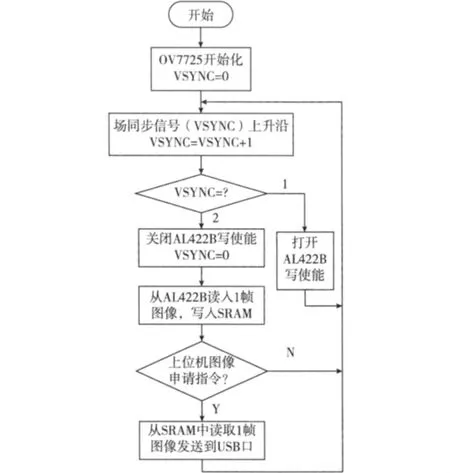

NiosⅡ程序采用C语言编写,为系统核心控制程序,主要功能包括:摄像头的初始化、图像数据的采集、图像数据的存储、上位机指令的接收、图像数据的上传等。主程序流程图如图3所示,系统上电后,先通过SCCB总线完成对OV7725摄像头的初始化,帧计数VSYNC赋初值0;主程序接收由据摄像头场同步信号(VSYNC)上升沿产生的中断请求,帧计数VSYNC值加1;当帧计数VSYNC值为1时,主程序打开AL422B缓存的写使能,等待摄像头场同步信号中断请求,当中断请求到来时,帧计数VSYNC值加1;当帧计数VSYNC值为2时,主程序关闭AL422B缓存的写使能、帧计数VSYNC赋值0,同时主程序从AL422B缓存中读取1帧图像数据,并保存到SRAM中;判断USB口是否有指令数据写入,即上位机是否发送图像数据请求指令,如果有则从SRAM中读取最近写人的1帧图像数据并通过USB口发送给上位机显示,发送完毕后主程序返回等待场同步信号的中断请求,并循环执行对摄像头图像数据的采集。对主程序及上位机做适当修改,该系统便可实现对图像数据的实时显示;根据需要也可在主程序中加入一定的图像处理功能。

图3 NiosⅡ主程序流程图

4 上位机软件设计

上位机软件是该图像采集系统的控制软件,为人机对话接口。上位机功能主要包括:通过USB口向NiosⅡ处理器发送图像申请指令来获取系统所采集到的图像数据,显示图像,将图像数据保存到计算机硬盘中等。上位机软件使用可视化程序设计语言VB所设计,能够在Windows 7/XP操作系统上运行[4]。通过对该软件的功能扩展可实现图像数据的实时显示,并可实现较为复杂的图像数据处理功能。

5 测试结果分析

通过实际测试,系统各项性能指标均达到了设计目标要求,系统测试结果如图4所示。

该图像采集系统可扩展性强,在不修改系统硬件的前提下,只需对NiosⅡ主程序及上位机做适当修改,便可使该系统具有一定的图像处理功能或作为不同应用系统的前端图像采集子系统。

图4 系统测试结果(截图)

[1]赵贻玖,王厚军,戴志坚.基于NIOS处理器的数字示波表设计[J].仪器仪表学报,2006,27(6):1484-1485.

[2]蔡伟纲.NiosⅡ软件架构解析[M].西安:西安电子科技大学出版社,2007.

[3]杨晓,王红亮.基于FPGA控制的图像采集和存储系统[J].火力与指挥控制,2010,35(9):124-126.

[4]龚敬,孟令军,严帅,等.多通道数字脉冲发生器的SoPC实现[J].电视技术,2011,35(15):71-73.