基于动态调控的接入控制器内存调度策略

2013-01-31李广成

肖 洋,李广成,杜 勇

(1.武汉邮电科学研究院,湖北 武汉430074;2.武汉烽火国际技术有限责任公司,湖北 武汉430074;3.武汉虹信通信技术有限责任公司,湖北 武汉430074)

随着智能手机、平板电脑等接入设备的普及,用户上网更加便捷,致使无线用户数量不断增加,网络中的用户流量也在不断攀升。在现有普遍采用的集中式WLAN的网络环境中,数据处理的集中点位于接入控制器中,包括用户数据处理、转发和对用户、接入点的管理数据的处理。对接入控制器数据处理的速度提出了很高的要求。在处理数据的时候,必然涉及到对内存的申请、使用、传递和释放的过程。这个过程的好坏直接决定了系统性能的高低。

由于接入控制器对内存的使用比较频繁,内存分配和释放的效率对整个系统的性能有直接的影响;在接入控制器的系统中,内存交互申请和内存释放的过程有可能造成一定量的内存泄露情况,一旦出现内存泄露,频繁的内存申请释放操作又会产生大量内存碎片,从而极大降低系统整体性能。同时,由于大量的模块分布在不同的线程之中同时运转,内存调度情况不容易掌控,系统整体内存使用情况以及各个线程之间的内存使用情况也不易把控。因此,需要提出一种内存调度策略,既能够满足内存的高效回收机制,又能够有效地管理系统内存空间、掌握各个线程中内存分配的信息。

1 接入控制器内存调度总体结构及功能

现有通用的接入控制器主要采用集中式组网方式,接入控制器负责管理AP以及STA,负责数据的快速转发,其基本模块组成如图1所示。由报文快速转发模块、用户管理模块、业务管理模块以及系统管理维护模块构成[1]。其中,报文快速转发模块由报文接收/发送和报文处理模块组成,负责对接入控制器内外报文进行筛选分类,并根据网络协议规则转发到相应模块或网络接口上,对模块性能的要求较高;用户管理模块和业务管理模块分别负责对接入用户以及AP的状态等上下文进行管理维护。系统管理维护模块是对整个接入控制器系统进行统一管理与状态监控的模块。根据这三大模块的构成,可以按照数据处理分为三大部分:报文快速转发部分、系统线程内处理部分以及系统线程间处理部分。

快速转发部分指从网络中收到的数据增减头部隧道封装并快速转发出去,该过程会频繁地为数据分配内存,并将其需要的数据拷贝数次,处理后输出。

图1 AC的多板构架及模块组成

系统线程间数据处理是指在系统线程间的数据处理,涉及到线程间的通信机制,以及内存相互访问和调度。

系统线程内处理数据部分指在系统线程内部处理的数据,通常为线程私用的数据,包括用户上下文、WTP上下文等,申请释放的频率相对较低。

针对接入控制器以上几种内存使用的特点,可以将接入控制器内存调度分层3个层次:Dynamic Smart Preallocation(DSPA),Static Pre-allocation(SPA),Dynamic Pre-allocation(DPA)。

DSPA适用于快速转发功能,实现预分配内存,并对分配内存大小进行预估,不足的时候就按照一定规律进行链式增加,优化分配机制,在处理的过程中实现一次拷贝多次使用。

SPA适用于线程间的内存分配。实现预分配内存、大小固定、匹配内存空间[2]。

DPA适用于线程内部处理的内存使用,实现按需分配,匹配内存空间,会有一些内存空间的浪费。

以上3种层次的内存分配方式都能够实现内存快速调度,对应用每次分配以及释放动作的代码段进行定位,确认内存泄露与否,以避免内存碎片产生。在接入控制器系统发生异常的时候,应用定位问题具有方便快速定位的优势。

2 接入控制器内存调度设计原理

基于以上功能需求,对AC内存调度的设计分为内存分配层和内存管理层2个层次,其中内存分配层提供内存分配释放,为上层应用提供快速稳定的存储基本服务,而内存管理就在内存分配之后,对内存信息进行统一管理,并对异常内存分配或释放进行记录。下面分别对两个层次的设计原理进行详细的介绍。

2.1 接入控制器内存分配设计原理

在AC线程内部及线程间,均采用内存池阵列的方式对内存进行分配。内存池阵列中有数个内存池,每个内存池中内存大小相同[3]。

SPA内存分配方式使用于线程之间的大小固定的应用环境下,当应用的某一种相同的数据结构数量较大,使用较为频繁的时候,如ARP表项、用户上下文、AP上下文等,在使用的时候,只需创建适合其使用固定大小的内存池,并每次从指定的内存池中分配释放内存即可,其时间复杂度为O(1)。效率极高,但是使用环境也有限制,而且需要应用对该内存池的大小进行设定。

在AC的报文快速转发模块中,一般会从网络接口接收数据包。每当收到数据包,就会为这些数据包分配内存。为了实现零拷贝,每次从DSPA内存池中,分配1块内存,该内存结构如图2所示。是一种缓冲链式结构,由1个DSPA描述符以及DSPA内存块组成。上层应用需要为其增加或减少数据头,就只用将指针向前偏移一部分,并填充相应的数据部分即可。若需要在该数据包后继续填充数据,只需继续增加1个DSPA内存块,并将之前的DSPA用指针指向新增的内存块,保证关联关系。应用处理之后,将其转到发送端口,将数据转出。这就是数据的快速转发过程。由于每个DSPA内存块都是固定大小,在分配内存的过程中,适合于高效数据快速转发,而在其他环境中不够灵活。

图2 DSPA内存分配结构

其中,在DSPA的工作流程图如图3所示。

图3 DSPA内存分配流程图

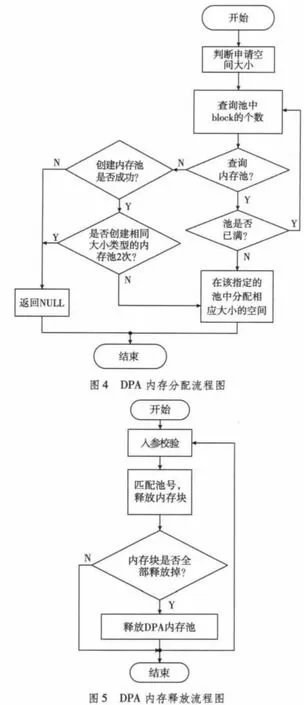

DPA分配内存的模式为根据应用申请的内存大小,与2n进行比较(2n为计算机存储特性的一个参考值),匹配需要申请的内存池。若该内存池的内存分配完了,就会动态分配新的大小相同的内存池,为应用继续提供内存。其中在DPA的工作流程图如图4、图5所示。

2.2 接入控制器内存管理设计原理

在以上3种工作模式下,分配和释放内存的时候都会为每个内存打上标签,分别记录分配内存的函数、文件、行号、及分配的时间。每个内存都有1个内存使用标志位,用于表示该内存使用情况[4-5]。其中-1表示从未使用过,0表示被释放,1表示被分配。为内存管理模块其配置命令行,在调试工作模式下,提供分析问题的帮助。

1)为用户分配内存提供定位信息

当用户分配内存的时候,就会将内存分配的情况记录下来,并与内存池的上下文绑定。已分配的内存块会将内存使用标志位置为1。

2)为用户释放内存提供定位信息

当用户释放内存的时候,就会将内存释放的情况记录下来,并与内存池的上下文绑定。并且可以和1中的信息进行比对,判断内存是否存在内存泄露。

3)为用户非法内存操作提供信息

(1)double free

在程序员编程过程中,某一个内存用于存储上下文,共用于数个线程中,在释放的过程中可能存在重复释放的情况。如果在调用malloc-free函数的时候,程序就会挂掉,并留下double free的信息。本文会根据flag位来判断,如果flag为0,应用又释放一次内存,即发生double free。在内存管理中会记录double free的错误,并保证程序不会因此异常退出。

(2)释放非法地址内存

在程序员编程过程中,释放非法的内存地址,如未对齐的内存块地址、空地址或不存在于内存池中,避免造成程序的异常退出。其调用释放函数的跟踪信息都会被记录到日志信息中,便于后续定位处理问题。

4)为可能出现内存泄露的内存提供信息

在程序员编程过程中,或多或少都会出现一些内存泄露的问题,通过标志位以及调用信息可以容易地定位到内存块的状态,在正常的内存使用中,大部分的内存都是不断地分配然后释放。因此,在每个内存分配的时候中,就会在内存块中增加1个时间戳信息,如果1个内存块在运行时长大于1周的时候还没有被释放,就会将这个内存块的地址调用信息记录到日志信息中,便于程序员定位分析。

3 内存调度运行结果

根据以上内存调度的分析设计,通过在Linux C下实现内存调度方法。现从内存调度功能和性能2个方面来验证本文设计方案。

3.1 内存调度功能测试

内存调度功能测试即对内存管理的测试。在实际Linux系统中只能通过系统的命令行查看整个系统以及每个进程的内存使用情况。通过系统的接口对程序的分析不能有很大的帮助,如图6所示。

图6 系统对内存使用情况统计(截图)

基于内存调度对内存的管理,可以清晰地打印出内存 的使用情况,其实现如图7~图10所示。

3.2 内存调度性能测试

内存调度性能测试即对内存分配释放的性能的一个测试。在内存调度过程中,测试的环境为mips构架,CPU为Cavium Octeon CN5650,内存为8 Gbit。将本内存调度与直接调用系统API malloc/free函数接口测试对比。结果如表1所示。

通过对比,可以清晰地看出通过内存池调度的内存通过空间换取更快的分配释放时间,提供了更加高效的内存分配机制。

表1 内存性能对比测试 μs

4 结语

本文设计的内存调度方式是适用于当前各种构架的接入控制器底层的一种内存调度策略。在以SPA,DSPA,SPA三种层次的内存分配方式上为上层应用提供高速可靠的内存分配策略,与此同时能够定位内存调用模块以及内存泄露问题,避免内存碎片的产生导致系统性能的降低,大大增加接入控制器在大流量多用户的情况下的运行性能以及稳定性。

[1]STEVENS W R.Unix Network Programming[M].Englewood Cliff:Prentice Hall,1990.

[2]MCKEE S,KLENKE R,WRIGHT K,et al.Smarter Memory Improving Bandwidth for Streamed References[J].IEEE Computer,1998,31(7):51-63.

[3]顾胜元.嵌入式实时动态内存管理机制[J].计算机工程,2009(20):1-3.

[4]JAMES F,KEITH W.Computer Networking:A Top-Down Approach[M].5th ed.New Jersey:Addison Wesley,2010.

[5]SCHUMANN R C.Design of the 21174 Memory Controller for Digital Personal Workstations[J].Digital Technical Journal,1997,9(2):57-70.