针对AES加密算法的研究及其FPGA实现

2013-01-31顾美康孙凯民

王 亮,顾美康,孙凯民

(上海师范大学 通信与信息系统学院,上海200234)

在信息化高速发展的时代,网络不仅给人们的生活带来了诸多便利,也推动了航天、军事,商务领域的不断进步。因此,信息安全尤其是在数据存储和传输方面的数据安全尤为重要。数据加密技术在数据安全中起着至关重要的作用,它保护敏感信息免受来自外界的恶意攻击,使数据不被篡改、盗取[1]。

国际上现行的数据加密标准是AES加密标准,又称Rijndael算法,它取代了DES和3DES,成为21世纪保护信息安全的新一代加密标准[2-3],并在各个领域得到广泛应用,如智能存储卡、高性能的数据服务器、无限网络传感器等。

本文针对AES加密算法进行了研究,通过分析其算法结构和加密原理,采用Nios II CPU的SOPC集成实现方式,基于FPGA设计出了具有加密和解密功能的、密钥可配置的、资源利用和吞吐量都十分理想的SOPC加密系统。

1 Rijndael算法的简要概述

AES是一个迭代的对称分组密码[4]。它需要一个128 bit的数据块作为输入,并执行在此分组内的轮变换。AES-Rijndael的算法是在“状态”中进行的。

状态是一个两维的字节数组,由4行Nb列组成,其中,Nb是除以32的分组长度。在AES算法中,所有字节表示为有限域GF(28)上的元素,使用多项式来表示。在有限域上的数学运算与那些有数学字符表示的运算不同。通过一个模2(一个XOR操作)实现两个多项式的相加。相对应的,有限域元素上的减法也是如此。

此外,在GF(28)上的乘法是一个8次幂的多项式乘法。AES算法指定一个不可约多项式,没有简单的操作可以在字节级上实现乘法。算法的轮数依赖于密钥的大小和分组的大小,由表1所示。所产生的轮数(Nr)由以下公式所得:Nr=(密钥长度(位))/32+6。在设计中,建议使用128 bit的密钥和密码的大小,因此,需要10个回合[5]。

表1 密钥和分组大小

1.1 整体结构

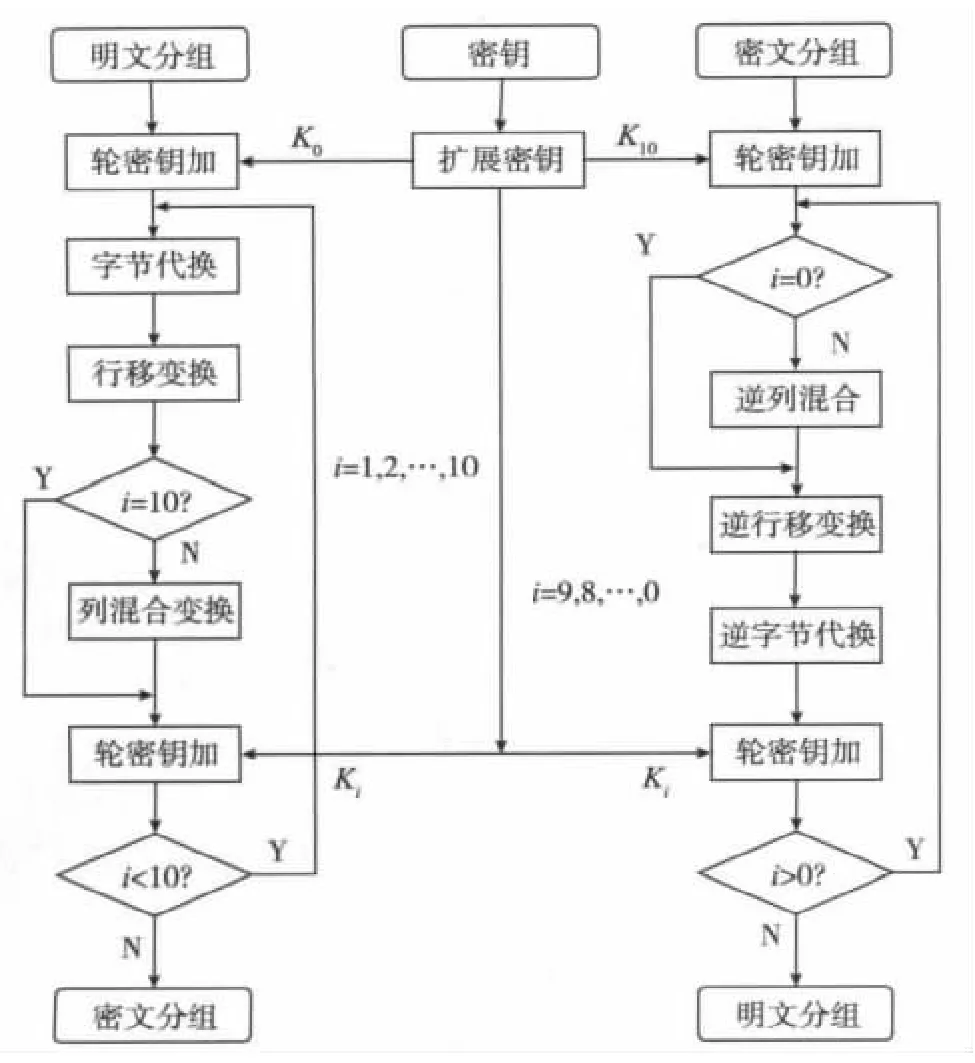

AES算法的整体结构如图1所示。解密结构与加密结构具有完全相同的变换序列结构。此功能可以更有效地实施联合加密/解密。

在标准的AES算法中,有4个步骤,即字节代换、行移位变换列、列混合变换及密钥加法[6]。

1)字节代换是一个非线性的字节取代变换独立的作用于的每一个字节,用替换表(S盒)来实现,其中S盒是可逆的。

2)移行变换作用于状态的最后三行中的字节进行字节循环移位,每一行的偏移量不同。第一行不移位。

3)列混合变换混合加密列上的状态,在每列中使用线性变换,结合行位移变换。

图1 AES算法的整体结构

4)密钥加法把每个字节的状态与每一轮的密钥相结合,每个循环密钥来自密钥编排。

2 AES加密系统FPGA设计与实现

2.1 系统架构

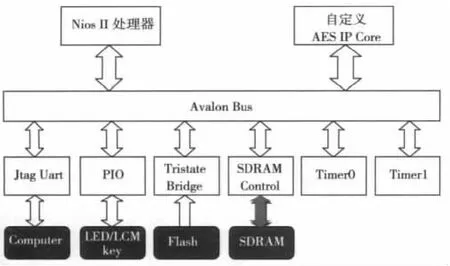

本设计通过在FPGA中嵌入微控制处理单元Nios II来实现对整个系统的控制,定制了32位Nios II CPU软核,并将定制的软核连接到Avalon总线上,与此同时,将Jtag Uart、SDRAM Controller、PIO等必要的外设和CPU一起集成在芯片上,使系统的规模得到简化,实现了On Chip System,得到了一个可靠安全、高效并且可灵活配置的实时加解密系统。本设计的SOPC系统架构如图2所示。

图2 SOPC系统框架图

2.2 自定义AES IP Core的设计

本系统根据AES加密算法的轮变换步骤确定AES IP Core的设计过程,把AES IP Core作为顶层,根据功能划分子模块:字节代换模块(SubBytes)、行移变换模块(ShiftRows)、列混合变换模块(MixColumns)、密钥加模块(AddKey)、密钥扩展模块(KeyExpansion)、多路复用模块(AddKeyMux)和有限状态机模块(Fine State Machine)。其中,有限状态机模块和多路复用模块为轮变换控制模块。IP Core设计模块结构如图3所示。

图3 IP Core设计模块结构图

其中控制信号有:时钟信号(Clk)、复位信号(Reset)、使能信号(Enable)、功能片选信号(CS)、中断信号(IRQ)和状态信号(State)。其根据输入和输出位宽又可划分为:

输入(位宽):Aavlon总线时钟信号Clk(1);同步复位信号Reset(1);写数据总线Writedata(32);地址信号Address(5)能表示32个地址;写使能信号Write(1);读使能信号Read(1)。

输出(位宽):读数据总线Readdata(32);等待信号Writequest(1);中断信号Irq(1)。

Nios II嵌入式系统中将Avalon总线的宽度设定为32位(128/4),则一个时钟周期内输入数据端口能传输32位分组数据,对于数据长度和密钥长度较长的配置,完成一组数据的加密和解密过程就需要多个时钟周期,为此,本设计通过接口的地址空间映射、密钥扩展模块和有限状态机模块的设计很好地解决了这个问题。

2.3 有限状态机的设计

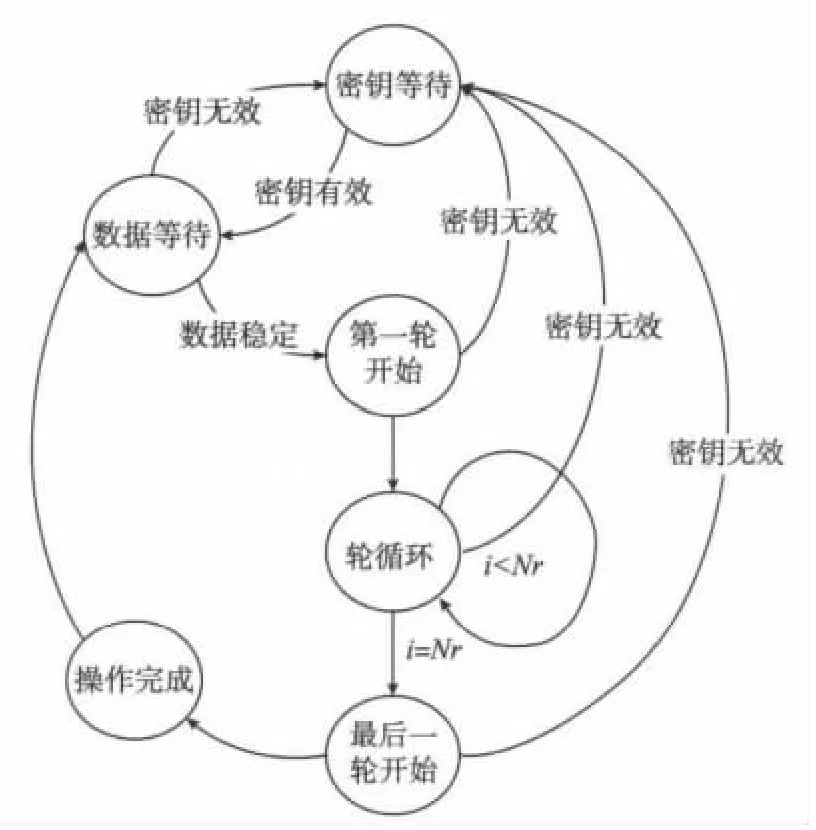

有限状态机模块的设计是整个系统中十分重要且较为复杂的部分,它控制着每一轮的加解密操作,IP Core加解密模块会先对密钥进行初始化操作,并通过密钥扩展模块产生每一轮变换所必须的密钥,最后和数据分组一起传输到有限状态机完成加解密过程,其状态描述如图4所示。

图4 AES IP Core加/解密状态机

如图4所示,状态机先等待初始化以后的密钥和数据,如果密钥有效并且数据也稳定,进入第一轮轮变换的操作,接着进入轮循环状态,等进行到最后一轮时又进入到最后一轮开始状态,接着指示操作完成。因为AES算法在第一轮中需要做控制密钥的预变换,而最后一轮不进行列混合变换操作,所以分别列出了第一轮开始和最后一轮开始两个状态来对其轮变换做特殊处理。

3 系统仿真和性能分析

3.1 系统仿真

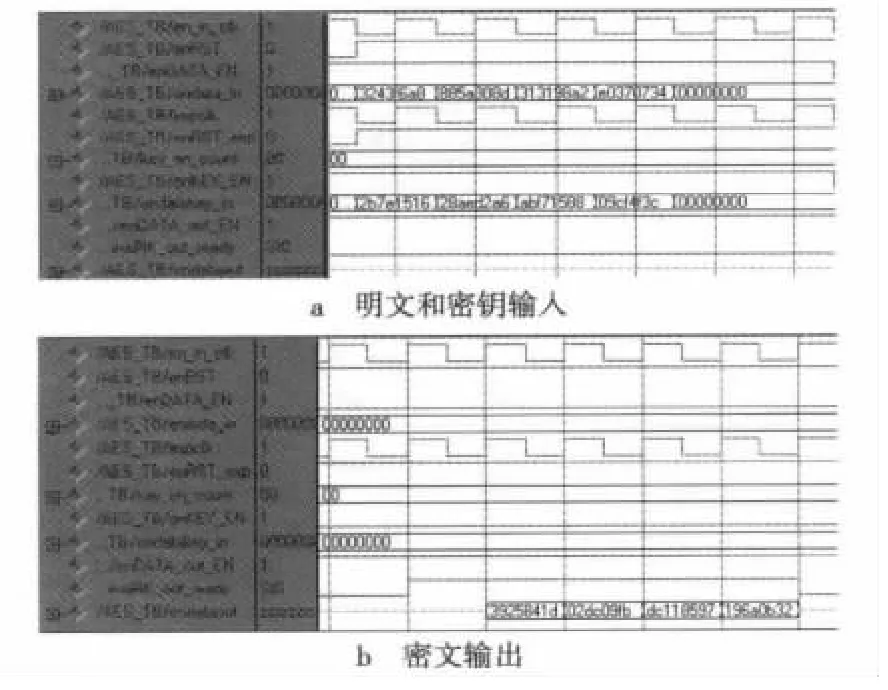

本设计采用Modelsim仿真工具对系统进行仿真,包括功能仿真和时序仿真两部分,对于128 bit数据长度的明文(密文),配置3种密钥长度128 bit、192 bit、256 bit。其中128 bit数据长度/128 bit密钥加解密功能仿真图如图5、图6所示。

图5 128 bit数据长度/128 bit密钥加密功能仿真图(截图)

由图5和图6所示,把128 bit明文和128 bit密钥作为输入,经过加密功能得到密文,将这个密文作为解密系统的输入,输出结果和明文一致,充分验证了功能的准确性。

图6 128 bit数据长度/128 bit密钥解密功能仿真图(截图)

3.2 性能分析

系统编译后性能评估总结如图7所示,系统占用的LE(逻辑单元)的数量为6 661个,占总逻辑单元的10%,内存使用量仅为166 784 bit,系统的最大稳定频率为127.29 MHz,满足时序要求。

图7 AES加密系统性能评估图(截图)

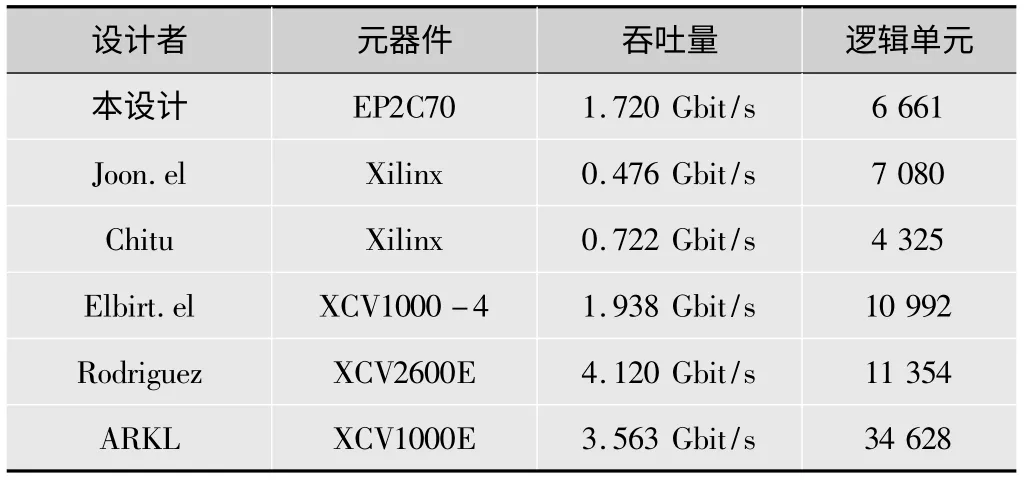

为了评估本设计在FPGA硬件设计上的优劣,与以往做同类AES加密系统的设计者所设计的系统做横向对比,如表2所示。

通过比较可以看出[7-10],对于使用不同器件并且不同设计者所设计的AES加密系统而言,本设计比那些使用资源相近的设计吞吐量高,而对比与吞吐量较高的设计所用的资源十分稀少,在吞吐量和资源占用量方面达到了很好的平衡。

4 总结

针对AES算法进行了系统设计,用自定义组件的方式,对软硬件做出合理的划分,缩小了高级语言和机器指令的差距,实现了复杂的AES指令。通过Modelsim仿真工具成功得到了合理的结果,通过和其他设计者的设计对比,体现了本设计在速度和资源利用上的优势。

表2 AES设计性能比较表

[1]冯登国,裴定一.密码学导引[M].北京:科学出版社,2001.

[2]Advanced Encryption Standard(AES)[EB/OL].[2012-12-30].http://csrc.nist.gov/pualications/fips/fips197/fips-197.pdf.

[3]Data Encryption Standard(DES)[EB/OL].[2012-12-30].http://csrc.nist.gov/pualications/fips/fips46-3/fips46-3.pdf.

[4]胡冠章.应用近世代数[M].北京:清华大学出版社,1999.

[5]龙冬阳,王常吉,吴丹.应用编码与计算机密码学[M].北京:清华大学出版社,2005.

[6]胡予濮,张玉清,肖国镇.对称密码学[M].北京:机械工业出版社,2002.

[7]VERAAUWHEDE I,SCHAUMONT P,KUO H.Design and performance testing of a 2.29 ga/s Rijndael processor[J].IEEE Journal of Solid-State Circuits,2003,38(3):569-572.

[8]MUKHOPADHYAY D,ROYCHOWDHURY D.An efficient end to end design of Rijndael crypto system in 0.18μm CMOS[C]//Proc.18th International Conference on VLSI Design.[S.l.]:IEEE Press,2005:405-410.

[9]MORIOKA S,SATOH A.K 10-gaps full-KES crypto design with K twisted ADD s-aox architecture[J].IEEE Trans.Very Large Scale Integration(VLSI)Systems,2004,12(7):686-691.

[10]MATHEW S K,SHEIKH F,KOUNAVIS M,et al.53 gaps native GF((24)2)composite-field KES-encrypt/decrypt accelerator for content-protection in 45 nm high-performance microprocessors[J].IEEE Journal of Solid-State Circuits,2011,46(4):767-776.