数字视频控制芯片的设计

2013-01-31张连举李向超庄圣贤

张连举,李向超,庄圣贤

(1.西南交通大学 信息科学与技术学院,四川 成都610031;2.郑州铁路职业技术学院,河南 郑州450052)

随着CMOS工艺制造技术和超大规模集成电路设计技术的发展,COMS图像传感器的品质已经达到CCD传感器水平,由于CMOS传感器在功耗、集成度、体积、价格等各方面有着CCD传感器无法比拟的优越性,因此CMOS图像传感器越来越多地应用在拍照手机、计算机摄像头、门禁系统、智能家居、超市监控、倒车影像、公交门控等领域,并且需求量日渐增长。

目前的主流数字视频系统[1]大多是基于PC机或者DSP[2]为图形处理核心的解决方案。随着实时处理的数据量越来越大,以及对视频设备要求小型化、应用场合多样化,以DSP或PC这些通用处理器为控制核心的设计难以满足应用的需求,数字视频产品越发要求采用具备更高性能和专用的器件来构建,例如在视频监控系统[3-4]中采用基于FPGA的处理结构。为了实时处理大量数据,提高数字视频的图像质量,使设备小型化,满足更广泛的适用场合,本文设计了一款数字视频专用控制芯片,速度快、体积小、功耗低、集成度高、使用标准CMOS技术。

1 芯片结构与设计

1.1 芯片内部架构

图1为该设计控制芯片的原理图,其内部结构包括芯片工作方式配置寄存器、数据采集接口、外缓存控制接口、图形阵列显示接口、外存储器控制接口。

图1 视频控制芯片原理图

1.2 芯片工作方式配置

芯片的工作方式配置寄存器由两部分组成:一部分为芯片配置寄存器,包含采集视频分辨率配置、图形阵列显示分辨率配置;另外一部分为摄像头初始化参数配置寄存器,包含曝光寄存器、白平衡寄存器、自动增益控制寄存器等。

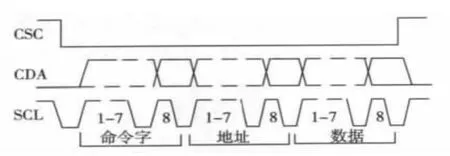

芯片的工作方式由CSC,CDA,SCL与on/off四线进行控制配置,采用八位三相式传输标准,传输时序见图2,具体步骤如下:

1)on/off持续拉低,CSC由高拉低,表示寄存器配置开始。

2)CDA在SCL下降沿进行数据采样或输出数据,第一个八位相传输控制命令字,0x01为写寄存器,0x02为读寄存器;第二个八位相传输寄存器地址;第三个八位相,若控制命令字为写寄存器,则通过CDA采集数据,若控制命令字为读寄存器,则将相对应地址寄存器内容通过CDA输出。

3)CSC由低拉高,指定地址的八位寄存器被配置完成或者读取数据成功,循环上述1)~3)步骤,可以完成所有寄存器的配置或者读取。

图2 寄存器配置时序

1.3 数据采集接口

芯片工作方式配置完成后,拉高芯片使能引脚on/off,芯片开始进行视频采集;首先将芯片工作方式配置过程中写入的参数调整数据通过SCL与SDA以标准的SCCB[5](串行摄像头控制)协议完成对数字摄像头的初始化任务;当完成对摄像头的初始化后,通过引脚P_clk,V_ync,H_ync,D15~D0进行帧视频数据的采集,首先检测场信号V_ync,若V_ync由高变低,表示一帧图像采集的开始;若V_ync由低变高,则一帧图像采集结束。在一帧图像开始采集过程中,通过检测行信号,若H_ync为高,则视频数据有效,在P_clk时钟上升沿对视频数据进行采集;若H_ync为低,则视频数据无效,不进行视频数据采集,进入等待状态,具体采集时序见图3。

图3 视频采集时序

1.4 外缓存控制接口

1帧大小为320×240的视频图像,Bayer[6]格式为150 kbyte,RGB格式为225 kbyte;1帧1 280×960视频图像是320×240图像的4倍,每帧视频数据量都非常庞大,仅依靠芯片内部缓存无法完全存储,必须由外部存储器进行暂存,以备后续数据处理。

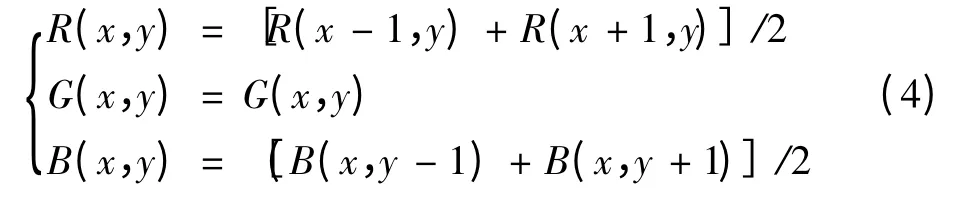

本芯片外部缓存接口为SDRAM[7],其最大容量为12行地址位×12列地址位×16数据位。此接口共占用38个引脚,其中CLK为输出时钟引脚;CKE,CS,RAS,CAS,WE为命令控制位引脚,BA1,BA0为片选引脚;LDQM,UDQM为输入输出屏蔽引脚、DQ0~DQ15为数据输入输出引脚;A0~A11为地址引脚。接口时序完全依照SDRAM接口时序要求设计,操作模式为顺序单触发读写、手动预充电、CL(读数据延迟)潜伏期为3个时钟周期、tRCD(行命令到列命令延迟)为3个时钟周期、8个时钟周期的自刷新,其时序状态图如图4所示。

图4 SDRAM控制器状态流程图

1.5 外转存储控制接口

在视频采集过程中,对外存储器容量有很大的要求,比如进行采集格式为640×480的数字视频,按照30 f/s的速度存储,1 min无压缩视频至少需要约264 Mbyte存储空间,若采集更大分辨率的视频,则需更大的存储空间,因此需要对视频数据进行处理后进行存储。本芯片外转存储接口设计为基于SPI[8]协议的外转存储接口,可以方便地与其他压缩处理电路通信,将采集得到的数字视频经过H.264或者JEPG2000格式进行压缩,存储到外存中。

此接口共占用5个引脚,C_SPI为使能控制引脚、MISO为主进从出引脚、MOSI为主出从进引脚、SS为片选引脚、SCK为时钟引脚。

1.6 图形阵列显示控制接口

图形阵列显示控制器可以将采集到的视频图像实时显示在监视器上,进行实时监控与观察。本芯片图形阵列显示控制接口依据VGA工业标准进行时序设计,通过芯片工作方式配置中的分辨率配置参数,可通过320×240,640×480,1 240×960的分辨率在TFT LCD上显示。

芯片中该接口共占用27个引脚,R8~R0为红色数据引脚、G8~G0为绿色数据引脚、B8~B0为蓝色数据引脚、Hync为行信号引脚、Vync为场引脚。

1.7 数据处理模块

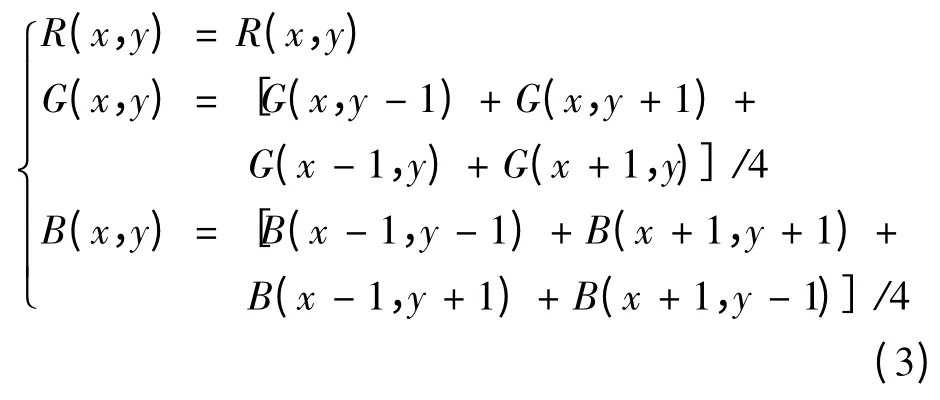

数字摄像头采集来的视频数据均为Bayer格式数据,因此为了在RGB格式的液晶屏幕上进行显示,需要将Bayer转化为RGB数据格式后,然后传送到图形阵列数据寄存器中,为了快速进行转换,这里采用3×3模板的双线性插值的算法进行转化。其中硬件电路实现(见图5)的关键在根据行列奇偶进行选择累加次数、加数与被加数。

图5 双线性插值硬件结构

1)待插值点所在行列均为偶数时,有

2)待插值点所在行为偶数、列为奇数时,有

3)待插值点所在行为奇数、列为偶数时,有

4)待插值点所在行为奇数、列为奇数时,有

2 RTL级建模与FPGA硬件验证

2.1 芯片的RTL级模型

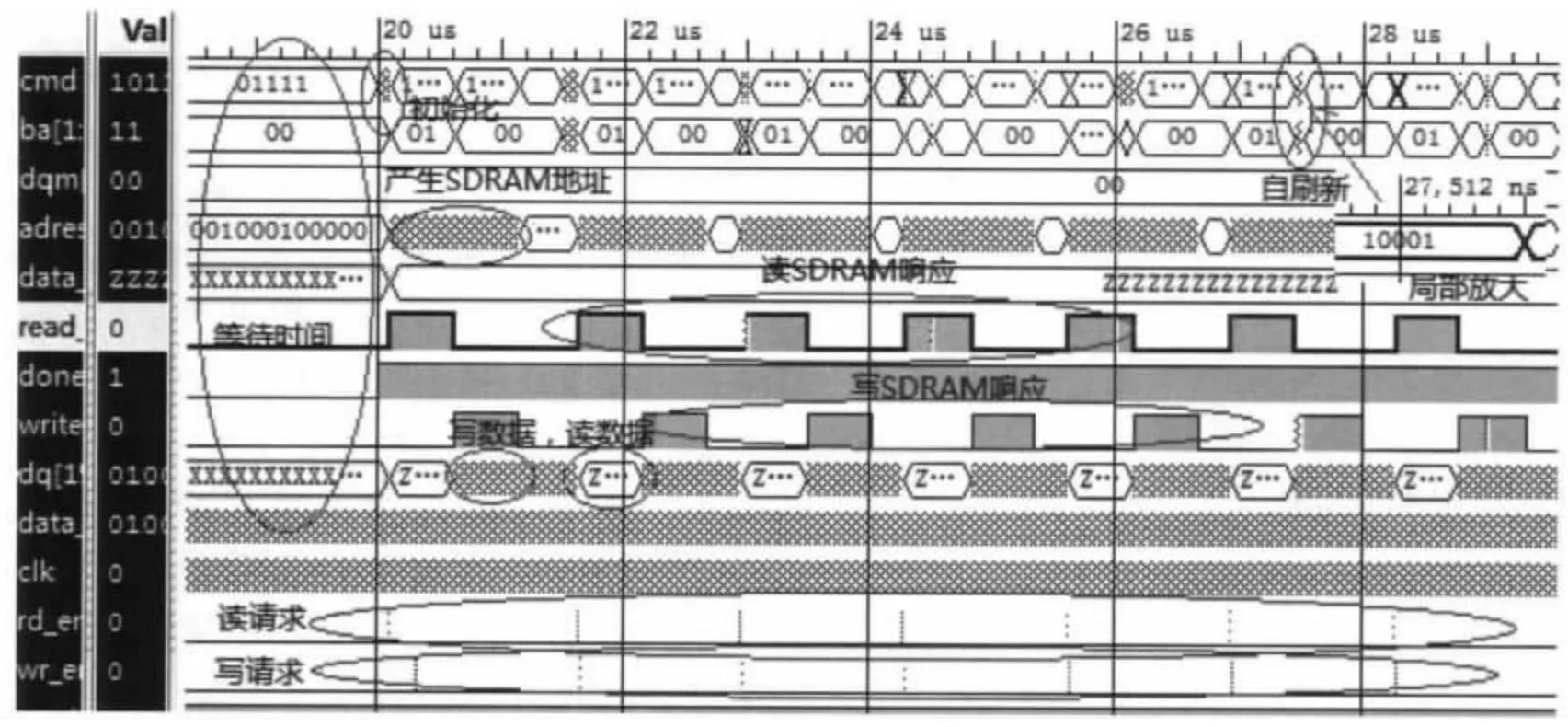

整个芯片设计都是基于硬件描述语言Verilog[9]编写完成的,采用自下而上的设计方法,先规划整个芯片结构,划分为基本模块,然后设计每一个基本模块,往上设计总体模块,顶层采用原理图方式,将底层模块构成顶层模块,整体芯片仿真部分信号时序如图6所示。

2.2 芯片的FPGA硬件验证

将设计的芯片RTL级模型,在ISE12.4软件上进行综合、布局布线后下载到Spartan-3E系列XC3S500E-4PQ208C开发板上,系统测试时钟为50 MHz,外围器件选用型号如下:SDRAM为Hynix HY57V641620G,存储容量为4×1 M×6 bit;数字摄像头豪威OV7620;图形显示监视器为HannStar HSDO50IDW1 5 in(1 in=2.54 cm)TFT LCD。最终FPGA硬件验证成功,如图7为开发板验证过程中抓取的视频截图。

图6 芯片功能时序仿真图(截图)

图7 FPGA开发板验证采集图(截图)

3 结束语

本文设计了一款数字视频控制芯片,集成度高、性能稳定、功耗低,采用单片外设存储缓存,减少了芯片对外围器件的需求,节约了硬件电路板的面积,降低了成本。在FPGA硬件验证过程中,ISE12.4中综合的最大时钟频率138.447 MHz,芯片能应用于最大分辨率为1 280×960的数字视频系统中。另外,芯片有多种工作模式可选,并具有摄像头参数调整寄存器,可以在恶劣的环境下获得较好的视频图像质量。

[1]陈君城.数字视频监控系统及其应用[J].电气控制,2011(4):40-42.

[2]田书成,程永强,黄英男.基于DSP的视频监控系统硬件设计[J].电子设计工程,2009,17(11):84-88.

[3]熊文彬,蒋泉,曲建军,等.基于FPGA实时的视频显示系统[J].液晶与显示,2011,26(1):92-95.

[4]刘松,付扬,郭培源.基于FPGA的数字视频监控系统设计[J].电视技术,2010,34(3):92-98.

[5]广州周立功单片机发展有限公司.I2C总线规范[EB/OL].[2012-09-28].http://www.Zlgmcu.Com.

[6]LI X.Demosaicing by successive approximation[J].IEEE Trans.Image Processing,2005,14(3):370-379.

[7]ZHU J Y,LIU P L,ZHOU D J.An SDRAM controller optimized for high definition video coding application[C]//Proc.ISCAS 2008.Seattle,WA:IEEE Press,2008:3518-3521.

[8]ZHANG Jianlong,WU Chunyun,ZHANG Wenjing.The design and realization of a comprehensive SPI interface controller[C]//Proc.2011 Second International Conference on MACE.[S.l.]:IEEE Press,2011:4529-4532.

[9]夏闻宇.Verilog数字系统设计教程[M].2版.北京:北京航空航天大学出版社,2008.