交通系统中信号灯的FPGA实现研究

2013-01-30张开生

张 昭, 樊 迪, 张开生

(1.陕西科技大学 教育部轻化工助剂化学与技术重点实验室, 陕西 西安 710021; 2.河北工业大学 信息工程学院, 天津 300401; 3.陕西科技大学 电气与信息工程学院, 陕西 西安 710021)

0 引言

由于设计交通灯的方案有很多,目前比较成熟的方案中,控制器的设计可以用到51单片机作为控制核心[1],也可以采用EDA技术,用FPGA实现控制和倒数计时器的设计[2-5],本文就是采用后者的技术,直接驱动LED灯和数码管,这样也省去了外部硬件驱动电路的设计.通过VHDL语言编程控制信号灯的时序变化,采用多进程的设计和主程序调用各功能模块的方法实现上述各项功能,之后利用软件平台对设计系统进行仿真[6],在以往的仿真过程中经常采用Max+Plus II进行仿真,本文考虑到Max+Plus II相对于Quartus II来说比较传统,其软件的发展前景和应用的广泛性都在Quartus II之下,Quartus II软件含有FPGA设计所有阶段的解决方案,不存在人工接线的问题,所以故障率低、可靠性好,更提供了对一些新器件和新技术的支持,是设计者能够轻松全面的介入到设计的每个环节,所以在编译仿真时选取了Quartus II 9.1软件平台,最后根据得到的仿真波形,就可以直接的观察出程序的功能实现是否符合研究要求.

1 智能交通控制系统结构分析

FPGA系统设计的相关技术很多,包括了FPGA的结构原理,电路硬件设计与调试,硬件描述语言(HDL),开发工具EDA软件,仿真验证技术以及FPGA和其他处理器的互联接口技术等[7-10].进行VHDL设计实现时,首先考虑到大多数情况是通过自动控制的方式指挥交通,所以为了使系统正常运行,电路中必须有一个稳定的时钟源,再用分频器得到想要的时钟频率,并且可以通过计数器转换成BCD码显示出来,其中可以用到七段显示器,之后根据不同的功能模块进行设计,并且利用软件平台对设计系统进行仿真.

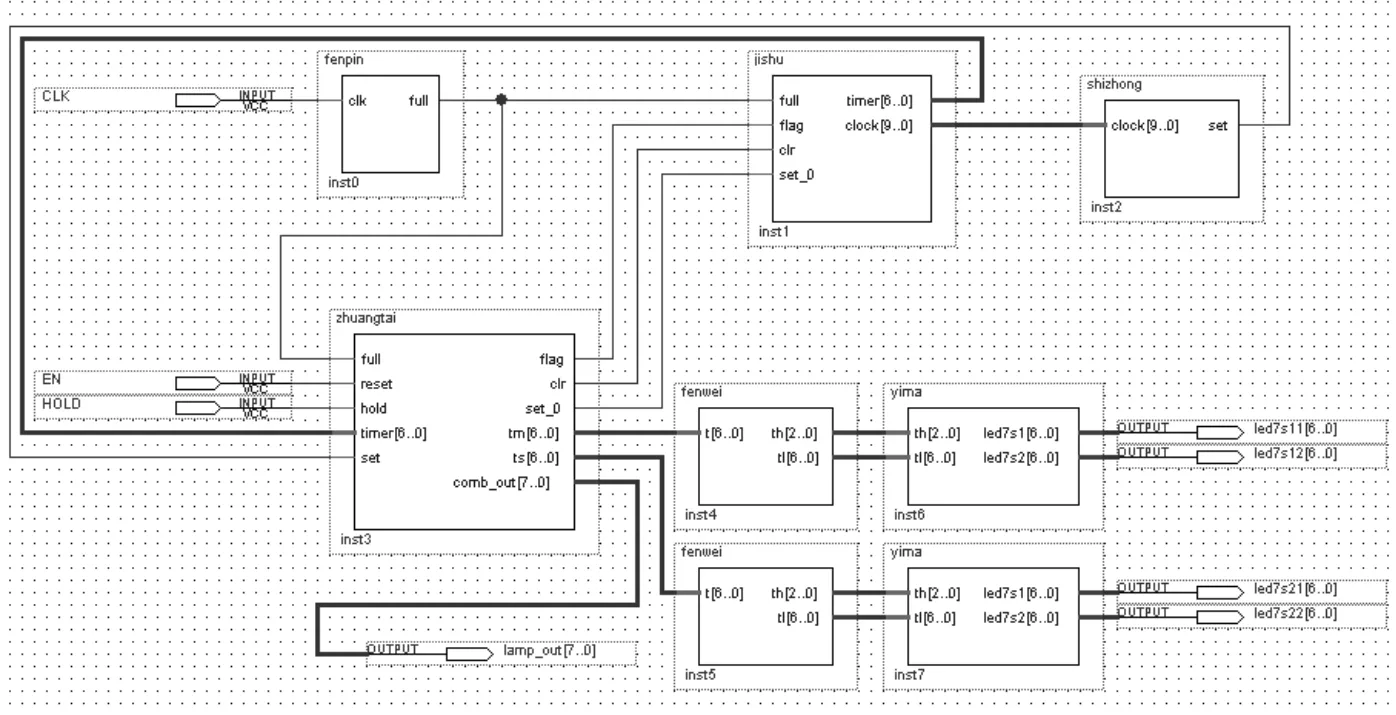

2 系统程序模块分配

按所需时序控制变化,在整个系统中可以按照功能分为几个不同的模块[11-12],分别有分频模块、计数模块、状态控制模块、分位显示模块和译码驱动模块,各个模块之间的连接如图1所示.其中,计数模块里包含了一个24 h的时钟控制器部分,它是为了实现夜间信号变化而存在的模拟时钟.状态控制模块类似于一个状态机,由主控时序逻辑进程和组合逻辑进程两个部分组成,通过状态控制模块改变二极管的显示情况,而倒计时则由分位译码后的二进制数输出给7段数码管后显示出来.

图1 系统原理图

2.1 分频和计数模块

此模块是为了产生所需倒计时的秒数,将输入的clk信号分频为所需的1 Hz,在选取有源晶振时为保证时钟的准确度,晶振频率不能过小.本课题中用到的有源晶振是100 kHz,已经可以满足钟表所需的频率,所以设计时应在经过105个clk上升沿后full信号发生跳变,产生一个脉冲,这样full信号就是一个周期为1 s的时钟信号,且信号没有按照常规的占空比为50%的时钟信号设计,而是一个一个相隔时间为1 s的脉冲.

计数模块主要实现累加循环计数,在时钟full的驱动下,计数值timer不断自加,当达到一规定数值时计数返回到0,开始新一轮的计数,其中规定数值就是信号灯所有状态循环一遍所需要的时间.考虑到一共六个状态都需要计时,如果采用六个计时器的话对资源是一种浪费,所以用一个通用的计数器,运行到某一状态就开始对这一状态进行计时.另外,在数码管显示倒计时时,数字应不断减少,而本课题为了便于通用计时器的设计,采用的是加法计数器,所以在状态转换模块中执行的计数时间是用倒计时间总数减去timer当前的数,这样就可以依次得到递减的数值.

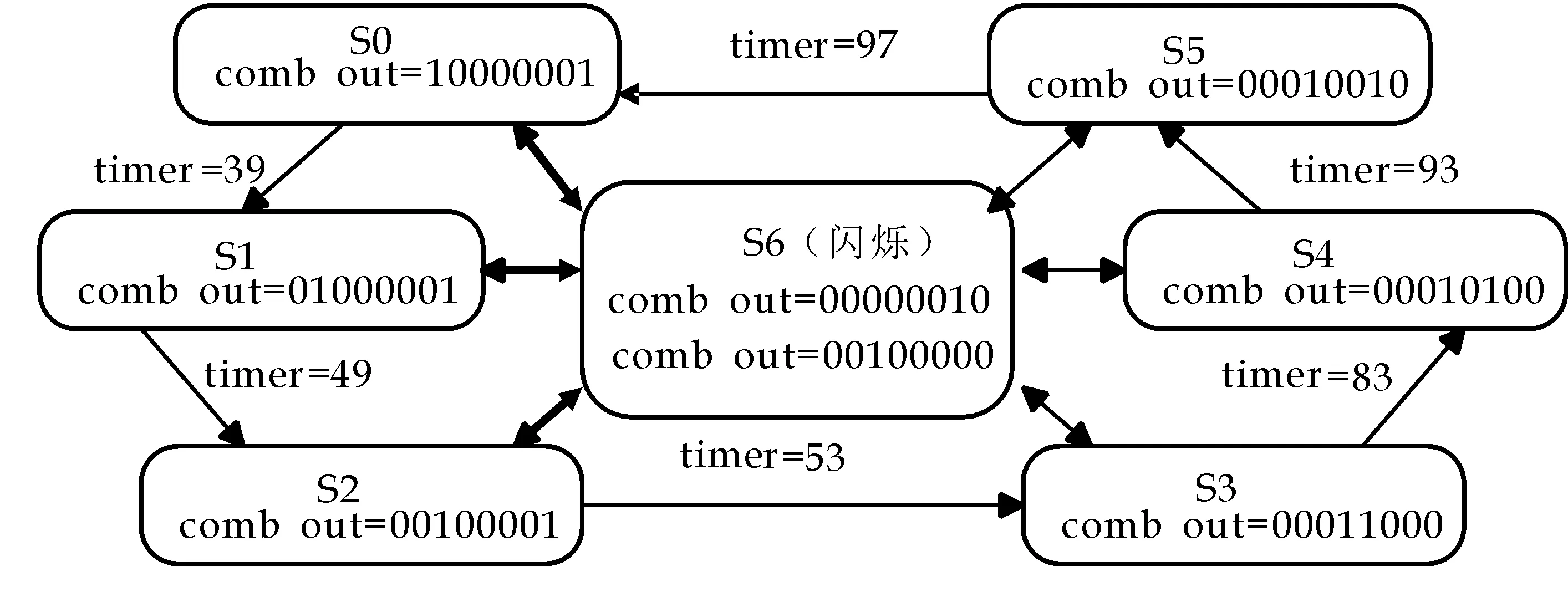

2.2 状态转换模块

状态控制模块类似于一个状态机,由两部分组成,分别是主控时序逻辑进程和组合逻辑进程,不论当前状态如何,时序逻辑进程只将当前状态转换为下一状态,只有当来自时序逻辑进程的信号改变时,组合逻辑进程才开始执行.图2是整个模块的状态转换图,输入输出按照时序图的流程,可以将整个时序变换分割为六个状态,在倒计时计数达到规定时间时发生状态变化.由于主路和支路的信号灯共有8个,所以在程序中设定一个八位的输出信号comb_out,从高位到低位分别依次控制主路直行绿灯,主路左转绿灯,主路黄灯,主路红灯,支路直行绿灯,支路左转绿灯,支路黄灯,支路红灯.其中高电平代表灯亮,低电平代表灯灭.

考虑到夜间黄灯闪烁的情况,应再添加一个S6夜间状态,当模拟时钟到达22点时,不论现在处于什么状态,都要跳转到S6状态开始两个路口同时黄灯闪烁,并且倒计时每一位全部显示为0,最后在6点时再跳转回初始状态.

图2 状态转换图

2.3 分位和译码模块

分位模块的设计主要是将灯亮的时间拆分成十位和个位后分别通过两个7段数码管显示出来,在本设计中灯亮时间最长为58 s,程序中tm、ts分别为主路和支路的倒计的时间,分别把他们分为十位thm、ths和个位tlm、tls两个数组合表示一个十进制数,从而实现了分位功能.如图3所示是基本分位模块t分位的过程图.

分位后,通过对照7段数码管显示的对应二进制码,对应相应的译码数值,将十位和个位分别由7段数码管显示出来,这就完成了倒计时的显示功能.

图3 分位模块设计图

3 芯片连接设计

考虑到智能交通未来的发展情况和本文应用于实际的成本问题,本系统选用的是Alter公司生产的Cyclone系列的EP1C6Q204C8芯片,是新一代采用SRAM工艺的中等规模FPGA芯片,成本相对较低.EP1C6Q204C8具有5 980个逻辑单元,完全能够满足用户逻辑的需要,内嵌有20个M4K RAM嵌入式存储器块和两个Pll,可以为系统提供时钟信号,大大降低了系统的时钟延时,并且最大支持185个用户I/O管脚资源,能够提供足够的各类接口[16].在完成之前的编译与仿真后,选择EP1C6Q204C8芯片为设计文件进行管脚分配并编译整个工程文件,最后完成系统的原理图设计.

4 仿真结果与比较

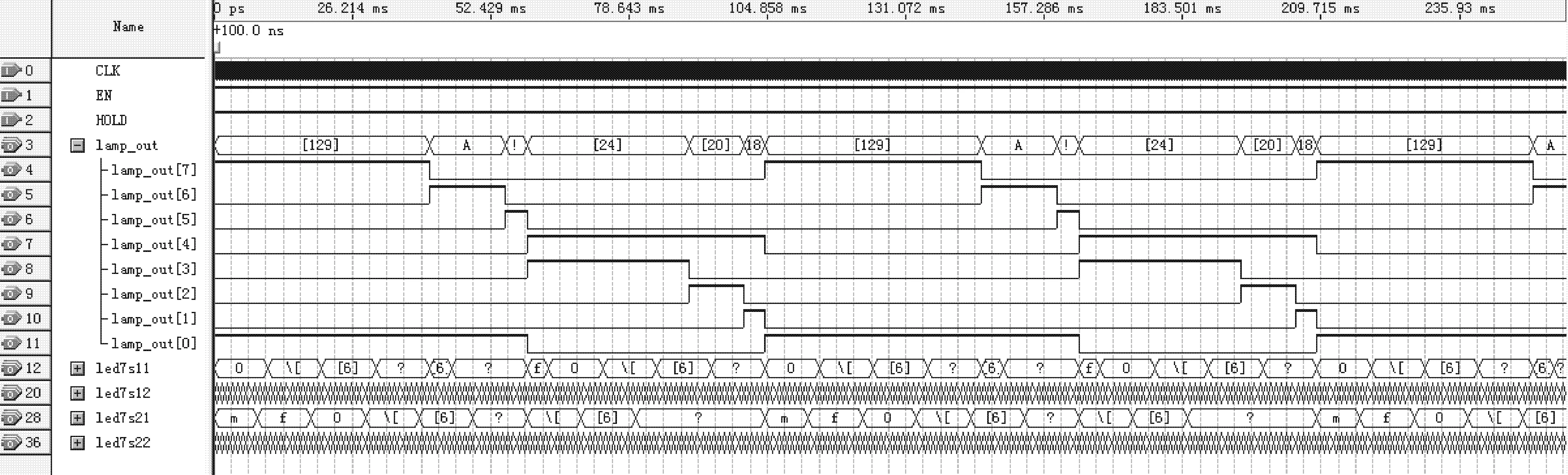

4.1 功能仿真

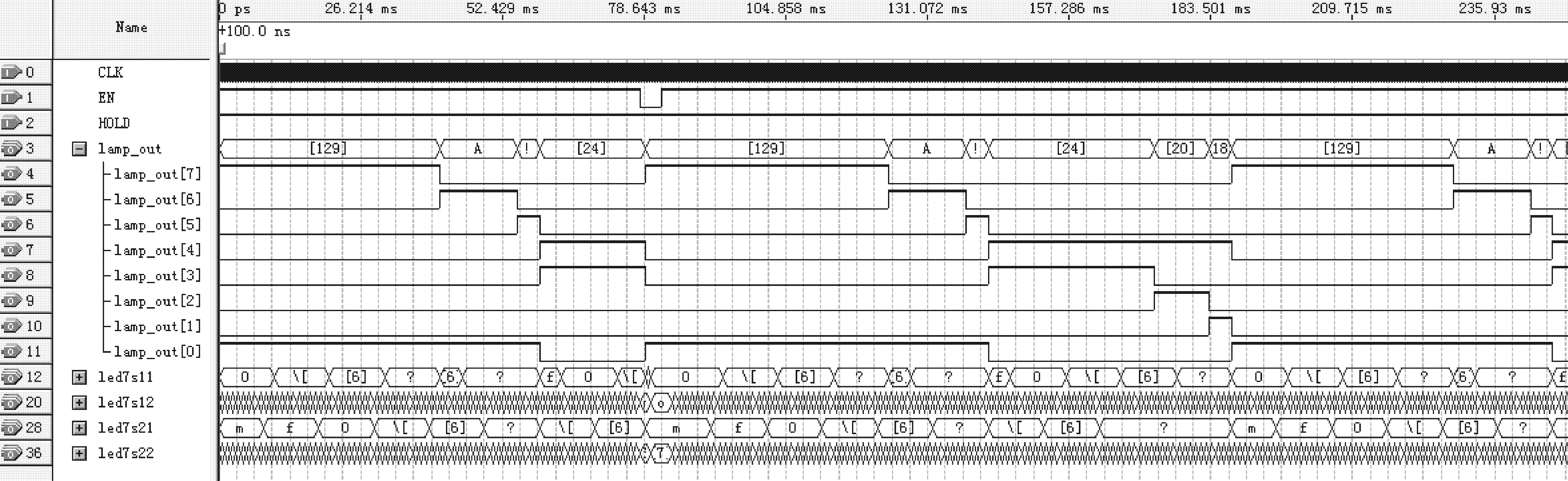

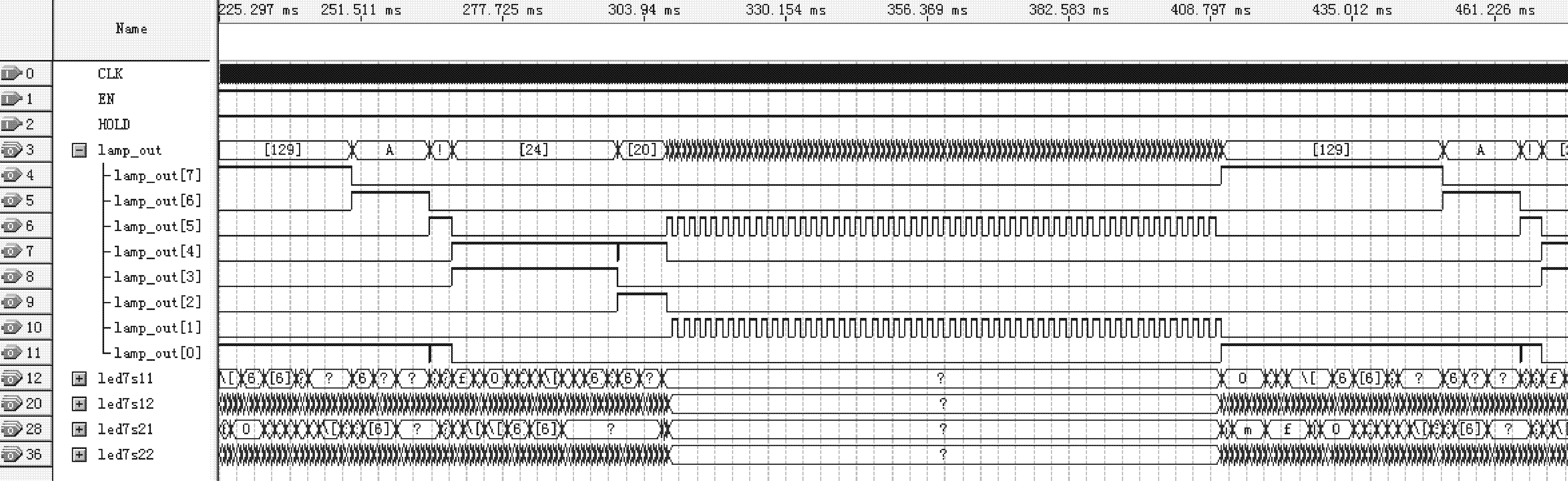

图4 信号灯正常指示仿真波形

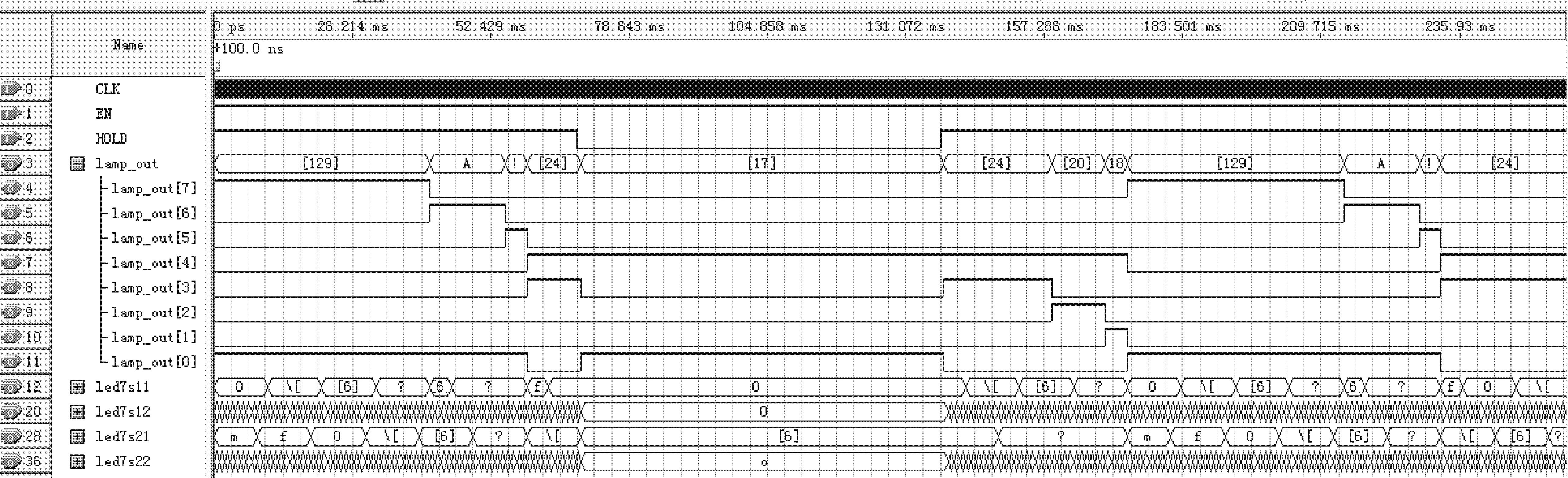

图5 发生复位时仿真波形

图6 紧急情况时仿真波形

图7 夜间指示时仿真波形

图4~图7为不同条件下的仿真波形.根据仿真波形可以看到当复位开关按下,EN变为低电平的一段倒计时全部归零,状态保持在初始状态,当开关再次弹起时,开始从初始状态的正常信号灯运转.

紧急情况功能用一个HOLD信号来控制,当HOLD为高电平时正常运行,为低电平时各方向红灯均亮起,所有车辆禁止通行,并且所有数码管显示暂停倒计时,等HOLD又跳回高电平时继续运行,仿真波形如图6所示.另一个夜间指示的仿真波形如图7所示,到了22点时所有路口黄灯开始交替闪烁,倒计时数码管始终显示时间为零.

4.2 时序仿真

功能仿真正确后,可以加入延时模型,将Simulation mode选为Timing模式进行时序仿真.

在设计好工程文件后,首先要进行工程的约束,约束主要包括器件选择、管脚分配及时序约束等.时序约束属于较为高级的应用,通过时序约束可以使工程设计文件的综合更加优化.在选择器件系列以及器件的型号后就可以为设计文件进行管脚分配了,按照需求进行管脚定义,最后再编译整个工程文件,就可以下载到硬件了.在设计中没有用到的管脚很容易导致系统程序运行不正常,因此对于一些未使用的FPGA管脚一定要将其设为三态输入,以隔离其它电信号的干扰.

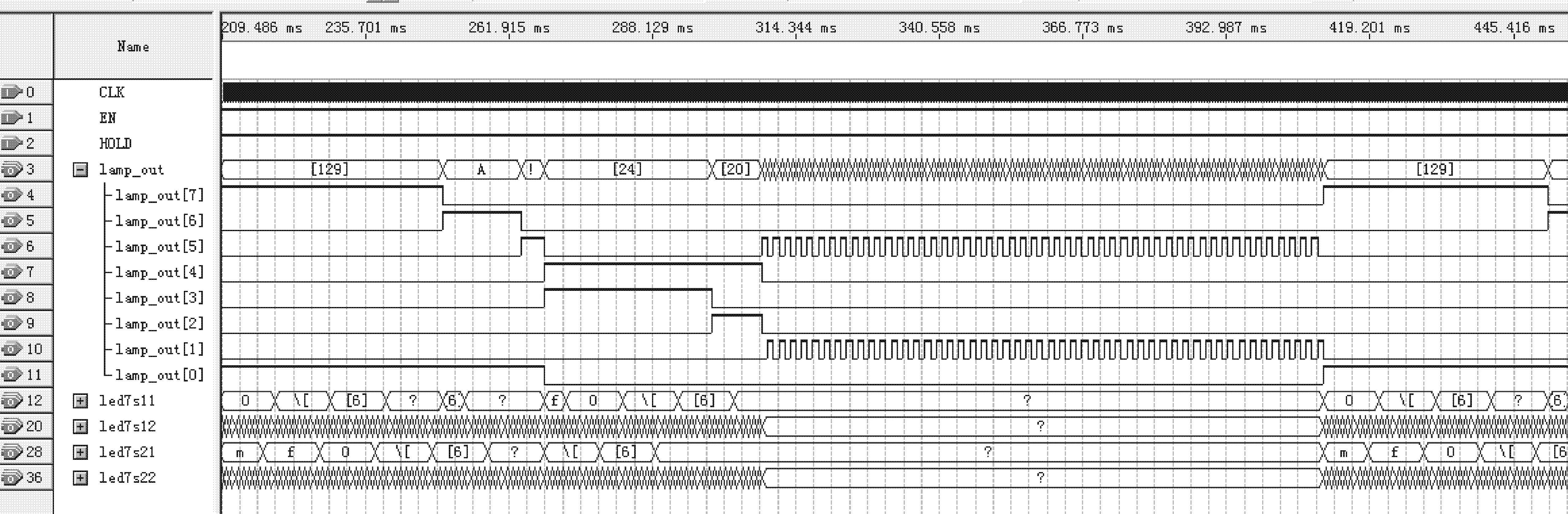

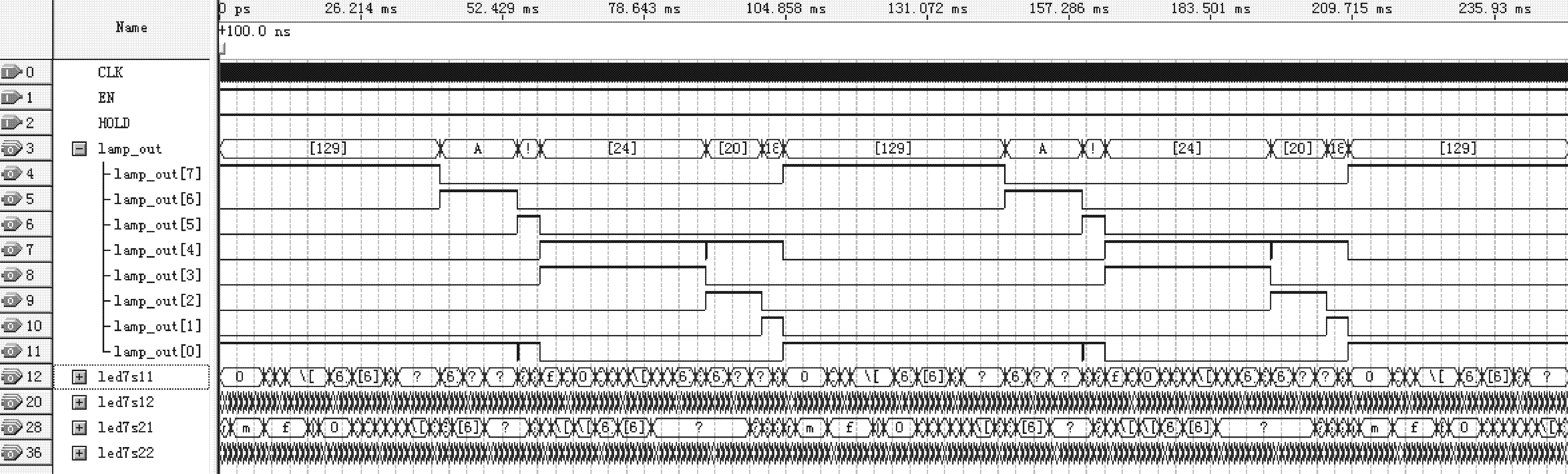

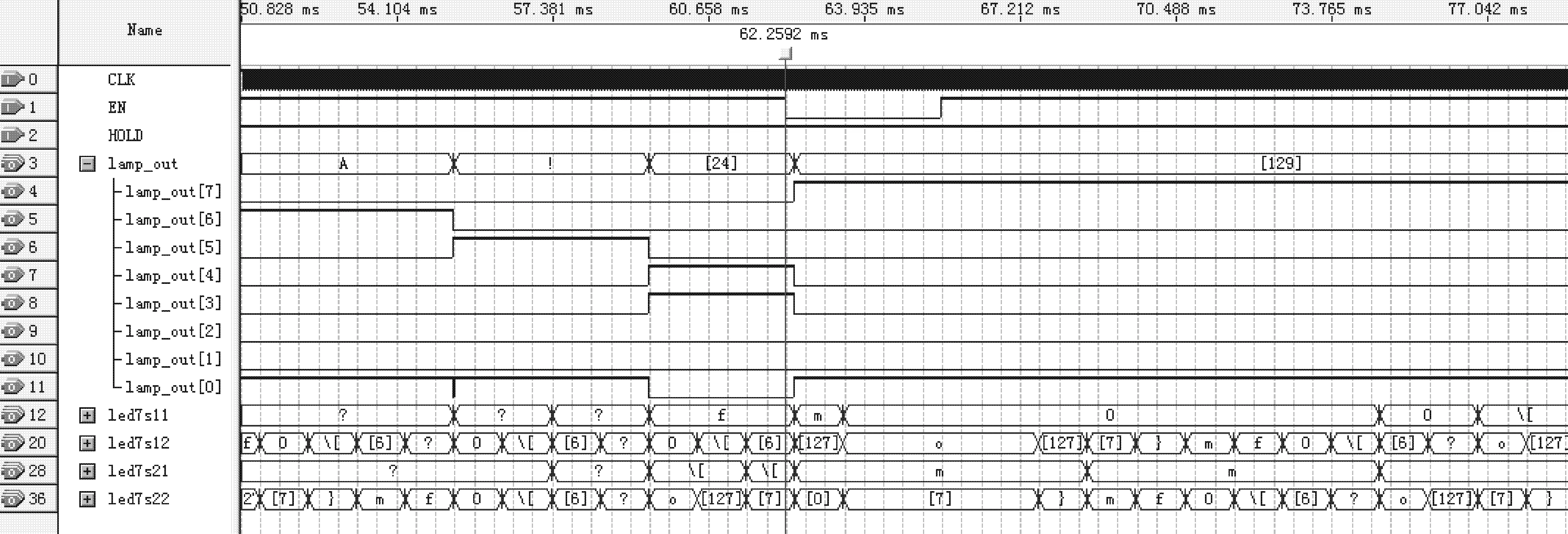

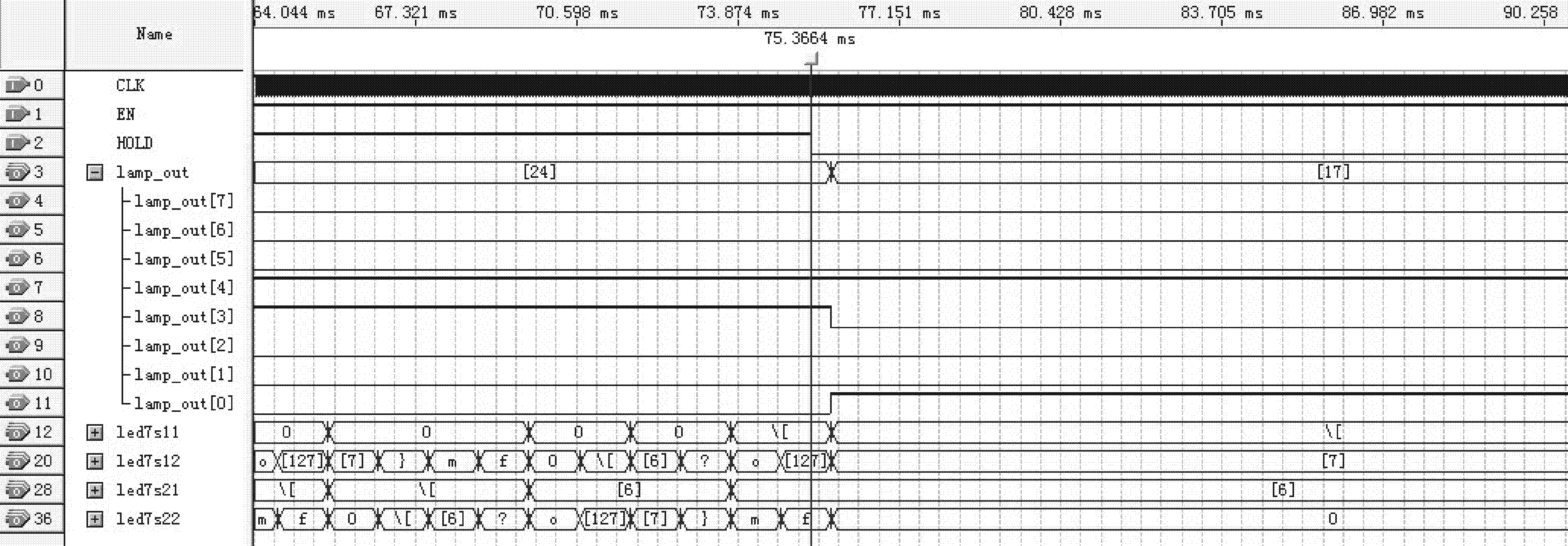

通过时序仿真结果可以看到,信号灯正常交替运转时的波形和夜间黄灯闪烁的波形正确,波形如图8和图9所示.

从两个特殊状态的时序仿真看到,从EN和HOLD给出信号到波形发生变化之间产生了一定的延时,但是并没有影响系统的功能实现.图10和图11所示分别是通过放大工作区和拖动时间测量游标观察两个特殊状态的波形延时情况,尽管输出相对于开关信号存在一定延时,但输出结果是正确的,符合设计要求,不影响系统功能的实现.

图8 信号灯正常指示仿真波形

图9 夜间模式的时序仿真波形

图10 发生复位时的波形延时

图11 紧急情况下的波形延时

功能仿真并不包含延迟,而时序仿真则会根据具体的器件参数配置及资源使用情况将延时仿真出来.功能仿真主要用于验证工程设计文件逻辑的正确性,而时序仿真更能体现真实的硬件运行过程中设计文件的执行过程.在进行时序仿真时,如果改变了设计程序或者管脚的配置,就会出现没有波形的情况,这时候就要重新对设计分析与综合,包括程序的汇编和管脚的适配,之后才能进行时序分析.时序仿真更侧重观察信号的延时,所以在波形图中网格的大小应该适当调小来观察延时程度.

在进行了功能仿真和时序仿真之后就可以开始物理综合于硬件的下载了,可以用仿真软件中的Assembler为整个系统设计建立编程文件,通过编程器将设计下载到FPGA芯片中.

5 结束语

传统的交通灯控制系统大多数由单片机或PLC来实现,而本文在设计过程中,综合运用了FPGA的相关知识和EDA技术,并利用VHDL硬件描述语言编程,最后借助Quartus II软件平台对系统进行编译及仿真测试.随着EDA技术的发展和应用领域的扩大与深入,它在日常生活中的重要性日益突出,其中交通信号灯的控制就是与人们生活息息相关的常见应用之一,本文的设计研究具有一定的实用性,对城市交通的畅通起到了重要作用.采用EDA技术实现交通灯控制电路的设计方案可以有效的克服传统的交通灯控制的缺点,采取自顶而下的设计思路,从设计思路、描述方法及语句运用上对电路进行多方面的优化设计,通过电路优化设计,可以使用规模更小的可编程逻辑芯片,从而降低系统成本.本文采用的相关技术不仅可以大大缩短开发研制周期,提高设计效率,还使整个系统具有灵活应变能力,并且性能稳定,实现简单,有效降低了数字系统的设计难度,易于发现错误并进行修改.

[1] Wu L,Liu J X,Min D.Single chip fuzzy control system based on mixed-signal FPGA intelligent human-machine systems and cybernetics[C]//2009 International Conference on Intelligent Human-Machine.Hangzhou:IEEE Conference Publications,2009:397-400.

[2] Zhu Hao,Wang Mulan,Su Wei,et al.Design of servo system intelligent control chip based on FPGA[J].Advanced Materials Research,2012,542-543:949-952.

[3] 谭会生.基于FPGA的网络通讯流量模糊控制器的实现[J].测试技术学报,2011,25(5):421-426.

[4] Liu zhenggang,Xiong jialong,Zhou mingyun,et al.FPGA-based dual-mode traffic lights system design[C]//2009 First International Conference on Information Science and Engineering.Nanjing:IEEE Computer Society,2009:558-561.

[5] Li li,Song jingyan,Wang feiyue.New developments and research trends for intelligent vehicles[J].IEEE Intelligent Systems,2005,20(4):10-14.

[6] Xu C F,Yuan Y,Wang J J.A new method for FPGA development[C]//2011 International Conference on Information Science and Technology.Nanjing:IEEE Computer Society,2011:314-317.

[7] Lee P S,Lee C S,Lee J H.Development of FPGA-based digital signal processing system for radiation spectroscopy[J].Radiation Measurements,2013,48:12-17.

[8] Liu C R,Zhang S Y.Hydro-generating unit axis intelligent detection system design based on single-chip microcomputer[C]//2011 International Conference on Consumer Electronics,Communications and Networks.Xianning:IEEE Conference Publications,2011:402-405.

[9] Moon Y S,Roh S H,Jo K H,et al.A study on the development of servo motor control IP core based on FPGA[J].Journal of Korean Institute of Intelligent Systems,2010,20(4):562-568.

[10] Weber J,Chin M,Timossi C,et al.Hardware and software development and integration in an FPGA embedded processor based control system module for the ALS[C]//2007 IEEE Particle Accelerator Conference.Albuquerque:IEEE Conference Publications,2007:503-505.

[11] Zhao haimeng,Zheng xifeng,Liu weiya.Intelligent traffic control system based on DSP and nios II[C]// International Asia Conference on Informatics in Control, Automation and Robotics, CAR′09.Bangkok: IEEE Computer Society,2009:90-94.

[12] 杨晓慧,杨 旭.FPGA系统设计与实例[M].北京:人民邮电出版社,2010:13-22.