基于MCU的FPGA系统在线配置及实现

2013-01-29晏勇

晏 勇

(1.阿坝师范高等专科学校 电子信息工程系, 四川 汶川 水磨 623002; 2.电子科技大学 信息与软件工程学院, 四川 成都 610054)

0 引言

信息社会高速发展离不开集成电路,现代电子产品性能不断提高,复杂程度不断增大,价格不断下降,这都依赖于EDA技术高速发展.产品是否便于现场升级,是否便于灵活应用,成为商家是否能够快速占领市场的关键因素.FPGA/CPLD继承了ASIC高集成、大规模、高可靠性的优点,又克服了普通ASIC周期长、投资大、灵活性差的缺点,已成为各类复杂电路的不错选择.在这种环境下,ALTER公司开发了基于查找表(LUT)和静态随机存储器(SRAM)的现场可编程逻辑器件FPGA,并得到了广泛应用和肯定.

FPGA(Filed Programmable Gate Array,简称FPGA)是一种高密度可编逻辑器件,基于数字逻辑门电路连接编程,生成网表文件配置进入FPGA芯片内部随机静态存储器,实现各种复杂逻辑功能.由于FPGA基于SRAM,调电后芯片内部数据全部丢失,每次系统上电时都需要重新配置,即ICR(In Circuit Reconfigurability),系统才正常工作,因此FPGA系统须接flash器件保存配置数据.

从FPGA配置连接方式看,FPGA配置主要分为3类:一是通过下载线缆由计算机直接进行配置,二是利用FPGA专用配置器件进行配置,三是利用CPLD或MCU进行配置.第一种配置方式调试方便,但系统调电后数据全部丢失,缺乏现场实用价值;第二种配置方式系统数据保密性不强;第三种配置方式兼有第一种和第二种配置方式的优点.从FPGA在配置过程中所起的引导作用看,FPGA配置可以分为3类:FPGA主动引导配置方式、FPGA被动配置方式和JTAG方式.MCU与FPGA连接方式可分为配置数据并行传输的总线连接方式和配置数据串行传输的独立连接方式.

本文提出了一种基于MCU与FPGA独立连接和Flash上电FPGA配置方案.由MCU引导配置,PFGA被动串行配置PS模式,基于MCU的PS配置模式继承了MCU和FPGA的优点,实现了对Altera公司FPGA器件在线配置,通信可靠、配置过程稳定、硬件接口灵活,在实际中得到了广泛应用.

1 配置系统硬件设计

1.1 Altera公司FPGA选型

Altera公司生产具有ICR功能的FPGA器件有APEX、ACEX、FLEX6000、FLEX10K、Cyclone、Stratix等系列.FPGA器件选用Altera公司具有代表性的Cyclone系列器件EP1C3T144C8,I/O供电电压3.3 V,内核和PLL电压1.5 V,有源时钟晶振50 MHz.器件内部含等效门电路数50万逻辑门电路,4 000个LE,1个PLL,QFP108封装.

1.2 MCU配置FPGA时序

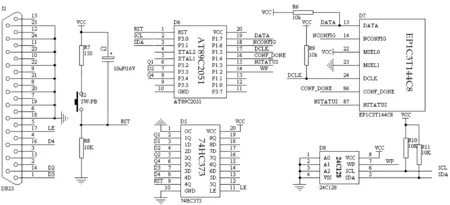

嵌入式系统中,MCU能产生FPGA配置时序引导配置,由MCU控制将配置数据流通过E2PROM传输到FPGA中,每次上电后,FPGA配置数据从E2PROM读取,EP1C3T144C8配置中通过MLES1和MLES0引脚设置配置方式,分别位于器件23和22脚,当MLES1=0, MLES0=1,EP1C3T144C8采用被动串行配置方式,MCU引导FPGA配置,FPGA处于被动.

在PS配置模式中,FPGA通过5个I/O口与MCU连接,这5个引脚分别是NCONFIG、DCLK0、DATA0、NSTATUS、CONF_DONE,分别位于EP1C3T144C8第14、24、13、87、86引脚.其中,NCONFIG配置控制输出;DCLK0配置时钟输出端;DATA0配置数据输出端;NSTATUS配置状态输出;CONF_DONE配置完成标志位.器件配置期间,CONF_DONE输出低电平,配置完成后自动输出高电平.MCU与NCONFIG、DCLK0、DATA0连接端口设置为输出状态,与NSTATUS、CONF_DONE连接端口设置为输入状态.

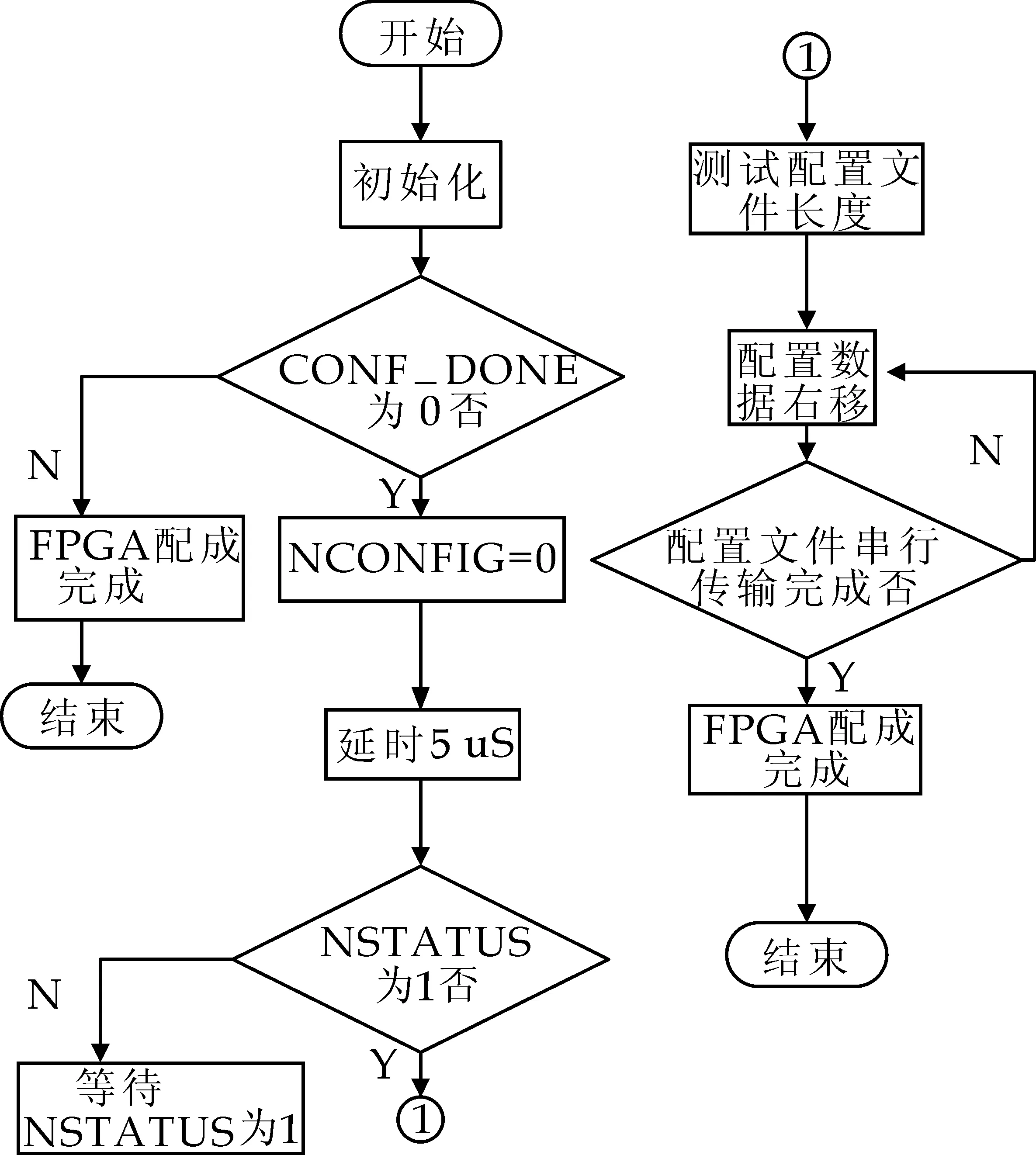

嵌入式系统中FPGA Cyclone EP1C3T144C8被动串行配置模式PS模式的配置流程如图1所示.微处理器启动引导FPGA配置时,首先由微处理器与FPGA NCONFIG引脚相连的IO上发出一个大于8 uS的低脉冲,当FPGA NCONFIG引脚收到由MCU来的低电平后,立即将NSTATUS和CONF_DONE引脚电平拉低,其中NSTATUS为配置状态输出,CONF_DONE为配置完成标志位,MCU收到NSTATUS引脚低电平后,NCONFIG引脚和NSTATUS引脚同时为低电平,当MCU控制NCONFIG引脚跳变为高电平4 uS后,FPGA NSTATUS变为高电平,FPGA进入配置状态,1 uS后MCU发送同步时钟和配置数据信号启动FPGA配置,由DATA0在时钟DCLK0的引导下串行传输数据,配置期间CONF_DONE一直为低电平,FPGA配置完成后CONF_DONE变成高电平,如配置过程中数据传输出错或配置失败,NSTATUS会自动拉低重启配置,器件配置完成后由FPGA引导各种应用功能.

图1 MCU配置FPGA流程图

Altera公司Cyclone FPGA配置可分为4个过程:(1)Vcc上电阶段,Vcc上电爬升到稳定过程;(2)配置准备阶段,NSTATUS和CONF_DONE拉低;(3)配置阶段,FPGA完成配置后CONF_DONE输出高电平,系统初始化;(4)用户模式阶段,由FPGA引导系统工作.FPGA工作状态分为3种,即:用户状态,FPGA引脚输出高低电平;配置状态和初始化状态,FPGA引脚呈高阻状态.

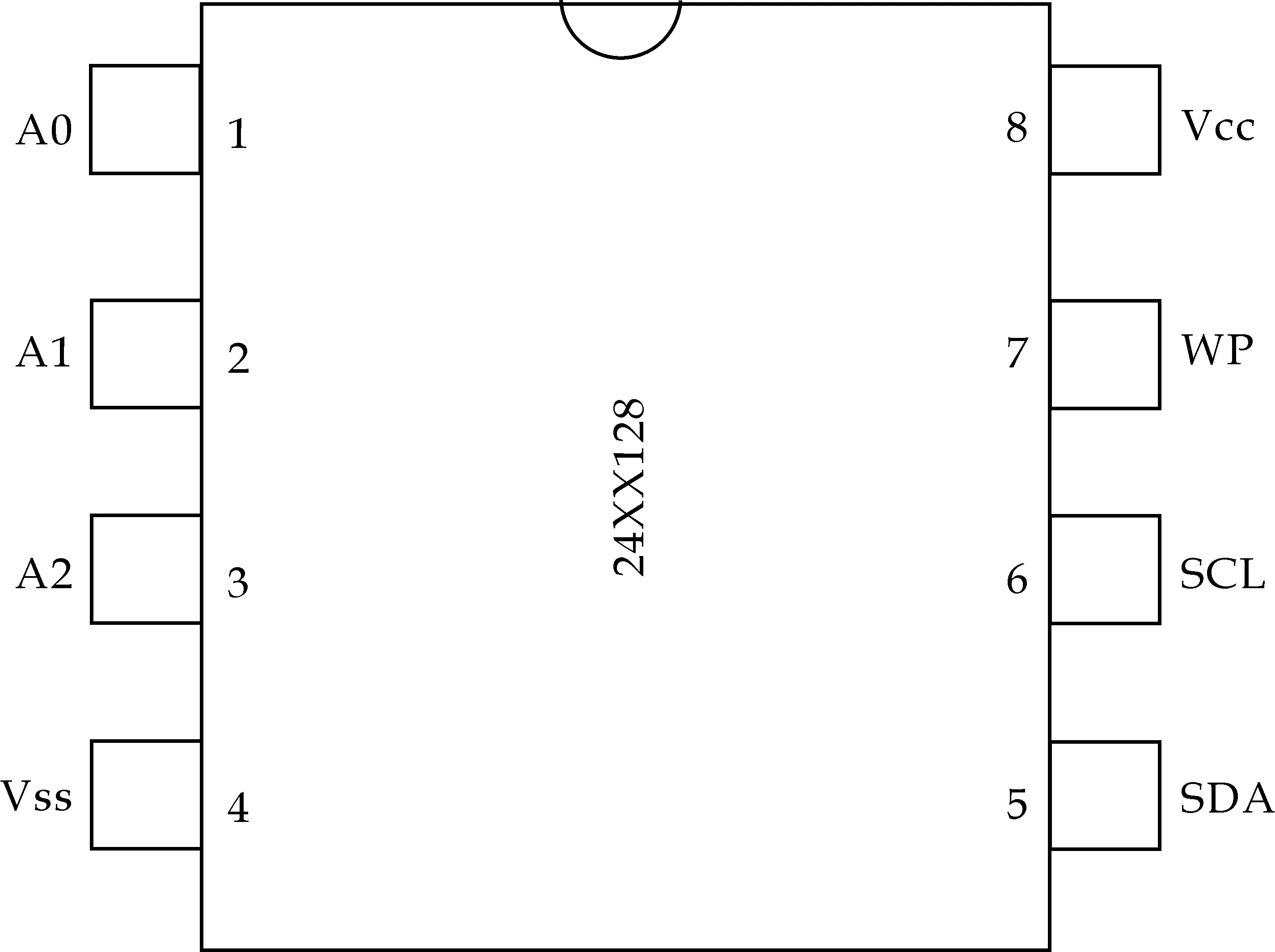

1.3 24C128

FPGA配置存储器选择Microchip基于CMOS工艺, 串行通E2PROM储存器24C128,存储器组织结构128K×8 Bit,最大容量128 Kbits,SOP8封装,供电范围4.5~5.5 V,读写数据最高时钟频率400 KHz,写数据最大电流3 mA,读数据最大电流400 uA,24C128封装引脚如图2所示.

图2 24C128封装及引脚图

A0、A1、A2:器件选择地址输入引脚,最多允许外接8个存储器,不用时允许接地;

Vss:器件接地端;

SDA:I2C串行数据地址输入输出引脚,漏极开路门需接10 K上拉电阻;

SCL:串行时钟输入引脚,同步数据传输,上升沿写数据,下降沿读数据;

WP:读写保护引脚,WP=0数据正常读写,WP=1数据写保护,只读不写;

Vcc:供电引脚,范围4.5~5.5 V.

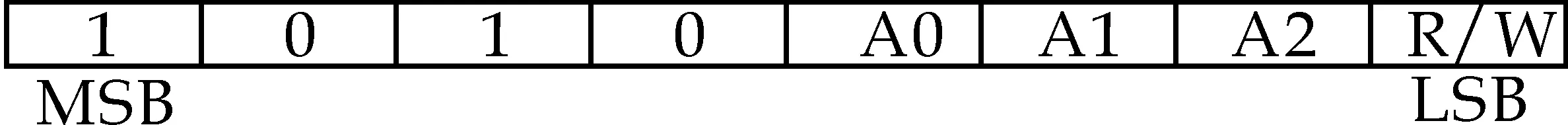

所有串行E2PROM控制位数据前4位都为1010,A0、A1、A2为24C128器件独有地址,R/W器件读写数据控制信号,1读数据,0写数据,控制数据格式如图3所示.对24C128操作,先向24C128写入控制字,再读写数据,数据通信严格按照I2C时序进行.

图3 24C128控制位数据格式

1.4 AT89C2051

MCU选择Atmel公司低电压、高性能CMOS 8位单片机AT89C2051,DIP20封装,片内含2 k bytes只读Flash程序存储器和128 bytes随机存取数据存储器RAM,兼容标准MCS-51指令系统,内置通用8位中央处理器,15个双向输入/输出I/O,两个外中断口,两个16位可编程定时计数器.I2C模式与24C128E2PROM通信,串口模式与FPGA通信,串口采用方式0移位寄存器方式,TXD/P3.1同步通信脉冲,RXD/P3.0同步通行数据,配置数据存储在E2PROM中,单片机发送控制信号从24C128中提取PFGA配置数据,完成引导FPGA配置,配置系统原理如图4所示.

AT89C2051在线编程ISP为74HC373并口下载电路,下载线软件用Easy 51Pro v2.0,并口下载电路下载速度快,过程稳定可靠,电路简单,在实际工程中使用广泛.

图4 配置系统原理图

2 配置系统软件设计

2.1 软件设计思想

Altera Quartus II FPGA开发平台对不同器件有不同的配置文件,配置文件大小和数据格式也不同,JTAG模式对应配置文件.sof,AS模式对应配置文件.pof,单片机配置FPGA两种文件.rbf二进制文件和.ttf十六进制文件, Quartus II不自动产生.ttf文件,具体方法如下:

(1)选择Assignements菜单Setings 下Device;(2)单击Device & Pin Option;(3)Programming Files下Tabular Text file(.ttf)栏打勾;(4)重新编译工程得到.ttf文件.单片机配置FPGA就是将.ttf文件内容按照FPGA配置时序发送到FPGA的SRAM内,.ttf文件用记事本方法打开,将.ttf里配置数据采存储在E2PROM内,通过开辟数组存储的方法,由单片机发送到FPGA,完成FPGA配置.

2.2 程序分析

Altera FPGA在线配置,实际就是将FPGA配置文件转换为51.HEX文件写入单片机,模拟FPGA配置时序将配置文件写入FPGA,C51完成FPGA配置,FPGA用VHDL或Verilog HDL,完成整个应用系统,具体配置程序如下.

#include "reg51.h"

#include "intrins.h"

sbit NSTATUS=P1^3;

sbit CONF_DONE=P1^4;

sbit DCLK0=P1^5;

sbit NCONFIG=P1^6;

sbit DATA0=P1^7;

unsigned char config[ ]={};//放置FPGA配置文件 .ttf内容

void main(void)

{

unsigned char dat,t,k;

NCONFIG=1;//初始化

NSTATUS=1;

CONF_DONE=0;

DCLK0=0;

while(CONF_DONE==0);// CONF_DONE为高,配置结束

{

for(t=0;t<20;t++); //NCONFIG引脚发送一个大于8 uS低脉冲

NCONFIG=0;

_nop()_;_nop()_;_nop()_;_nop()_;//等待FPGA接收信号

for(k=0;k<300;k++)//FPGA接收到NCONFIG信号, NCONFIG,NSTATUS同时为低

NSTATUS=0;

NCONFIG=1;

_nop()_;_nop()_;_nop()_;_nop()_;//NCONFIG引脚跳变为高电平后4 uS后,NSTATUS为高

while(NSTATUS==1);// NSTATUS为高,启动配置

{

for(k=0;k { dat=config[k]; for(t=0;t<8;t++)//配置文件左移,串行送入FPGA { DCLK=0; if(DATA0) DATA0=DATA0|0x01; DCLK=1; dat=dat>>1; DCLK=0; } } } } while(1); } 当今嵌入式系统已应用到各个领域,有必要在成本和体积上进行优化,降低成本.通过AT89C2051单片机模拟FPGA配置时序引导配置FPGA,实践证明配置电路设计完全正确、可行,每次系统上电都能准确、快速完成配置,保证系统保密性和稳定性.Altera公司FPGA器件配置数据时钟有所不同,但单片机配置程序稍加修改即可完成FPGA配置,单片机配置FPGA电路简单、灵活,已广泛应用于各种FPGA应用系统. [1] 王灵芝,林培杰,黄春晖.FPGA的配置及其接口电路[J].电子测量与仪器学报,2007,21(2):109-112. [2] 缪云青,李永刚.FPGA器件在嵌入式系统中的配置方式的探讨[J].微计算机信息,2006,22(11):161-162. [3] 张 玄,李开航.利用CPLD实现FPGA的快速加载[J].现代电子技术,2012,35(22):163-170. [4] 郭利文,邓月明.CPLD/FPGA设计与应用高级教程[M].北京:北京航空航天大学出版社,2011:56-88. [5] 游志宇,张 洪,董秀成,等.MCS-51与FPGA/CPLD总线接口逻辑设计[J].单片机与嵌入式系统应用,2008,23(1):29-31. [6] 马英矫,马瑛蓬,徐 亮.一种共享存储器的FPGA配置电路设计[J].中北大学学报(自然科学版),2012,33(3):272-287. [7] 薛 昀,李宗艳,张德安.基于单片机的FPGA被动串行配置方式[J].桂林电子工业学院学报,2005,25(3):29-33. [8] 李广彪.基于单片机的FPGA并行配置方法[J].电子技术应用,2005,31(1):72-74. [9] 孙进平,王 俊,李 伟,等.DSP/FPGA嵌入式实时处理技术及应用[M].北京:北京航空航天大学出版社,2011:223-245. [10] 包 明.EDA技术与可编程器件的应用[M].北京:北京航空航天大学出版社,2007:173-220. [11] 周立功.EDA实验与实践[M].北京:北京航空航天大学出版社,2007:88-110. [12] 潘 松,黄继业.EDA技术实用教程第四版[M].北京:科学出版社,2010:60-80. [13] 潘 松,黄继业.EDA技术实用教程第三版[M].北京:科学出版社,2006:72-90. [14] 徐志军.EDA技术实用教程第三版[M].北京:电子工业出版社,2009:92-110. [15] 李朝青.嵌入式系统原理与接口技术[M].北京:北京航空航天大学出版社,2005. [16] 张洪润,张亚凡. FPGA/CPLD应用设计200例[M].北京:北京航空航天大学出版社,2009:80-112.3 结论