2.4GHz CMOS低噪声放大器的设计*

2012-12-25唐学锋

唐学锋

(湖州师范学院 信息与工程学院,浙江 湖州 313000)

2.4GHz CMOS低噪声放大器的设计*

唐学锋

(湖州师范学院 信息与工程学院,浙江 湖州 313000)

基于0.18μm CMOS工艺,采用共源共栅源极电感负反馈结构,设计了一个针对蓝牙接收机应用的2.4 GHz低噪声放大器(LNA)电路.分析了电路的主要性能,包括阻抗匹配、噪声、增益与线性度等,并提出了相应的优化设计方法.仿真结果表明,该放大器具有良好的性能指标,在5.4mW功耗下功率增益为18.4 dB,噪声系数为1.935 dB,1dB压缩点为-14 dBm.

低噪声放大器;CMOS;噪声系数

0 引言

随着无线便携式产品如全球定位系统、蓝牙、ZigBee、无线射频识别、无线局域网等的快速发展,无线终端低成本、低功耗、小型化、高性能已成为新的技术目标.近年来,深亚微米和纳米CMOS工艺日趋成熟,其截止频率已经达到几十GHz,并且其相对于bipolar或BiCMOS工艺具有低成本、低功耗的优势.另外,采用CMOS工艺实现的射频前端电路易于与基带部分电路集成在一块芯片上,实现单芯片方案,因此CMOS工艺越来越多地用于无线通信产品.

蓝牙是一种支持设备短距离通信(一般10m内)的无线电技术,能在包括移动电话、PDA、无线耳机、笔记本电脑和其他便携式设备之间进行无线信息交换.蓝牙工作在全球通用的2.4GHz ISM频段,其数据速率为1Mbps.低功耗、小体积以及低成本的芯片解决方案,使得蓝牙技术甚至可以应用于极微小的便携设备中.用CMOS工艺设计低成本、低功耗、高集成度的蓝牙接收机芯片已成为当前研究的一个热点[1,2].

本文设计了一个针对蓝牙接收机应用的2.4GHz CMOS低噪声放大器(LNA),通过参数优化,得到了较好的仿真效果,具有实用的参考价值.

1 电路结构

LNA位于射频接收系统的最前端,它的性能对整个接收机系统的性能起着至关重要的作用.它的功能是在尽可能低地产生噪声的前提下,提供足够的增益放大输入射频信号,以降低后续各级电路产生的噪声对信号的影响.除了低噪声和高增益,LNA还应该具有较高的线性度以适应输入信号的变化,良好的输入阻抗匹配以实现最大功率传输.由于是便携式蓝牙应用,LNA应当保持低功耗.

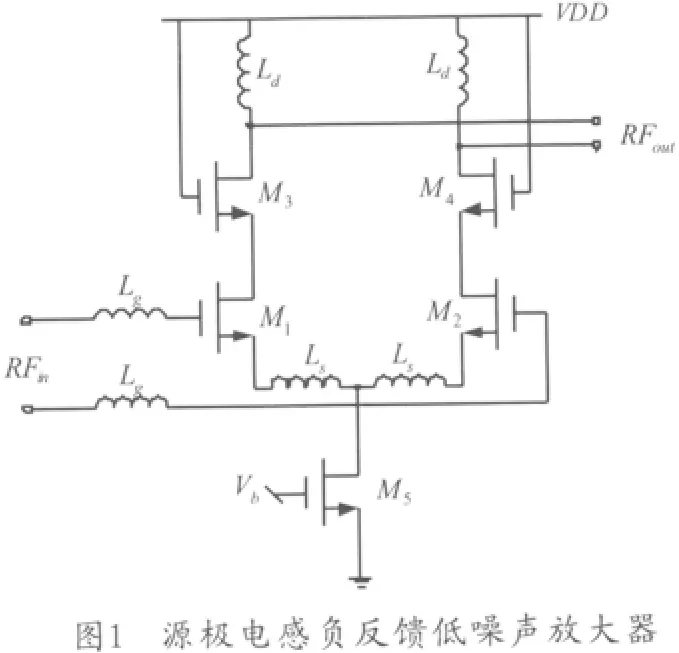

为了满足上述指标,本文采用图1所示的带源极电感负反馈共源共栅结构放大器,该结构有利于获得高增益和低噪声系数.M1、M2为共源放大管,给电路提供足够的增益.M3和M4为级联共栅晶体管,用来减小由M1/M2的栅漏极间电容Cgd引起的Miller效应和有限输出阻抗对放大器性能的影响,并提供良好的输入输出反向隔离度,避免稳定性问题.栅极电感Lg和源极电感Ls用于输入阻抗匹配.电感Ld与输出节点寄生电容及后级混频器输入容抗在工作频率附近形成谐振,提供一个谐振负载RD.LNA采用全差分结构,差分结构可以较好地抑制共模噪声,提高线性度.

2 电路分析

2.1 阻抗匹配

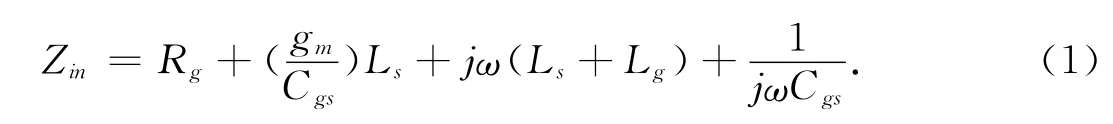

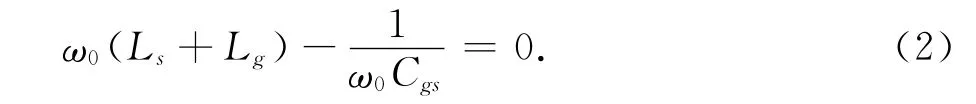

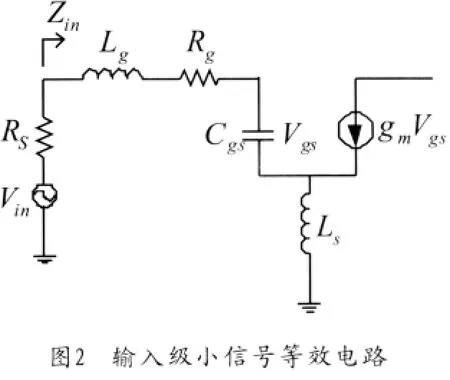

LNA的前级电路一般为分立的射频带通滤波器,输出阻抗一般为50Ω.由于滤波器的传输特性与终端所接负载有很大关系,因此LNA的输入端要实现对50Ω信号源阻抗的良好匹配,以减小信号反射,实现最大功率传输.图2为源极电感负反馈共源共栅放大器的输入级小信号等效电路.根据等效电路,计算得到输入阻抗为[3]:

谐振时:

式中,gm是共源MOS管M1/M2的跨导,Rg是栅分布电阻,Cgs是栅源寄生电容.通过选择适当的偏置条件和源极电感Ls,使输入阻抗得到一个50Ω的实部;再通过选择适当的栅极电感Lg使得输入回路在工作频率附近谐振,使得输入阻抗的虚部为0,从而实现阻抗匹配.这种结构最大的优点是采用电感来得到50Ω的输入阻抗,由于理想电感不会引入额外的噪声,同时通过合理设计,可以在功耗受限条件下做到近似的噪声匹配,于是即实现了阻抗匹配,又满足了低噪声的要求.这种结构实现的是窄带匹配,实际应用时需要在输入端加ESD保护电路,另外还需焊盘和键合线与外界相连,这些都会引入寄生电容和电感,使输入匹配发生偏移,因此在设计时要仔细考虑这些寄生的影响.

2.2 噪声

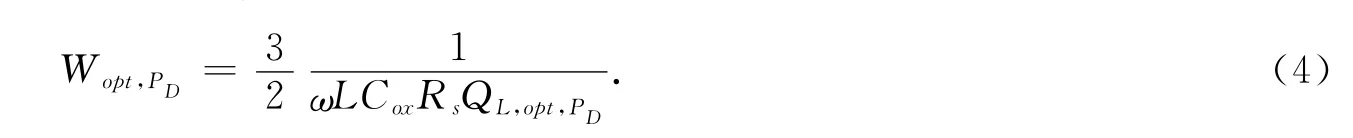

LNA是射频接收机的第一级,根据级联系统噪声公式,它的噪声系数在整个系统中占主导地位.经典两端口网络噪声理论指出,当输入信号源阻抗Zs等于电路最优信号源阻抗Zopt时,电路可以获得最佳噪声性能.在LNA设计中,源阻抗Zs一般是固定不变的(50Ω).本文采用的LNA结构可以在限定功耗条件下,通过优化输入共源级MOS管器件尺寸和偏置条件做到近似的噪声匹配(Zs=Zopt),从而取得较好的噪声性能.通过推导得到使噪声最优的晶体管栅宽[4]:

因此:

根据优化的MOS管器件宽度,得到在功耗PD受限条件下获得的最小噪声系数为:

式中,ωT是MOS管的截止频率,γ是MOS管沟道热噪声系数.公式5中只考虑了MOS管的沟道热噪声,除此之外,栅分布电阻Rg和栅极电感Lg寄生电阻Rl是另外两个噪声源.栅分布电阻引入的热噪声可以在版图实现时采用多指晶体管技术来减小,以提高栅极电感Lg的Q值,有效降低噪声系数.目前芯片代工厂提供的基于CMOS工艺的硅基片上平面螺旋电感Q值不高,大约在10~15左右,对噪声性能有一定的影响.栅极电感Lg值比较大,会占用较大芯片面积,可考虑采用片外贴片电感实现.

2.3 增益与线性度

LNA必须提供足够的增益放大来自天线的微弱信号,同时大的增益也能抑制后续级的噪声.但与LNA级联的混频器对线性度有很高要求,所以要求LNA的增益不宜过大,太大了容易使混频器产生过载.本文设计的LNA的增益可以表示为:

式中,Q是输入匹配谐振回路的品质因子,Gm是输入MOS管等效跨导,RD是输出谐振负载.

采用源极电感Ls做负反馈,负反馈能提高放大器的线性度,但会减小输入MOS管等效跨导Gm,降低LNA增益.另外,增加输入MOS管的过驱动电压VGS-VTH也可以提高线性度,但这是以降低MOS管等效跨导Gm为代价的.因此增益和线性度是相互制约的关系,在设计LNA的过程中应对两者进行折衷考虑[5].

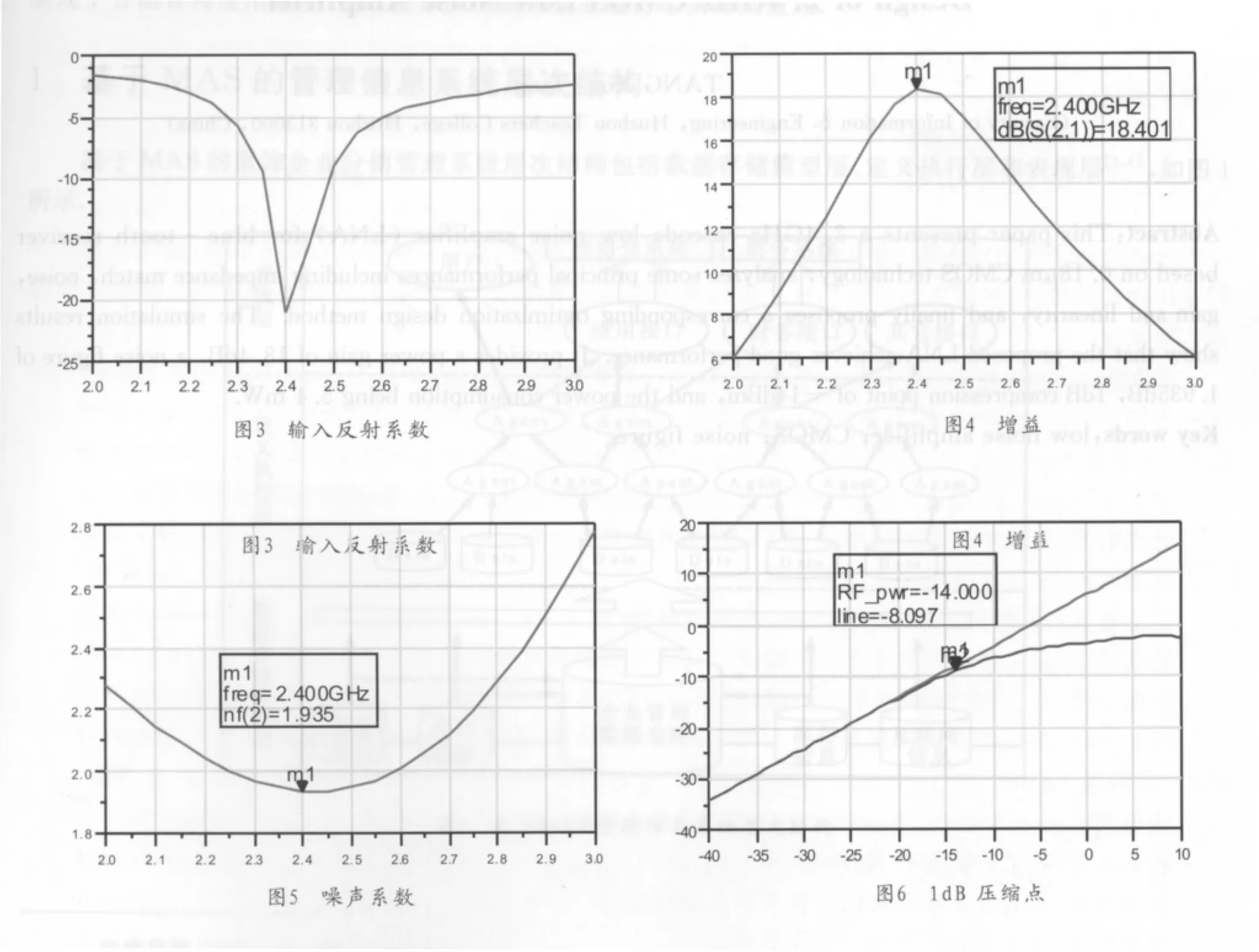

3 电路仿真

使用Agilent公司射频仿真软件ADS2009和CMOS 0.18μm工艺模型进行电路优化仿真.ADS2009软件可以提供给电路设计者进行模拟、射频与微波等电路的仿真设计.由图3可以看出,在2.4GHz时输入反射系数S11小于-20dB,达到了较好的输入匹配.如图4所示,放大器的增益S21达到18.4dB,可以有效地放大输入射频信号和抑制后续模块噪声.图5给出了输出噪声系数NF为1.935dB,噪声系数曲线走向比较平缓.使用谐波平衡法对电路进行线性度仿真,得到1dB压缩点为-14dBm,如图6所示,LNA具有较好的线性度.电路使用1.8V电源电压,功率消耗为5.4m W.

4 结论

本文深入分析了带源极电感负反馈共源共栅结构LNA的各项性能,从阻抗匹配、噪声系数等方面对电路的性能进行了优化.采用0.18μm CMOS工艺设计了针对蓝牙接收机应用的2.4GHz LNA.运用ADS2009软件对电路进行了仿真优化,仿真结果表明本文设计的LNA在较低的功耗下,保持了良好的输入阻抗匹配,同时达到了高增益和低噪声系数.

[1]Jenn-Tzer Yang.A CMOS Radio Frequency Receiver for Bluetooth Applications [C]//1st Asia Symposium on Quality Electronic Design.Penang,Malaysia,2009:352~356.

[2]BEFFA F,VOGTET R.A 6.5mW receiver f ront-end for bluetooth in 0.18μm CMOS [C]//IEEE Radio Frequency Integer Circuit Symp.Seattle,WA,USA,2002:391~394.

[3]THOMAS H L.The Design of CMOS Radio-Frequency Integrated Circuits [M].Cambridge University Press,2006:364~400.

[4]THOMAS H L,DEREK K S.A 1.5V,1.5GHz CMOS Low Noise Amplifier[J].IEEE Journal of Solid-State Circuits,1997,32(5):1~16.

[5]徐跃,杨英强.1V 高线性度2.4GHz CMOS低噪声放大器 [J].电路与系统学报,2009,14(4):97~100.

Design of 2.4GHz CMOS Low Noise Amplifier

TANG Xue-feng

(Faculty of Information &Engineering,Huzhou Teachers College,Huzhou 313000,China)

This paper presents a 2.4GHz cascode low noise amplifier(LNA)for blue-tooth receiver based on 0.18μm CMOS technology,analyzes some principal performances including impedance match,noise,gain and linearity,and finally proposes a corresponding optimization design method.The simulation results show that the proposed LNA achieves good performance.It provides a power gain of 18.4dB,a noise figure of 1.935dB,1dB compression point of-14dBm,and the power consumption being 5.4 mW.

low noise amplifier;CMOS;noise figure

TN 722.3

A

1009-1734(2012)01-0053-04

2011-12-06

唐学锋,实验师,从事模拟电路研究.