基于NAND Flash 的海量存储器的设计*

2012-12-22舒文丽吴云峰孙长胜吴华君

舒文丽,吴云峰 ,孙长胜,吴华君,唐 斌

(电子科技大学光电信息学院,成都610051)

数据采集存储系统是现代电子系统的重要组成部分,在通信、雷达、航天等领域都有着广泛的应用[1]。由于图像的分辨率和采样率大幅提升[2],高速海量数据的存储问题成为研究的热点。随着半导体技术的发展,固态存储器以其优异的性能逐渐成为数据存储系统的首选存储介质[1],其中以闪速存储器(Flash Memory)发展的最快。Flash 根据芯片内部逻辑架构设计上的差异主要分为NOR Flash 和NAND Flash 两种[3]。相比于NOR Flash,NAND Flash 具有访问速度快、成本低、容量大、功耗低等诸多的优势,在大容量存储系统中得到广泛应用,本文的海量存储板就是基于NAND Flash 设计的。但是NAND Flash的读写速度不快,读带宽为17 Mbyte/s,写带宽为6.8 Mbyte/s[4],考虑到存储系统对带宽的要求,本文采用FPGA 同时控制多片NAND Flash 的读写操作以增加带宽。

1 存储器的硬件设计方案

本存储器的设计指标是:Camera Link 高级模式的数据输入;600 Mbyte/s 数据存储速度;30 min 的连续存储时间;掉电数据不丢失;抗震性;容量可扩展性。NAND Flash 存储系统要完成存储数据操作需要实现两个方面的功能:一是实现具体的存储器接口与存储系统的数据交换;二是实现存储系统的数据管理[5]。基于以上指标,本存储器分为接口板和存储板。

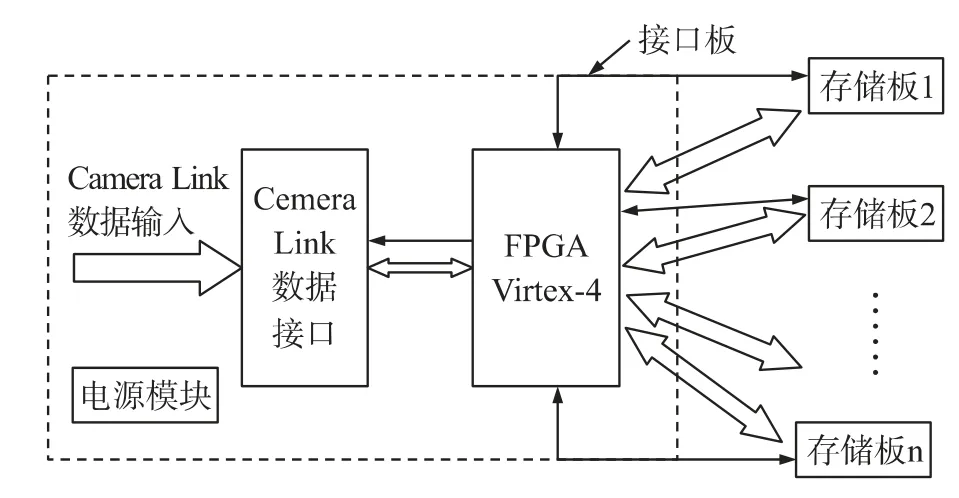

1.1 接口板设计

接口板完成的任务是将Camera Link 数据信号接收进来,然后通过FPGA 分配数据信号。分配数据信号主要是要选择可用的存储板,将数据信号传输进去。在读取数据信号时,接收相机控制信号选择需要读取的存储板,并将里面的数据读出。

输入部分首先是Camera Link 接口部分三片DS90CR286 接收数据信号、一片DS90LV047A 作为相机控制信号(Camera Control 1 ~4)的发送端、一个MDR-26 接头、一个MDR-20 接头。采用I/O 口最多的XC4VLX100-FF1513 型号的Virtex-4 FPGA芯片作为数据输入分配模块,同时控制Camera Link接收芯片。

操作过程描述:

首先Camera Link 数据接口模块接收到接口传输过来的LVDS 信号,将其转换为64 bit 数据信号和相机控制信号。然后在Virtex-4 FPGA 里面做一个双口RAM 将存储进来的数据写入RAM。接下来,按照Virtex-4 FPGA 里面存储的信息选择可用的存储板,将数据从RAM 的另一口读出,存入存储板。接口板的框图如图1 所示。

图1 接口板框图

1.2 存储板设计

存储板完成的任务是接收接口板的数据信号和控制信号,将数据存入NAND Flash 芯片中。在读取数据时,按照顺序读取板上NAND Flash 里面的数据信号,并通过主FPGA 芯片传入接口板。

接收到存储板传来的数据和控制信号,每块存储板采用4 片FPGA(1 片Virtex-4 和3 片Spartan- 3)的设计结构。首先使用型号为XC4VLX25-FF668 速度较快的Virtex-4 FPGA 芯片接收,其指标为:448 个可用IO、1296 kbit 的内部Block RAM。然后使用型号为XC3S4000 -FG900 的Spartan-3 芯片直接控制NAND Flash 芯片,其可用管脚数为633。NAND Flash 芯片是三星公司的K9WBG08U1M,单片大小为4 Gbyte,单片速度为15 Mbyte/s。每片Spartan-3 可以控制48 片4 Gbyte 的NAND Flash,这样一款存储板就有4 G×48×3=576 GBytes 的存储容量,两块存储板就可以完成30 min 的数据存储。48 片NAND Flash 芯片并行存储,分担600 Mbyte/s 的数据速度,每片所需的存储速度为12.5 Mbyte/s,该芯片完全能够完成这个指标,具体连接方式如图2 所示。

图2 FPGA 与一组Flash 的连接方式

操作过程描述:

首先接受接口板的选择传输信号后,使能板上NAND Flash 芯片的写入模式,接收64 bit 数据信号,存入接口板主FPGA Virtex-4 芯片,再按顺序存入3 片从FPGA Spartan-3 芯片。在接收到接口板的读取数据信号时,使能使能板上NAND Flash 芯片的读取模式,按顺序从3 片从FPGA 芯片中读取数据信号,传入主FPGA 芯片,再传入接口板。存储板的框图如图3 所示。

图3 存储板框图

2 存储器的软件设计

在搭建好硬件平台以后,需要编写相应的程序代码实现系统的逻辑功能,主要包括两个部分:一是根据具体的存储器接口编写合适的程序实现从存储器接口读取当前的操作命令和实现NAND Flash 闪存系统与存储器接口之间的数据交换,二是存储系统的数据管理,主要指NAND Flash 闪存数据管理[5]。NAND Flash闪存数据管理是闪存存储系统的关键,主要包括坏块管理,损耗均衡和ECC 校验[6-8]。

2.1 坏块管理

坏块是指一个块内含有一位或多位数据单元无法进行操作的块单元,分为固有坏块和使用坏块。由于生产工艺的限制,NAND Flash 在出厂的时候允许存在一定量的坏块,称为固有坏块。在芯片的长期使用过程中也会产生新的坏块,称为使用坏块。如果信息存储在坏块中,会导致信息的丢失,所以在对NAND Flash 操作过程中要编写程序对坏块进行管理,保证信息的准确性。坏块管理包括坏块识别,坏块存储,坏块跳过和坏块替换。

2.1.1 坏块识别和存储

要对NAND Flash 的坏块进行管理,首先要识别并存储坏块的位置。第一次上电的时候,通过坏块识别函数,检测NAND Flash 的固有坏块,建立坏块信息表,存储坏块的位置。

2.1.2 坏块跳过

以后每次对NAND Flash 进行操作时,先调用有效块检测函数,也就是和坏块信息表的内容做比较。如果检测到该块是坏块就直接加1 跳过,否则就把该块的地址存储在建好的RAM 中,用来存储数据。这样在对NAND Flash 进行操作的过程中,RAM 中始终存储着下一个待用的有效块地址。

2.1.3 坏块替换

当对NAND Flash 进行写操作或擦除操作时,可以根据状态寄存器判断Flash 的运行是否成功,当状态寄存器接收到错误信息时,这个块就会被认为是坏块,写操作或擦除操作就是无效的,这时就要用好块替换坏块。由于在同一块中某一页的操作失败不会影响其他页数据的正确性,所以可以重新写入无效页的正确数据,通过控制器缓存,连同块中的其它页的数据一起拷贝到下一个有效块中,避免信息丢失。

图4 坏块替换

考虑到本设计中采用48 片NAND Flash 并行操作,FPGA 同时控制48 片NAND Flash。如果采用传统的坏块跳过方法,将48 块Flash 的所有有效块的地址全部存储在建好的RAM 中,会占用FPGA 大量的资源。本文提到的坏块跳过方法,通过不断地调用有效块检测函数,每次只存储48 个有效块地址即每片NAND Flash 只需存储一个有效块地址,这样避免占用太多的FPGA 资源。

2.2 损耗均衡

尽管NAND Flash 的每个单元块相互独立,且每块一般可擦除次数高达100×104次,但是随着擦写次数增加,会有一些单元块逐渐变得不稳定或失效从而形成永久性坏块。损耗均衡的原理是在数据需要更新时,不是在原来的数据块上重写,而是直接把新数据写入一个空块中,再把原来的块擦除[10],损耗均衡原理如图5 所示。因此,要避免对某些块的频繁操作,尽量做到操作次数均衡,以达到NAND Flash 的最长使用寿命。

图5 损耗均衡原理图

2.3 ECC 校验

ECC(Error Checking & Correction)校验,又叫错误检查校正。对NAND Flash 进行操作时,为了保证数据的准确性,本文采用ECC 校验操作。ECC 校验码存放在NAND Flash 的备用空间内,通过ECC 校验,可以有效地纠正或检测出误码,从而保护用户存放的数据[9]。

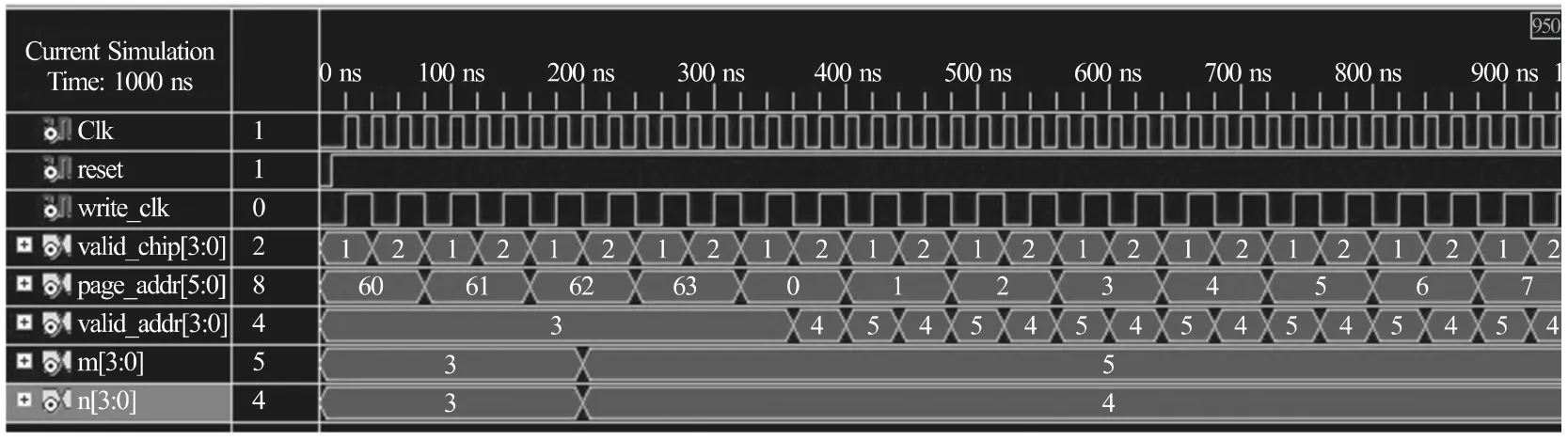

3 实验仿真

本存储系统以Xilinx 公司的Virtex-4 FPGA 作为控制核心,NAND Flash 采用48 行3 列的阵列式,每一列的48 片Flash 并行操作以增加位宽,3 列之间采用流水线技术进行操作。每一行的Flash 共用I/O,每一列共用片选信号,每一列的R/B 信号相与后送给FPGA,其他信号共用。

为了便于观察,图6 只设置了第1 列和第2 列Flash 交替操作,并将第1 列的第4 块假设为坏块,valid_addr 为调用有效块检测函数后得到的有效块地址,valid_chip 为流水线操作的Falsh 芯片地址,page_addr 为页地址,m 和n 为中间变量。上电时先将第4 块存到坏块表中,然后对第3 块进行操作的过程中调用有效块检测函数确定下一有效块地址。对第3 块的64 页操作完成后,第一列Flash 直接从第3 块跳过第5 块,跳过坏块4,而第2 列Flash 继续对第4 块进行操作。

图6 仿真波形

4 结论

随着NAND Flash 的存储密度越来越大,体积、功耗和成本却越来越小,NAND Flash 在不同的领域都得到了广泛的应用。本文针对单片Flash 存储速度慢的缺点,将多片Flash 并行起来工作,使得存储速度大大提高。针对坏块管理问题,本文提出了一种新的坏块跳过方法,通过不断调用有效块检测函数,可以跳过坏块,将有效块地址存储在已建好的RAM 中,对NAND Flash 操作时直接读取有效块地址,对坏块进行了管理,保证了存储器数据的可靠性。

[1] 雷磊.NAND 型Flash 海量存储系统的设计与实现[D].硕士论文.北京理工大学,2008.

[2] 朱知博.基于NAND Flash 的高速大容量存储系统设计[J].现代电子技术,2011,34(8):170-173.

[3] 陈国,高杨. NAND Flash 在大容量存储技术中的应用[J]. 航天计算技术,2009,39(2):113-116.

[4] 雷磊,谢民,李先楚.基于NAND 型Flash 海量存储系统的设计与实现[J].测控技术,2007,26:196-202.

[5] 晏敏,龙小奇,章兢,等.开放式大容量NAND Flash 数据存储系统设计与实现[J].微电子学与计算机,2009,26(11):13-16.

[6] Li Seung Ho,Park Lim Kyu Ho. An Efficient NAND Flash Files System for Flash Memory Storage[J]. IEEE Transaction on Computers,2006,55(7):906-912.

[7] 陶翼,晏轲,曹国梁.JFFS2 文件系统的闪存管理策略改进[J].计算机与数字工程,2008,36(6):64-66.

[8] 罗晓,刘昊.一种基FAT 文件系统的NAND Flash 坏块处理方法[J].电子器件,2008,31(2):716-719.

[9] 刘恕. NAND Flash 的ECC 分级及ATE 设备中的测试方法[C]//第五届中国测试学术会议论文集.2008:401-403.

[10] 林刚.NAND Flash 坏块管理算法及逻辑层驱动设计[D].硕士论文.西安电子科技大学,2009.