多码率并行LDPC编码器的设计与实现

2012-11-26章坚武包建荣许晓荣

王 博,章坚武,包建荣,许晓荣

(杭州电子科技大学通信工程学院,浙江杭州310018)

0 引言

低密度奇偶校验码(Low Density Parity Check Code,LDPC)有逼近香农极限的纠错性能、译码复杂度低、结构灵活等优点[1],受到了人们的广泛关注,并成功应用到了多个行业标准,如第二代卫星数字广播中采用了BCH码和LDPC码级联的方案[2]。空间数据系统咨询委员会(Consultative Committee for Space Data Systems,CCSDS)发布的131.1-0-2标准也推荐了2类 LDPC 码[3]。LDPC 码可分为随机构造的LDPC码和结构化的LDPC码两大类[4]。本文主要根据其编码矩阵的结构,设计了一个码率可选的多码率并行编码器,并进行了分析和验证,说明了该方案具有资源少,算法简单,易工程实现等优势。

1 深空通信中的LDPC码标准

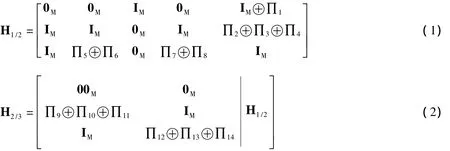

CCSDS推荐的深空通信的LDPC码的生成矩阵是分块循环的,故具有编码复杂度低的优点。该系列LDPC码有1/2、2/3、3/4、4/5共4种码率,各个码率校验矩阵H的定义如下所示[3]:

式中,0M和IM分别是M阶零矩阵和单位矩阵,Π1~Π26是置换矩阵。Πk在i行Πk(i)列有非零元素,i∈{0,…,M-1},在M阶的置换矩阵Πk中,包括16个m的小矩阵块(m=M/4)。其中,关于子矩阵阶次M的可取值和Πk(i)的计算见CCSDS实验规范中的推荐标准[3]。独立进行校验矩阵计算,得出该系列码具有兼容结构的生成矩阵,且该矩阵具有准循环结构。即高码率生成矩阵包含了低码率生成矩阵。

2 多码率并行编码器的设计

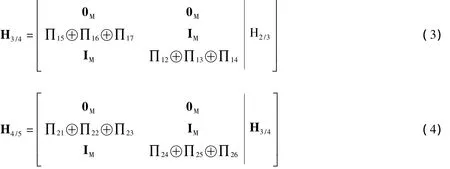

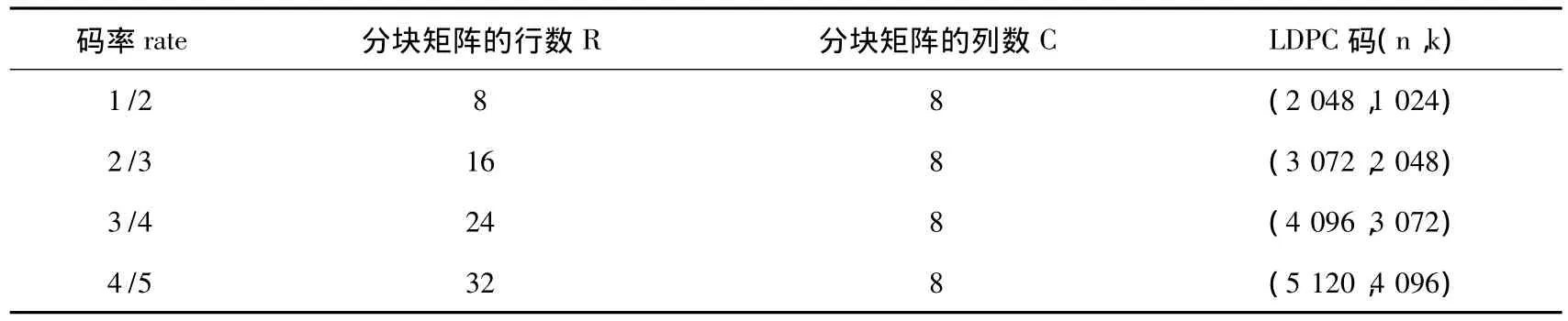

本设计支持4种码率、8路并行编码。参数如下:M=512,分块循环生成矩阵中子循环矩阵的维数m=128,对应的4种码率的参数如表1所示:

表1中,分块矩阵的行、列数只包计算校验比特的那部分生成矩阵,生成矩阵具有系统形式G=[I W],分块矩阵的行、列数也就是W中分块矩阵的行、列数。

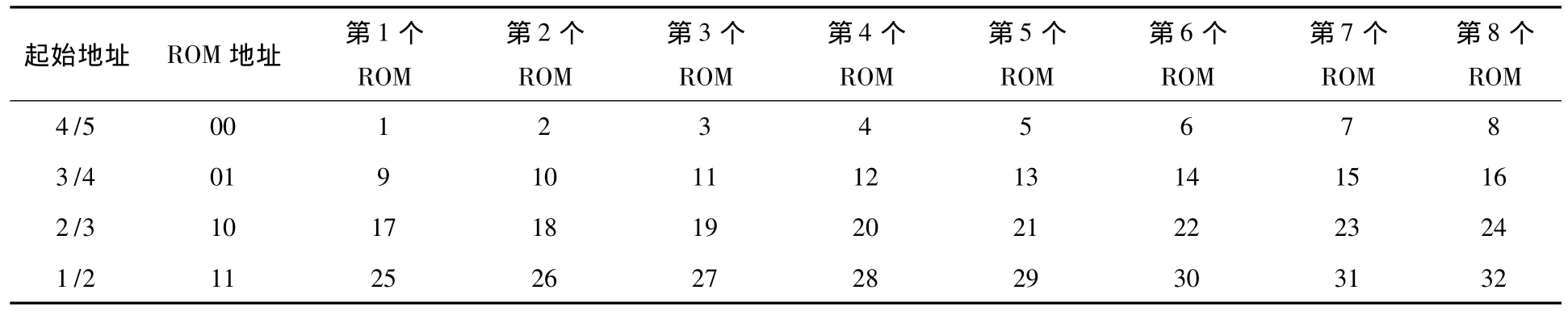

表1 各个码率的具体参数表

编码器的原理框图如图1所示。

图1 8路并行编码器原理框图

2.1 串/并和并/串转换模块的设计

在准循环码并行编码时,每个子循环矩阵能完成连续128(m=128)个信息比特的计算。所以,在此的串并转换模块不能简单地将连续进入的8个信息比特并行输出,而需特殊设计处理。在该模块里需要设置8个存储器,对应8路并行数据,且定义每1 024比特为1帧。串并模块的具体工作原理是:信息比特的第1个128位数据按序存入第1个存储器中,依次类推,直到第1帧的第8个128位存入第8个存储器中,此时才可输出并行信号。

并/串转换模块可以看成串/并转换模块的逆功能,同样需要特殊设计。模块里设置了8个大小相同的存储器,并行输入数据第1路到第8路分别存入第1个到第8个存储器。当存入1帧数据后,输出使能信号置为高,表示可以输出串行数据,这时候依次输出第1到第8个存储器数据。

2.2 存储模块的设计

生成矩阵具有兼容结构,为了减少矩阵存储量,只需存储4/5码率W矩阵中每行数据。为了便于8路并行编码寻址和降低地址信号的控制复杂度,数据分8个ROM存储,这样每个ROM位宽1 024位,深度为4(32/8=4),因此可用2位地址表示。ROM的存储结构如表2所示。表2中每个ROM下的数字代表4/5码率W矩阵中行号为该数字的数据。1/2码率的生成矩阵只用到了4/5码率W矩阵中最后8行数据,因此1/2码率的W矩阵起始地址是从每个ROM的“11”开始的,对应第25行到32行数据。同理,2/3码率的起始地址是“10”,3/4码率的起始地址为“01”,4/5码率起始地址是“00”。经过这样设计后,地址数据的控制是相当简单的,不同码率只需赋于不同起始地址即可,降低了系统实现复杂度。

表2 存储ROM地址分配

2.3 编码控制模块的设计

为了进一步降低系统实现复杂度,减少FPGA资源的利用,编码时二进制矩阵乘法运算可以化为简单的二进制异或运算,而不需使用乘法器。编码开始首先将校验位寄存器初始化为零,然后在每来8个并行信息比特时,将8个信息比特中非零元素对应的W矩阵行数据和校验比特寄存器进行模二和的累加运算,即异或运算,结果存入校验比特寄存器中,在一个码字中所有k个信息比特到来后,校验比特寄存器异或的结果就是该码字的校验位了,可以开始输出该码字的检验位了。

编码控制模块的仿真波形如图3所示。

图2 编码控制模块的仿真波形

在图2中rate为码率选择信号,由于篇幅有限,这里只给出4/5码率仿真图。Encode_En为编码使能信号,高电平时编码,编码完成后置为低电平,输出校验位。在图2中开始时Encode_En为1,输出dout的码字与信息比特din完全相同,只是相差一个时钟周期。

3 FPGA资源使用情况

硬件实现平台采用Xilinx公司的Virtex-6(XC6VLX240T)芯片,该芯片资源丰富,完全能满足多码率并行编码资源的消耗。LDPC码编码器硬件资源主要消耗在生成矩阵存储单元和编码电路所占用逻辑资源上[5],如表3所示为ISE 13.2开发环境给出的资源利用报告。

表3 芯片的资源使用情况

由表3可见,编码器在占用较少资源的情况下,实现了4种码率的8路并行编码,达到设计要求。

4 结束语

本文对CCSDS标准中适用于深空通信的系列LDPC码,设计了一个能够实现可选码率的多码率(4种码率)并行通用编码器,增强了系统的适用性,提高了编码数据速率,而具有一定的实用价值。从表3可见XC6VLX240T芯片资源丰富,因此还可用更高的并行路数以提高系统吞吐量。

[1] Chung SY.On the Design of Low Density Parity Check Codes Within 0.0045dB of the Shannon Limit[J].IEEECommun Letters,2001,5(2):58 -60.

[2] DVB-S2 Standard Draft ETSIEN 302 307 V1.1.1[S].2004.

[3] CCSDS.Low Density Parity Check Codes for Use in Near Earth and Deep Space Applications[S].CCSDS 131.1-O-2,Orange Book.Issue 2,2007.

[4] Macky D JC.Good error-correcting codes based on very sparse matrices[J].IEEE Trans on Inform Theory,1999,45(2):399-432.

[5] Zhang Huxing,Yu Hongyang.Multi-rate QC-LDPC Encoder[J].IEEE Trans on Inform Theory,2009,(4):1 -4.