一种基于ADS5232的高速数据采集电路的设计方法

2012-11-26程耀林

程耀林

(中南民族大学电子信息工程学院,武汉430074)

对于高清图像、高清视频应用设备以及对测量带宽和精度有一定要求的测量仪器而言,需要选择有一定精度的高速ADC芯片来完成模拟信号的采样.如果同时希望简化PCB的设计,则使用TI公司的高速ADC芯片ADS5232是一个不错的选择.该芯片每个通道的最高采样速率达到65MS/s,精度为12bit,将2个采样通道集成在一个芯片内,而且提供内部参考电压[1],可以省去外部参考电压产生电路,从而大大简化了设计.高速数据采集需要高速控制,高速缓冲.CPU的串行处理机制决定了它不能实现高速控制,所以一般使用FPGA来控制,但更高的采样速度FPGA也不能控制,只能使用专用芯片控制.而ADS5232的采样速度决定了它使用FPGA来控制非常合适.

1 系统设计

ADS5232的功能、信号和参数等详细说明可参看其数据手册[1],例如,其模拟电源和数字电源供电电压都是3.3V.差分模拟输入的波动范围为1.5~2.0Vpp,DNL= ± 0.3LSB,TQFP-64 封装.参考电压可选内部,也可选外部,使用内部参考电压时功耗371mW,使用外部参考电压时功耗335mW,对于2路高速采样的ADC芯片有此功耗并不高.

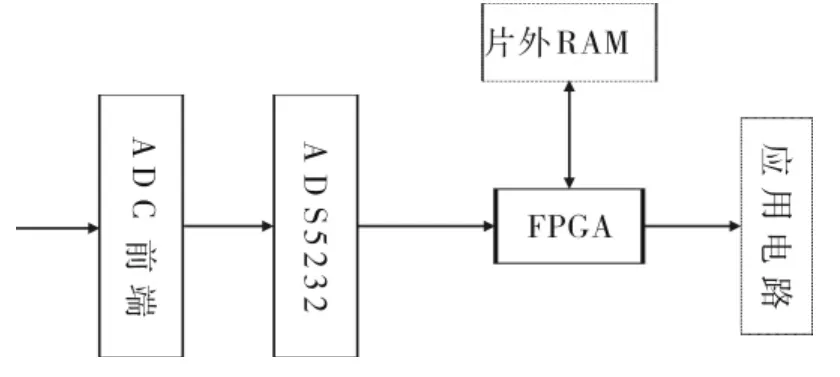

基于该芯片的高速采集电路系统设计如图1所示.芯片的2路模拟信号输入要求是差分信号,ADC前端模块的功能是把外部的单端模拟信号转化为符合芯片要求的差分信号,包括电压的要求.ADS5232完成模数转换,FPGA主要实现对ADS5232的控制和输出数据的缓冲,同时实现对外部应用电路的接口.ADS5232和FPGA都使用3.3V电源,可直接相连,不需要电平转换电路.数据缓冲区可以使用FPGA片内双口RAM来配置一个FIFO实现,如果要求缓冲区比较大,可以连接片外RAM来实现,但增加了设计的难度.片外RAM有2种可以选择,一种是SRAM,容量比较小,但接口比较简单,易于实现.另外一种是SDRAM,容量大,但接口比较复杂,实现难度大.使用片内的RAM最方便,适合于对缓冲区要求不大的场合.外部应用电路是指将模数转换后的数据作为输入的应用电路,例如,示波器、图像处理等模块.本设计是一种实现高速采样并提供数据缓冲和接口的应用平台,可以和各种高速数据处理电路(即外部应用电路)进行可编程的连接.本文的设计只涉及ADC前端模块、ADS5232模块和FPGA模块.

图1 系统结构框图Fig.1 System structure block diagram

在此系统设计中还要注意如下3个问题.

(1)同步设计.整个系统要采用同步设计,包括外部应用电路在内,即所有模块要使用一个时钟源产生的时钟.同步设计可以提高系统的稳定性,避免数据丢失等错误[2].

(2)PCB设计.PCB设计要符合高速电路的设计要求.为了保证高速电路信号的质量,要求使用4层版.高速PCB的设计要考虑的因素很多,其目的是尽量减少高速信号的干扰和寄生电容、电感的影响,例如时钟线要尽量短,且两边都布地线,去耦电容要靠近电源引脚,且使用小封装0603,高速信号线要避免走比较长的平行线等等[2].

(3)采集数据的处理.ADS5232是连续采样,但FPGA内部的缓冲区大小有限,而应用电路的处理速度和具体应用有关.如果能够实现连续、实时处理,可以不需要缓冲区,直接从ADS5232取数.如果处理速度有限,不能连续、实时处理,则只能以一个缓冲区的数据大小(即存储深度)为单位进行处理,例如示波器的波形显示,一幅波形显示的刚好是缓冲区的数据,所以,缓冲区数据的刷新频率决定了波形刷新的频率.对缓冲区的安排需要考虑到ADS5232可以实现2路模拟信号的同步采样.

2 模块设计

2.1 ADC 前端设计

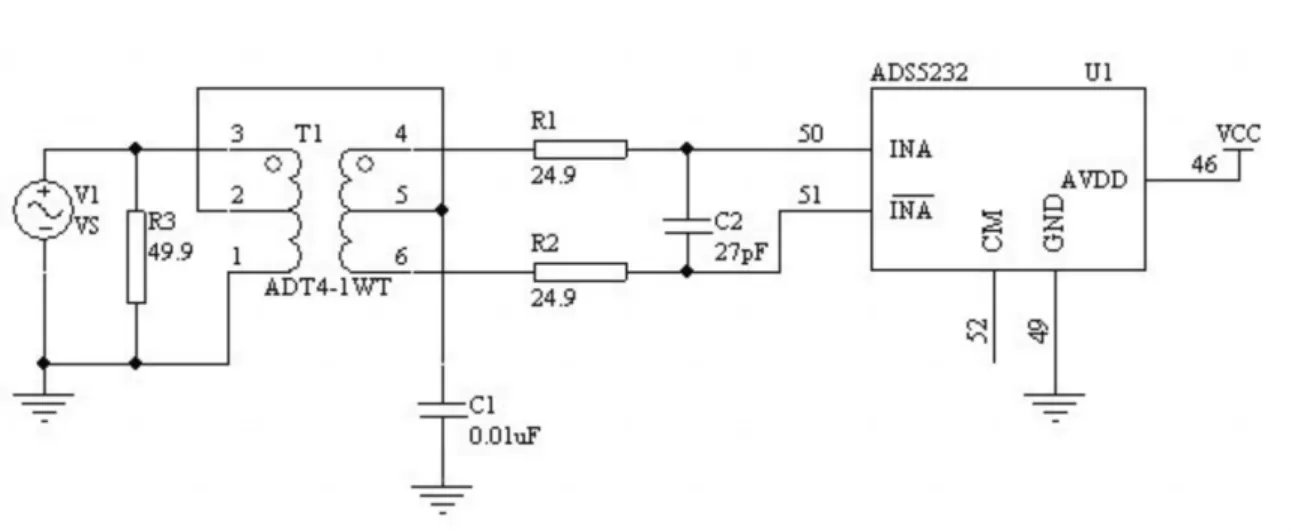

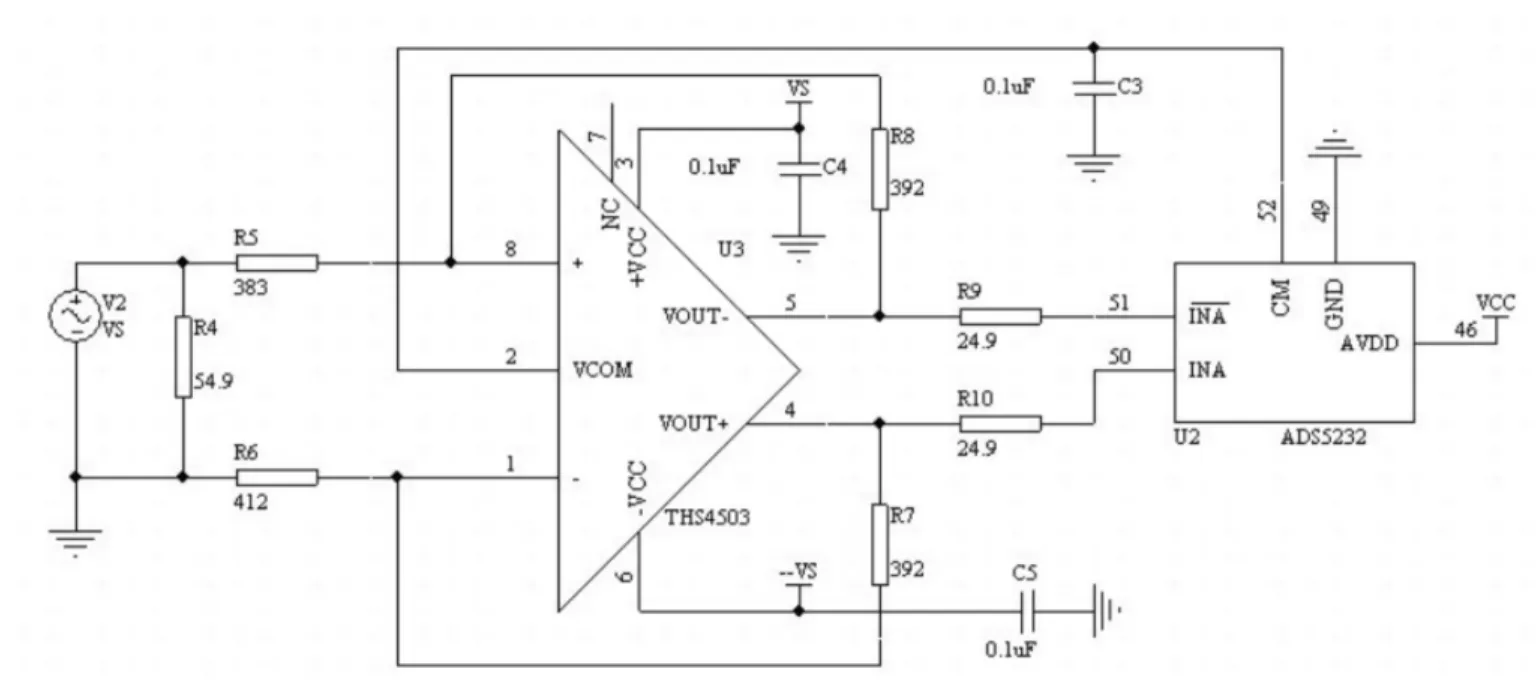

ADC前端电路可以使用放大器或者变压器来实现,二者都可以把单端信号转化为差分信号,并符合ADS5232对模拟输入的要求(ADS5232只接受差分模拟信号的输入).使用变压器的设计如图2所示,变压器的匝数比N可根据实际情况进行配置,使输出电压符合INA+和INA-的电压要求.使用放大器THS4503也可以实现ADC前端电路,其设计如图3所示,其中,THS4503的电压可以使用+5V和-5V.根据实际情况选择使用变压器或者放大器来实现 ADC 前端电路[1,3,4].一般而言,变压器不会引入噪音,而放大器会产生噪音.但如果要保留直流成分,则不能使用变压器,只能使用放大器了.

图2 使用变压器构成的ADC前端电路Fig.2 ADC front-end circuit constructed by transformer

图3 使用放大器构成的ADC前端电路Fig.3 ADC front-end circuit constructed by amplifier

2.2 ADS5232及其控制和接口电路的设计

ADS5232的输入和前端电路相连,输出和FPGA相连,如图4所示.2个通道同步采样,图4只给出了一个通道的情况.

(1)FPGA实现的功能.虚线框代表FPGA,使用内部的双口RAM作为数据缓冲区,可供片外应用电路读取.控制和接口模块完成ADS5232的接口控制,产生双口 RAM的写地址 WADDR,写使能WEN,对ADS5232的输出进行采样并按地址写入双口RAM中.片内锁相环对外部晶振输入的时钟进行倍频和相位调整,产生满足ADS5232需要的采样时钟CLK、双口RAM的写时钟CLK和读时钟CLK0以及其他模块需要的时钟,读时钟应该等于或者大于CLK.晶振的输出时钟是单端信号,考虑到锁相环需要输出高频时钟,所以要选用抖动小的晶振.数据处理及接口模块完成对采样数据的处理以及对外部应用电路的接口控制,例如,产生双口RAM的读地址,读使能.此外,还可以在FPGA内部单独新建其他模块实现应用电路所需的附加功能.FPGA可选择 ALTERA公司 Cyclone II系列的EP2C8Q208C8,它有182个 I/O引脚,8256个 LE,20.25KB 的内部 RAM,2 个锁相环 PLL[5].考虑到 2个通道同时采样,所以一个双口RAM的大小可以设置为5K×12bit比较合适.

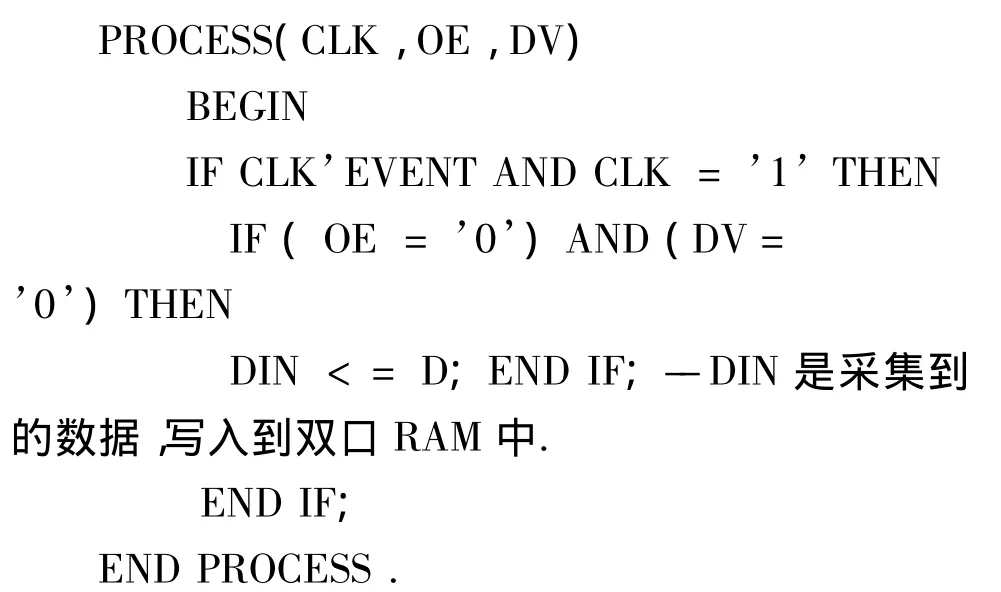

(2)ADS5232实现的功能.将差分模拟信号转化为数字信号D[11:0],同时产生数据有效指示信号DV、溢出指示OVR和输出使能OE.DV=0时,D[11:0]有效.DV=1 时,D[11:0]无效,表示数据更新期.根据数据手册提供的时序关系,应使用时钟CLK的上升沿对D[11:0]采样,采样的数据存入双口RAM中.其VHDL代码如下:

(3)控制信号的功能.除了上述DV、OVR、OE之外,其他信号的作用如下.

SEL:串口模式选择,SEL=1时,串口模式有效.串口模式是通过串口对内部寄存器进行设置,从而控制ADC的工作方式,需要设置串口通信.如果系统有CPU,则使用这种模式比较方便,但是在刚上电后需要产生一个SEL为0的低脉冲,以便对片内的寄存器复位,否则寄存器的值就不确定,复位是使之等于缺省值.当SEL=0时,禁止串口模式,此时串口关闭,串口引脚成为设置引脚,分别是OE、STPD、MSBI,这种模式属于硬件配置模式.图4所示的就是这种模式.非串口模式设置非常方便,是经常采用的一种模式.

STPD:省电模式控制,为1时省电工作模式,为0时正常工作模式.

图4 FPGA实现的缓冲、控制和接口Fig.4 Buffer,control and interface realized by FPGA

MSBI:输出数据D[11:0]的编码方式控制.为0时是SOB编码,为1时是BTC编码.这2种编码只是符号位的规定不同.对BTC编码,符号位为0表示正数,为1表示负数.SOB编码刚好相反.INT:参考电压选择控制,为0是使用外部参考电压,为1时使用内部参考电压.使用内部产生的参考电压时省去了外部参考电压设计,可以减小PCB的面积,图4就是使用内部参考电压的一种设计,可参考数据手册中的 Figure 21[1].

WADDR:双口RAM的写地址,由控制模块产生,初值设置为0,每当时钟CLK的下降沿到来时自动加1.当加到最大地址时自动回到0.需要注意的是,双口RAM的写地址和读地址不能同时相等,否则就会出现错误.

WEN:写使能,其为1时可以向双口RAM写入数据,其为0时不能写入.根据缓冲区是否写满、数据是否读完和采集的触发条件是否满足等来定义WEN的逻辑值.

3 结语

使用FPGA来实现高速ADC的控制以及与应用电路的接口是一种理想而实用的方案,本设计中使用的高速ADC芯片是ADS5232,其采样速率最高为65MS/s,精度12bit,双通道同步采样,差分模拟输入.FPGA不仅能实现高速控制、高速缓冲和高速接口,还可以扩展其他功能,例如,将2个采样通道对同一个模拟信号进行交叉采样,采样时钟相位差180°时,可以将采样速率提高到 2倍,即到达130MS/s.相位差为180°的时钟可以使用FPGA内部的锁相环实现.ADC前端电路根据具体情况可以适当修改,例如增加一定的信号调理电路,修改变压器的匝数比N等.本设计提供了一种高速数据采集的参考电路和设计方法,具有一定范围的实用性和普遍性,可以应用于高清数字视频采集、医学图像采集、测量仪表和通信基站等领域.

[1]Texas Instruments Inc.ADS5232 data sheet[EB/OL].(2006-03)[2010-05].http://www.ti.com/.

[2]程耀林,李享元,何湘竹.用于虚拟仪器的USB2.0接口高速数据采集卡的设计[J].计算机测量与控制,2011,19(5):1220-1222,1256.

[3]Texas Instruments Inc.ADS5232 EVM user’s guide[EB/OL].(2007-06)[2012-05].http://www.ti.com/.

[4]Texas Instruments Inc.THS4503 data sheet[EB/OL].(2002-03)[2012-10].http://www.ti.com/.

[5]Altera Corporation.Cyclone II Device Handbook,Volume1[EB/OL].(2005-03)[2010-07].http://www.altera.com.cn/.