基于FPGA的幅频数字均衡器设计

2012-11-21刘虹

刘 虹

(厦门理工学院电子与电气工程系,福建 厦门 361024)

基于FPGA的幅频数字均衡器设计

刘 虹

(厦门理工学院电子与电气工程系,福建 厦门 361024)

设计了一款以ALTERA公司Cyclone系列FPGA(现场可编程门阵列)芯片为控制核心的幅频数字均衡器。原信号经过衰减后由高速A/D芯片TLC55401进行采集,而后送入由FPGA实现的IIR(无限脉冲响应)数字滤波器进行补偿,再经D/A芯片THS5651将补偿后的信号输出,经低通滤波后,得到的输出信号完全补偿了信道造成的5dB衰减,幅频均衡效果良好。

FPGA(现场可编程门阵列);IIR(无限脉冲响应);幅频均衡

一个通信系统不可能完全满足理想的波形传输无失真条件,因而出现串扰现象是不可避免的[1]。为了接收到比较理想的发送信号,必须对整个系统的传递函数进行矫正,以补偿整个系统的幅频和相频特性。幅频畸变是由幅频特性不理想造成的,如电话线传输特性引起的幅频畸变,在该畸变影响下,模拟信号将产生波形失真,数字信号将产生码间串扰(ISI),对此解决的方法是采用时域或频域均衡技术。下面,笔者针对音频信号在带阻网络信道中的衰减,在接收端添加线性补偿网络进行特性补偿,并采用IIR滤波器实现。

1 方案论证

1.1核心器件选择

设计一款数字滤波器来实现数字均衡,其核心算法既可选择在FPGA(现场可编程门阵列)芯片上实现,也可选择在DSP(数字信号处理)芯片上实现。DSP有专用的乘法器和针对FFT(快速傅里叶变换)算法的位倒叙寻址方式等,这些专门设计使得数据处理更加方便和快速。但DSP实现数字滤波器需要较复杂的外围电路,而采用FPGA芯片时,可以通过DSP Builder并结合Matlab强大的滤波器设计功能来设计数字滤波器,该数字滤波器具有硬件执行速度快的特点。所以,进行方案设计时选择ALTERA公司EP2C5T144C8N型FPGA为核心控制器件。

1.2数字均衡实现方案确定

均衡可以在时域或者频域实现,在频域实现均衡时,首先将输入信号进行FFT(傅里叶)变换,然后根据补偿要求直接对信号的频谱进行缩放处理。由于处理的音频信号频率在中低频附近,如果采用频域均衡,对频率的分辨率要求很高,这使系统实现的复杂程度提高。而时域均衡主要采用数字滤波器实现,这使得系统实现复杂程度降低。数字滤波器包括选择FIR(有限长单位冲激响应)滤波器或者IIR(无限脉冲响应)滤波器,其中FIR滤波器虽然实现比较简单且工作稳定,但要达到均衡目的需较高的阶数,且硬件复杂度很高,而采用IIR滤波器时可以用较低的阶数达到均衡目的。因此,采用IIR数字滤波器实现幅频均衡。

2 系统设计

2.1总体结构

以正弦信号为测试信号,该信号通过信道时引起幅频畸变,该畸变信号经过A/D转换后由数字均衡器进行幅频均衡处理,再经D/A转换后由低通滤波器输出最终模拟信号。系统总体实现框图如图1所示。

图1 系统实现框图

2.2数字均衡器

图2 信道幅频特性曲线图

信号经过信道传输受到干扰时会引起信号畸变,因而必须对整个系统的传递函数进行校正,使接收到的信号与所发信号之间的误差在能够接受的范围内。由于采用串接一个滤波器的方式可以补偿整个系统的幅频特性,因而称该滤波器为数字均衡器[2]。设计均衡器时必须以信道的幅频特性为基础。通过实际测试,该设计中所要补偿的信道幅频特性如图2所示。

由图2可知,该信道属于带阻网络,其阻带频率下限为84Hz,阻带频率上限为4.4kHz,截止频率下限为33Hz,截止频率上限为10kHz。为了补偿该信道的幅频损失,数字均衡器应采用带通滤波器实现,其幅频特性应与带阻网络相反。经调试,所设计的数字滤波器的相关参数如表1所示。

表1 数字滤波器设计参数

由此得出该IIR滤波器的传递函数为:

式中,H(jw)为传递函数,jw为复频率,Hz;Z为Z域自变量。

根据上述传递函数并利用Matlab建立滤波器仿真模型,该仿真模型包括直接Ⅱ型与级联型2种类型[3]。

利用DSP Builder分别将以上2种滤波器模型转化为VHDL文件,嵌入FPGA中进行调试,FPGA的算法实现框图如图3所示。

图3 FPGA算法实现框图

经硬件测试,发现直接Ⅱ型IIR滤波器对低频信号的滤波效果不理想,出现了输出信号失真的现象(见图4)。在输入信号相同的情况下,采用级联型IIR滤波器能收到较好的滤波效果,没有出现输出信号失真的现象(见图5)。因此,设计时采用级联型IIR滤波器模型。

图4 直接Ⅱ型IIR滤波器输出信号 图5 级联型IIR滤波器输出信号

2.3低通滤波器

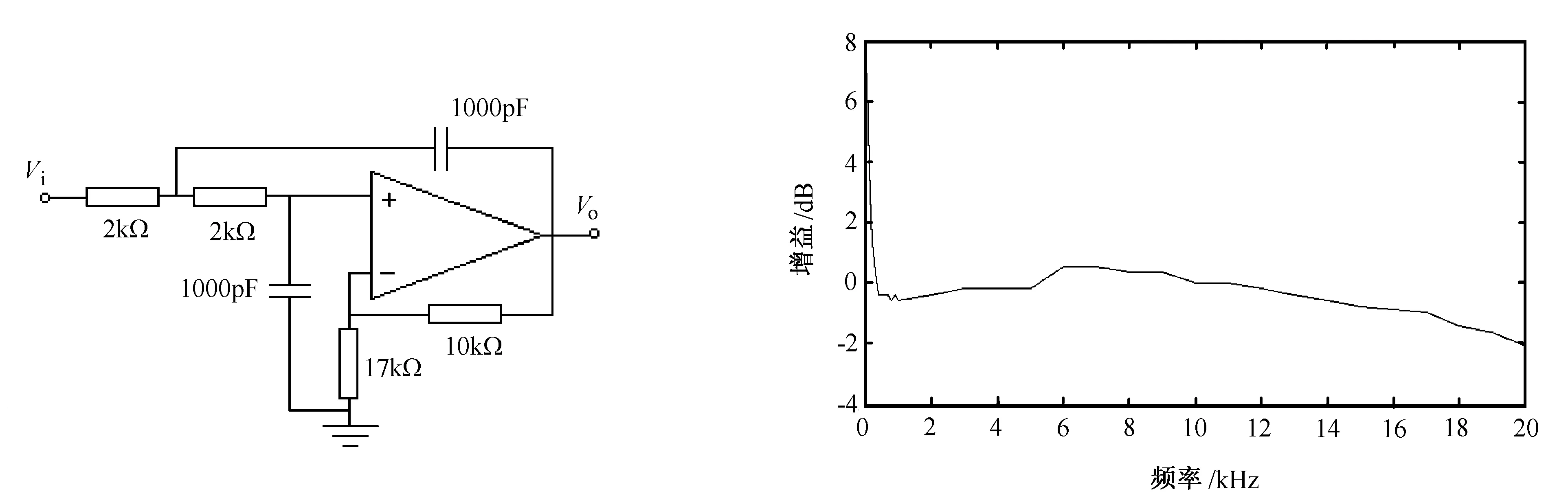

为了使D/A转换出来的波形不失真,在D/A输出端加上低通滤波器滤除高频波。低通滤波器电路图如图6所示。

2.4试验分析

为了测试幅频数字均衡器的硬件性能,输入多组不同频率的信号,得到最终输出信号频谱如图7所示。从图7可以看出,输出信号的增益曲线在10~20kHz范围内趋于直线,且增益变化不超过2dB,说明设计的数字均衡器能有效补偿由带阻网络所引起的信道损失,从而达到了幅频均衡的目的。

图6 低通滤波器电路图 图7 输出信号频谱图

3 结 语

利用Matlab强大的仿真功能,并结合DSP Builder对所设计的滤波器进行硬件描述语言的自动转换,可以避免在硬件上直接进行浮点设计的麻烦。试验分析表明,基于FPGA实现的数字滤波器能够实现良好的幅频均衡效果,说明上述设计方法是可行的。

[1]曹志刚,钱亚生.现代通信系统[M].清华大学出版社,2007.

[2]李建生,杜庆治.幅频畸变的均衡研究[A].北京:中国通信学会第五届学术年会论文集[C]. 2008:46-49.

[3]李彬.基于Matlab的IIR和FIR滤波器的滤波仿真教学体会[J].河北能源职业技术学院学报,2009,9(1):68-70.

10.3969/j.issn.1673-1409(N).2012.07.043

TN911.72

A

1673-1409(2012)07-N127-03

2012-04-13

厦门市指导性项目基金资助项目(3502Z20099009)。

刘虹(1978-),女,2001大学毕业,硕士,讲师,现主要从事数字信号与信息处理及芯片应用设计方面的教学与研究工作。

[编辑] 李启栋